Изобретение относится к области вычислительной техники и может быть использовано в многоканальных отказоустойчивых системах на базе конфигурируемых процессоров.

Известна резервированная вычислительная система (А.с. 1753479 А1 СССР МКИ G06F 15/16, 11/18), содержащая каналы вычислений, мажоритарные элементы, регистратор кода задачи, регистр кода решений, блок задания альтернатив, триггер инициализации, триггер зависания, счетчик времени, счетчик зацикливания, элемент задержки, элемент И, элемент ИЛИ, входы синхронизации, вход кода задачи, вход сброса, информационные входы, выход данных, выход останова.

Недостатком данной системы является низкая надежность, обусловленная невозможностью сохранения работоспособности при отказе двух каналов вычислений.

Наиболее близким предлагаемой по технической сущности и достигаемому эффекту является система (пат. РФ №146542), содержащая первый-третий конфигурируемые процессоры, в кристаллах которых синтезированы первый и второй внутренние каналы обработки информации, схема сравнения и коммутатор (полученные путем описания логики работы конфигурируемого процессора на одном из языков описания аппаратуры JHDL, AHDL, VHDL или Verilog), первый - третий мажоритарные элементы, конфигурационное ПЗУ, устройство загрузки конфигурации, первый - третий входы загрузки конфигурации, вход данных, первый - третий выходы данных.

Недостатком прототипа является низкая надежность функционирования, которая обусловлена следующими причинами.

В прототипе система признается полностью отказавшей, если у нее вышло из строя по одному внутреннему каналу обработки информации в двух конфигурируемых процессорах или три мажоритарных элемента. Тем не менее второй внутренний канал обработки информации может исправно функционировать.

Целью изобретения является повышение надежности вычислительной системы на конфигурируемых процессорах путем сохранения работоспособности при наличии двух исправных внутренних каналов обработки информации.

Поставленная цель достигается путем исключения из прототипа трех асинхронных мажоритарных элементов и дополнительного введения в прототип семи синхронных мажоритарных элементов, пяти элементов И, элемента И-НЕ, элемента ИЛИ, генератора тактовых импульсов, инверсного выхода схем сравнения и четырех выходов данных.

Сущность изобретения состоит в повышении надежности вычислительной системы на конфигурируемых процессорах путем сохранения работоспособности при наличии двух исправных внутренних каналов обработки информации за счет межканального мажоритирования информации.

В процессе функционирования системы данные обрабатываются внутренними каналами обработки информация, которые программно синтезированы в кристаллах конфигурируемых процессоров, там же расположены схемы сравнения, которые осуществляют контроль правильности функционирования внутренних каналов обработки информации, и в зависимости от результатов контроля, формируют управляющие сигналы на коммутаторы, также синтезированные в кристаллах конфигурируемых процессоров.

Обработанные данные из исправных каналов обработки информации поступают через коммутаторы на входы первой группы синхронных мажоритарных элементов и далее на выходы устройства.

Если в кристаллах каждого конфигурируемого процессора осталось исправно по одному каналу обработки информации или количество исправных каналов обработки информации не превышает трех, то по управляющим сигналам, формируемым генератором тактовых импульсов совместно с пятью элементами И, элементом И-НЕ и элементом ИЛИ, обработанные данные из исправных каналов обработки информации через входы второй группы синхронных мажоритарных элементов поступают на выходы устройства.

Введение семи синхронных мажоритарных элементов и обусловленные ими связи позволяют передавать данные из внутренних каналов обработки информации на выходы данных даже тогда, когда только два внутренних канала обработки информации исправны.

Введение генератора тактовых импульсов и обусловленные им связи позволяют формировать сигналы для управления синхронными мажоритарными элементами.

Введение первого - четвертого элементов И и обусловленные им связи позволяют формировать единичные сигналы на соответствующие входы элемента ИЛИ.

Введение пятого элемента И и обусловленные им связи позволяют управлять функционированием четвертого - седьмого синхронных мажоритарных элементов и элементом И-НЕ.

Введение элемента И-НЕ и обусловленные им связи позволяют формировать импульсный сигнал на входы синхронизации первого - третьего синхронных мажоритарных элементов.

Введение элемента ИЛИ и обусловленные им связи позволяют формировать единичный сигнал на втором входе пятого элемента И, если количество.

Введение инверсного выхода схем сравнения и обусловленные им связи позволяют формировать сигналы, управляющие элементом И.

Введение четырех выходов данных позволяет передавать потребителям обработанную информацию, когда количество исправных внутренних каналов обработки информации не превышает трех.

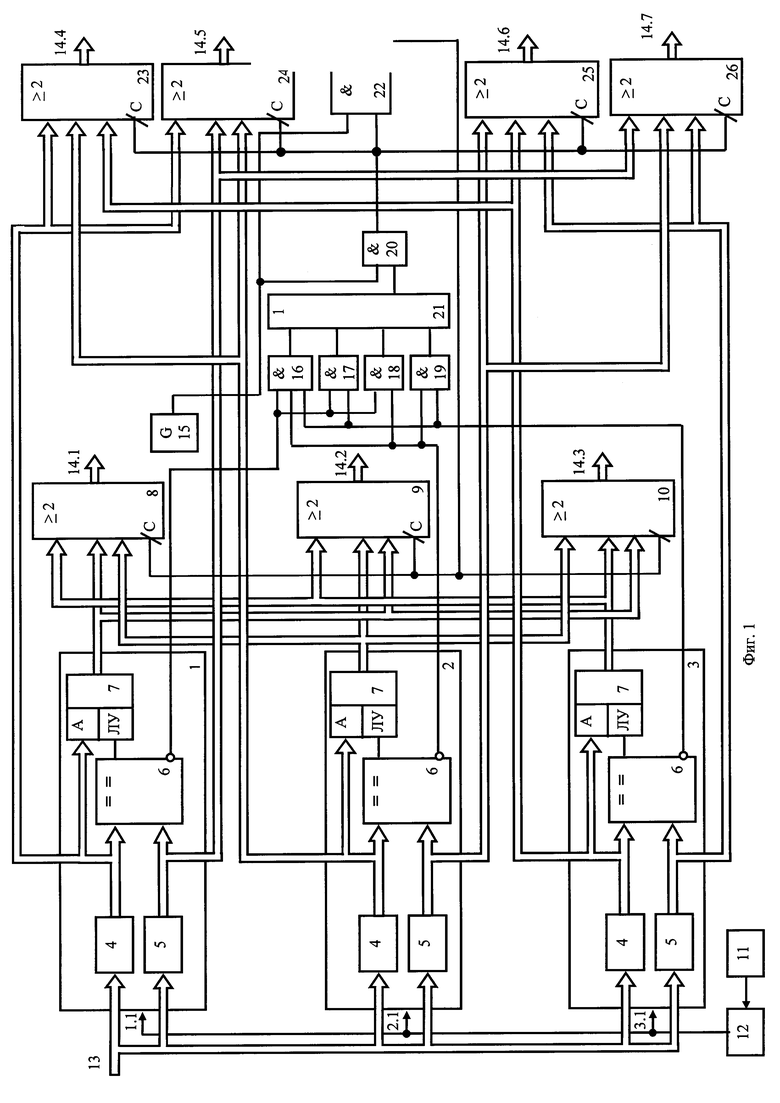

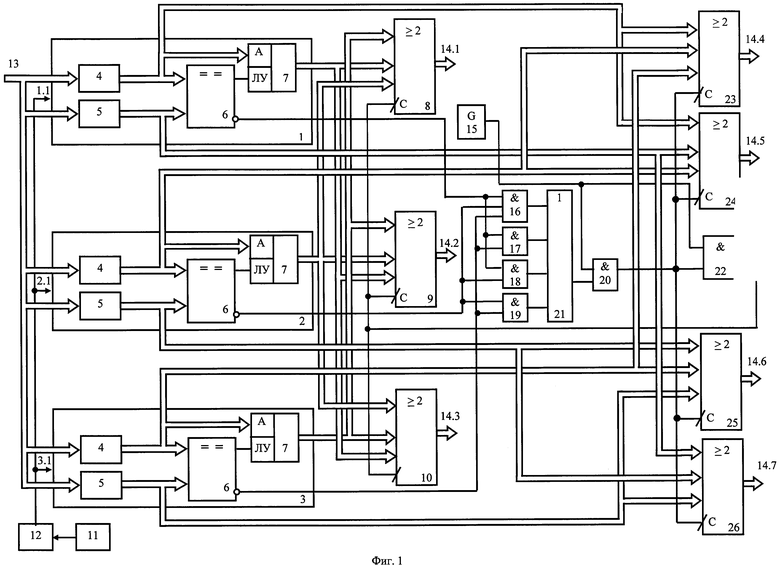

Вычислительная система с внекристальным мажоритированием и внутрикристальным дублированием содержит (фиг. 1): три конфигурируемых процессора 1-3, в кристаллах которых синтезированы первый 4 и второй 5 внутренние каналы обработки информации, схема сравнения 6, коммутатор 7 (получены путем описания логики работы конфигурируемого процессора на одном из языков описания аппаратуры JHDL, AHDL, VHDL или Verilog), первый 8 - третий 10 (составляют первую группу) и четвертый 23 - седьмой 26 (составляют вторую группу) синхронные мажоритарные элементы, генератор тактовых импульсов 15, первый 16 - пятый 20 элементы И, элемент И-НЕ 22, элемент ИЛИ 21, конфигурационное ПЗУ 11, устройство загрузки конфигурации 12, первый 1.1 - третий 3.1 входы загрузки конфигурации, вход данных 13, первый 14.1 - седьмой 14.7 выходы данных.

Назначение основных функциональных узлов предлагаемой вычислительной системы состоит в следующем.

Первый 1 - третий 3 конфигурируемые процессоры осуществляют обработку данных по алгоритму, реализованному во внутренних каналах обработки информации и контролируют правильность их функционирования.

Первый 4 и второй 5 внутренние каналы обработки информации предназначены для обработки данных по соответствующему алгоритму.

Схема сравнения 6 осуществляет поразрядное сравнение результатов обработки данных внутренними каналами обработки информации 4, 5 между собой и формирует управляющие воздействия на вход логических условий ЛУ коммутатора 7.

Коммутатор 7 предназначен для передачи результатов обработки данных с выходов первого 4 внутреннего канала обработки информации первого 1 - третьего 3 конфигурируемых процессоров на входы, первого 8 - третьего 10 синхронных мажоритарных элементов при наличии единичного сигнала на входе логических условий ЛУ, в противном случае, осуществляется запрет передачи данных на выход соответствующего конфигурируемого процессора.

Первый 8 - третий 10 (первая группа) синхронные мажоритарные элементы осуществляют выборку данных поступающих от конфигурируемых процессоров по схеме 2/3 и передают на выходы системы данные, соответствующие большинству из входных. Для реализации данной операции входы первой группы синхронных мажоритарных элементов соединены следующим образом: выход коммутатора 7 первого конфигурируемого процессора 1 соединен со вторым входом первого 8 мажоритарного элемента, третьим входом второго 9 мажоритарного элемента и третьим входом третьего 10 мажоритарного элемента; выход коммутатора 7 второго конфигурируемого процессора 2 соединен с третьим входом первого 8 мажоритарного элемента, вторым входом второго 9 мажоритарного элемента и первым входом третьего 10 мажоритарного элемента; выход коммутатора 7 третьего конфигурируемого процессора 3 соединен с первым входом первого 8 мажоритарного элемента, первым входом второго 9 мажоритарного элемента и вторым входом третьего 10 мажоритарного элемента.

Четвертый 23 - седьмой 26 (вторая группа) синхронные мажоритарные элементы осуществляют выборку данных поступающих от внутренних каналов обработки информации первого 1 - третьего 3 конфигурируемых процессоров по схеме 2/3 и передают на выходы системы, данные соответствующие большинству из входных. Для реализации данной операции входы второй группы синхронных мажоритарных элементов соединены следующим образом: выход первого внутреннего канала обработки информации 4 первого конфигурируемого процессора 1 соединен с первым входом четвертого 24 и первым входом пятого 25 синхронных мажоритарных элементов, выход второго внутреннего канала обработки информации 5 первого конфигурируемого процессора 1 соединен с вторым входом пятого 25 и первым входом седьмого 26 синхронных мажоритарных элементов, выход первого внутреннего канала обработки информации 4 второго конфигурируемого процессора 2 соединен с вторым входом четвертого 18 и третьим входом пятого 24 синхронных мажоритарных элементов, выход второго внутреннего канала обработки информации 5 второго конфигурируемого процессора 2 соединен с первым входом шестого 25 и вторым входом седьмого 26 синхронных мажоритарных элементов, выход первого внутреннего канала обработки информации 4 третьего конфигурируемого процессора 3 соединен с вторым входом шестого 25 и третьим входом четвертого 23 синхронных мажоритарных элементов, выход второго внутреннего канала обработки информации 5 третьего конфигурируемого процессора 3 соединен с третьим входом седьмого 26 и третьим входом шестого 25 синхронных мажоритарных элементов.

Генератор тактовых импульсов 15 осуществляет формирование импульса на первые входы пятого элемента И 16 и элемента И-НЕ 22.

Первый элемент И 16 формирует единичный сигнал на выходе, если данные с инверсных выходов схем сравнения 6 первого 1 - третьего 3 конфигурируемых процессоров установлен сигнал высокого уровня сигнализирующий о несовпадении информации в соответствующих внутренних каналах обработки информации.

Второй элемент И 17 формирует единичный сигнал на выходе, если данные с инверсных выходов схем сравнения 6 первого 1 и третьего 3 конфигурируемых процессоров установлен сигнал высокого уровня сигнализирующий о несовпадении информации в соответствующих внутренних каналах обработки информации.

Третий элемент И 18 формирует единичный сигнал на выходе, если данные с инверсных выходов схем сравнения 6 первого 1 и второго 2 конфигурируемых процессоров установлен сигнал высокого уровня сигнализирующий о несовпадении информации в соответствующих внутренних каналах обработки информации.

Четвертый элемент И 19 формирует единичный сигнал на выходе, если данные с инверсных выходов схем сравнения 6 второго 2 и третьего 3 конфигурируемых процессоров установлен сигнал высокого уровня сигнализирующий о несовпадении информации в соответствующих внутренних каналах обработки информации.

Пятый элемент И 20 предназначен для управления работой элемента И-НЕ 22 и передачи тактовых импульсов на входы синхронизации четвертого 23 - седьмого 26 (вторая группа) синхронных мажоритарных элементов, в зависимости от сигнала с выхода элемента ИЛИ 21.

Элемент И-НЕ 22 предназначен для передачи тактовых импульсов на входы синхронизации первого 8 - третьего 10 (первая группа) синхронных мажоритарных элементов, в зависимости от сигнала на выходе пятого элемента И 20.

Элемент ИЛИ 21 формирует на выходе сигнал высокого уровня при наличии единичного сигнала на выходе хотя бы одного из первого 16 - четвертого 19 элементов И.

Конфигурационное ПЗУ 11 служит для хранения файлов конфигурации, которые загружаются в кристаллы конфигурируемых процессоров и формируют их внутреннюю структуру.

Устройство загрузки конфигурации 12 осуществляет загрузку конфигурационного файла в первый 1 - третий 3 конфигурируемые процессоры.

Первый 1.1 - третий 3.1 входы загрузки конфигурации предназначены для загрузки конфигурационного файла из конфигурационного ПЗУ 11 в кристаллы первого 1 - третьего 3 конфигурируемых процессоров.

Вход данных 13 предназначен для подачи данных на первый 1 - третий 3 конфигурируемые процессоры.

Первый 14.1 - седьмой 14.7 выходы данных предназначены для передачи обработанной информации потребителям.

Вычислительная система с внекристальным мажоритированием и внутрикристальным дублированием функционирует следующим образом.

В исходном состоянии на входах логического условия ЛУ коммутатора 7 первого 1 - третьего 3 конфигурируемых процессоров единичный сигнал, который разрешает прохождение данных с выходов первого 4 внутреннего канала обработки информации соответствующих конфигурируемых процессоров на входы первого 8 - третьего 10 синхронных мажоритарных элементов.

На инверсных выходах схем сравнения 6 первого 1 - третьего 3 конфигурируемых процессоров сигналы низкого уровня, которые устанавливают на выходах первого 16 - четвертого 19 элементов И, а следовательно, на выходе элемента ИЛИ 21 нулевые сигналы, что запрещает прохождение импульсов синхронизации с генератора тактовых импульсов 15 через пятый 20 элемент И на входы синхронизации четвертого 23 - седьмого 26 синхронных мажоритарных элементов. Это не позволяет данным внутренних каналов обработки первого 1 - третьего 3 конфигурируемых процессоров поступать на четвертый 14.4 - седьмой 14.7 выходы данных.

Сигнал низкого уровня на втором входе элемента И-НЕ 22 открывает его и разрешает прохождение импульсов с генератора тактовых импульсов 15, подключенного к первому входу элемента И-НЕ 22, на входы синхронизации первого 8 - третьего 10 синхронных мажоритарных элементов. В этом случае данные с выходов первого 4 внутреннего канала обработки информации первого 1 - третьего 3 конфигурируемых процессоров через первый 8 - третий 10 синхронные мажоритарные элементы поступят на первый 14.1 - третий 14.3 выходы данных соответственно.

При включении питания файлы конфигурации, которые получены путем описания логики функционирования конфигурируемого процессора на одном из языков описания аппаратуры JHDL, AHDL, VHDL или Verilog поступают с выхода ПЗУ конфигурации 11 на вход устройства загрузки конфигурации 12, которое осуществляет их загрузку через первый 1.1 - третий 3.1 входы загрузки конфигурации в первый 1 - третий 3 конфигурируемые процессоры соответственно. Загрузка конфигурационного файла осуществляется так, что в каждом кристалле первого 1 - третьего 3 конфигурируемых процессоров размещаются по два одинаковых внутренних канала обработки информации 4, 5, по одной схеме сравнения 6 и по одному коммутатору 7.

Информация с входа данных 13 одновременно поступает во внутренние каналы обработки информации 4, 5 первого 1 - третьего 3 конфигурируемых процессоров. Результаты обработки синхронно появляются на выходах внутренних каналов обработки информации 4, 5, а, следовательно, и на входах схемы сравнения 6 конфигурируемых процессоров 1-3. Цепи синхронизации на фиг. 1 условно не показаны.

Кроме того, данные с выхода первого внутреннего канала обработки информации 4 поступают на вход А коммутатора 7 первого 1 - третьего 3 конфигурируемых процессоров и на входы четвертого 23 - седьмого 26 синхронных мажоритарных элементов.

Если, результаты обработки данных во внутренних каналах обработки информации 4 и 5 совпадут, то на прямом выходе схемы сравнения 6 соответствующего конфигурируемого процессора появится единичный сигнал, который, поступив на вход логических условий ЛУ коммутатора 7, разрешит прохождение данных на выход конфигурируемого процессора, а, следовательно, и на входы первого 8 - третьего 10 синхронных мажоритарных элементов.

В свою очередь, сигнал низкого уровня на инверсных выходах схемы сравнения 6 первого 1 - третьего 3 конфигурируемых процессоров инициируют установку нулевых сигналов на выходах первого 16 - четвертого 19 элементов И и на выходе элемента ИЛИ 21 тем самым, пятый 20 элемент И будет закрыт, что запретит прохождение импульсов с выхода генератора тактовых импульсов 15 на входы синхронизации четвертого 23 - седьмого 26 синхронных мажоритарных элементов. При этом прохождение данных с выходов внутренних каналов обработки информации первого 1 - третьего 3 конфигурируемых процессоров на четвертый 14.4 - седьмой 14.7 выходы данных станет невозможным. Сигнал низкого уровня на выходе пятого элемента И 20, поданный на второй вход элемента И-НЕ 22 разрешит прохождение импульсов с генератора тактовых импульсов 15, который подключен к первому входу элемента И-НЕ 22, на его инверсный выход и далее на входы синхронизации первого 8 - третьего 10 синхронных мажоритарных элементов.

Первый 8 - третий 10 синхронные мажоритарные элементы по сигналам на входах синхронизации, осуществляют поразрядное сравнение информации, полученной с выходов первого 1 - третьего 3 конфигурируемых процессоров. При этом на выходы мажоритарных элементов, а, следовательно, и на выходы данных 14.1 - 14.3 пройдут те данные, которые зафиксированы на выходах двух из трех процессоров.

В случае различия данных во внутренних каналах обработки 4, 5 на прямом выходе схемы сравнения 6 установится нулевой сигнал, который заблокирует коммутатор 7 соответствующего конфигурируемого процессора и на соответствующих входах первого 8 - третьего 10 мажоритарных элементов установится логический нуль. В свою очередь на инверсном выходе схемы сравнения 6 конфигурируемого процессора, в котором имеет место несовпадение данных, установится единичный сигнал.

В этом случае возможны два варианта работы системы:

1) первый вариант характеризует работу системы, когда исправно минимум два конфигурируемых процессора;

2) второй вариант характеризует работу системы, когда минимум две схемы сравнения в конфигурируемых процессорах просигнализировали о несовпадении данных во внутренних каналах обработки информации.

Рассмотрим работу системы для первого варианта.

Предположим, что отказал второй внутренний канал обработки информации 5 первого конфигурируемого процессора 1.

В этом случае на прямом выходе схемы сравнения 6 первого конфигурируемого процессора 1 появится нулевой сигнал, который поступив на вход логических условий ЛУ коммутатора 7 запретит прохождение данных с выхода первого внутреннего канала обработки информации 4 через вход А коммутатора 7 на выход первого 1 конфигурируемого процессора. В результате чего, на втором входе первого 8 мажоритарного элемента, третьем входе второго 9 мажоритарного элемента и третьем входе третьего 10 мажоритарного элемента установится нулевой сигнал, на остальных входах первого 8 - третьего 10 мажоритарных элементов установятся данные, поступившие с выходов второго 2 и третьего 3 конфигурируемых процессоров.

Далее мажоритарные элементы осуществляют выборку поступившей информации по схеме 2/3 и передают на первый 14.1 - третий 14.3 выходы данных те данные, которые соответствуют большинству из входных.

В тоже время на инверсном выходе схемы сравнения 6 первого конфигурируемого процессора 1 появится единичный сигнал, который поступит на первый вход первого 16 элемента И, первый вход второго 17 элемента И и первый вход третьего 18 элемента И. На остальные входы первого 16 - четвертого 19 элементов И поступят сигналы низкого уровня с инверсных выходов схемы сравнения 6 второго 2 - третьего конфигурируемых процессоров. В этом случае на выходах первого 16 - четвертого 19 элементов И, выходе элементы ИЛИ 21 и выходе пятого элемента И 20 установится нулевой сигнал, что запретит прохождение импульсов с генератора тактовых импульсов 15 на входы синхронизации четвертого 23 - седьмого 26 синхронных мажоритарных элементов и данные на четвертый 14.4 - седьмой 14.7 не поступят.

В случае отказа одного из мажоритарных элементов система продолжает функционировать как описано выше, но на выходе данных, который соединен с выходом отказавшего мажоритарного элемента установится нулевой сигнал и потребитель будет получать информацию с выходов данных соединенных с исправными мажоритарными элементами.

Для первого варианта функционирования остальные конфигурируемые процессоры в случае возникновения неисправности внутренних каналов обработки информации функционируют аналогично.

Рассмотрим работу системы для второго варианта.

Предположим, что отказали первый 4 внутренний канал обработки информации первого 1 конфигурируемого процессора, второй 5 канал обработки информации второго 2 конфигурируемого процессора, первый 4 и второй 5 внутренние каналы обработки информации третьего 3 конфигурируемого процессора.

В этом случае на прямых выходах схем сравнения 6 первого 1 - третьего 3 конфигурируемых процессоров установится нулевой сигнал, который поступит на входы логических условий коммутаторов 7 и запретит прохождение данных через первый 8 - третий 10 синхронные мажоритарные элементы на первый 14.1 - третий 14.3 выходы данных.

Одновременно на инверсных выходах схем сравнения 6 первого 1 - третьего 3 конфигурируемых процессоров установится единичный сигнал. Этот сигнал установит на выходах первого 16 - четвертого 19 элементов И сигнал высокого уровня, следовательно на выходе элемента ИЛИ 21 установится единичный сигнал, который, поступив на второй вход пятого 20 элемента И разрешит прохождение импульсов с генератора тактовых импульсов 15 на входы синхронизации четвертого 23 - седьмого 26 синхронных мажоритарных элементов и поступив на второй вход элемента И-НЕ 22 запретит прохождение импульсов с генератора тактовых импульсов 15 на входы синхронизации первого 8 - третьего 10 синхронных мажоритарных элементов.

Импульсы на входах синхронизации четвертого 23 - седьмого 26 синхронных мажоритарных элементов разрешат осуществление выборки данных поступивших с внутренних каналов обработки информации 4, 5 первого 1 - третьего 3 конфигурируемых процессоров по схеме 2/3 и передают на четвертый 14.4 - седьмой 14.7 выходы данных те данные, которые соответствуют большинству из входных.

В остальных аналогичных случаях, когда минимум две схемы сравнения в конфигурируемых процессорах просигнализировали о несовпадении данных во внутренних каналах обработки информации система функционирует аналогичным образом.

Система признается полностью отказавшей, если у нее остался исправным один внутренний канал обработки информации в любом конфигурируемом процессоре.

Таким образом, разработанная система позволяет существенно повысить надежность вычислительной системы путем сохранения работоспособности при наличии двух исправных внутренних каналов обработки информации за счет межканального мажоритирования информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Устройство для двунаправленной передачи информации | 1991 |

|

SU1784987A1 |

| Мажоритарное устройство обработки аналоговой информации | 1988 |

|

SU1737775A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в повышении надежности вычислительной системы на конфигурируемых процессорах путем сохранения работоспособности при наличии двух исправных внутренних каналов обработки информации за счет межканального мажоритирования информации. Устройство содержит три конфигурируемых процессора, в кристаллах которых синтезированы по два внутренних канала обработки информации, по одной схеме сравнения и по одному коммутатору, вне кристаллов располагаются семь мажоритарных элементов, пять элементов И, один элемент И-НЕ, один элемент ИЛИ, генератор тактовых импульсов, конфигурационное ПЗУ, устройство загрузки конфигурации, три входа загрузки конфигурации, вход данных, семь выходов данных. 1 ил.

Вычислительная система с внекристальным мажоритированием и внутрикристальным дублированием, отличающаяся тем, что содержит три конфигурируемых процессора, в кристаллах которых синтезированы по два внутренних канала обработки информации, по одной схеме сравнения и по одному коммутатору, вне кристалла расположены семь мажоритарных элементов, пять элементов И, один элемент И-НЕ, один элемент ИЛИ, генератор тактовых импульсов, конфигурационное ПЗУ, устройство загрузки конфигурации, три входа загрузки конфигурации, вход данных, семь выходов данных, причем вход данных соединен с входами первого-второго внутренних каналов обработки информации первого-третьего конфигурируемых процессоров, выходы первого-второго внутреннего канала обработки информации первого конфигурируемого процессора соединены с первым-вторым входами схемы сравнения первого конфигурируемого процессора, кроме того, выход первого внутреннего канала обработки информации первого конфигурируемого процессора соединен с входом А коммутатора первого конфигурируемого процессора, с первым входом четвертого мажоритарного элемента и первым входом пятого мажоритарного элемента, в свою очередь, прямой выход схемы сравнения первого конфигурируемого процессора соединен с входом логических условий коммутатора первого конфигурируемого процессора, выход второго канала обработки информации первого конфигурируемого процессора соединен с вторым входом пятого мажоритарного элемента и первым входом седьмого мажоритарного элемента, инверсный выход схемы сравнения первого конфигурируемого процессора соединен с первым входом первого элемента И, первым входом второго элемента И и первым входом третьего элемента И, выходы первого-второго внутреннего канала обработки информации второго конфигурируемого процессора соединены с первым-вторым входами схемы сравнения второго конфигурируемого процессора, кроме того, выход первого внутреннего канала обработки информации второго конфигурируемого процессора соединен с входом А коммутатора второго конфигурируемого процессора, с вторым входом четвертого мажоритарного элемента и третьим входом пятого мажоритарного элемента, в свою очередь, прямой выход схемы сравнения второго конфигурируемого процессора соединен с входом логических условий коммутатора второго конфигурируемого процессора, выход второго канала обработки информации второго конфигурируемого процессора соединен с первым входом шестого мажоритарного элемента и вторым входом седьмого мажоритарного элемента, инверсный выход схемы сравнения второго конфигурируемого процессора соединен с вторым входом первого элемента И, вторым входом третьего элемента И и первым входом четвертого элемента И, выходы первого-второго внутреннего канала обработки информации третьего конфигурируемого процессора соединены с первым-вторым входами схемы сравнения третьего конфигурируемого процессора, кроме того, выход первого внутреннего канала обработки информации третьего конфигурируемого процессора соединен с входом А коммутатора третьего конфигурируемого

процессора, с третьим входом четвертого мажоритарного элемента и вторым входом шестого мажоритарного элемента, в свою очередь, прямой выход схемы сравнения третьего конфигурируемого процессора соединен с входом логических условий коммутатора третьего конфигурируемого процессора, выход второго канала обработки информации третьего конфигурируемого процессора соединен с третьим входом шестого мажоритарного элемента и третьим входом седьмого мажоритарного элемента, инверсный выход схемы сравнения третьего конфигурируемого процессора соединен с третьим входом первого элемента И, вторым входом второго элемента И и вторым входом четвертого элемента И, выход коммутатора первого конфигурируемого процессора соединен с вторым входом первого мажоритарного элемента, третьим входом второго мажоритарного элемента и третьим входом третьего мажоритарного элемента; выход коммутатора второго конфигурируемого процессора соединен с третьим входом первого мажоритарного элемента, вторым входом второго мажоритарного элемента и первым входом третьего мажоритарного элемента; выход коммутатора третьего конфигурируемого процессора соединен с первым входом первого мажоритарного элемента, первым входом второго мажоритарного элемента и вторым входом третьего мажоритарного элемента, выход первого элемента И соединен с первым входом элемента ИЛИ, выход второго элемента И соединен с вторым входом элемента ИЛИ, выход третьего элемента И соединен с третьим входом элемента ИЛИ, выход четверого элемента И соединен с четвертым входом элемента ИЛИ, выход элемента ИЛИ соединен с вторым входом пятого элемента И, выход генератора тактовых импульсов соединен с первым входом пятого элемента И и первым входом элемента И-НЕ, выход пятого элемента И соединен с вторым входом элемента И-НЕ и входами синхронизации четвертого-седьмого мажоритарных элементов, инверсный выход элемента И-НЕ соединен с входами синхронизации первого-третьего мажоритарных элементов, выход первого-седьмого мажоритарного элемента соединен с первым-седьмым выходом данных соответственно, выход ПЗУ конфигурации соединен с входом устройства загрузки конфигурации, выход устройства загрузки конфигурации соединен с первым-третьим входами загрузки конфигурации первого-третьего конфигурируемых процессоров соответственно.

| Устройство для определения коэффициента теплоотдачи | 1961 |

|

SU146542A1 |

| Устройство для испытания высоковольтных воздушных выключателей на коммутационную способность | 1960 |

|

SU133952A1 |

| Циркониево-карбидная масса для наконечников термопар погружения | 1960 |

|

SU148928A1 |

| Краскораспылитель | 1961 |

|

SU141775A1 |

Авторы

Даты

2018-11-12—Публикация

2016-07-11—Подача