Изобретение относится к области радиотехники и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих при низких температурах и воздействии проникающей радиации [21,22,23].

Все существующие сегодня варианты построений буферных и неинвертирующих усилителей (НУ) на основе КМОП, КНИ, КНС, JFet, BJT, SiGe и др. технологий можно разделить на два класса – схемы с низкоомным выходом [1-9] и схемы с высокоомным (токовым) выходом [10-20].

Особенность усилителей с высоокомным токовым выходом [10-20] состоит в том, что они обеспечиваю опцию rail-to-rail (изменение уровня выходного напряжения от шины положительного питания до шины отрицательного питания). Кроме этого, усилители данного класса применяются для создания высоимпедансных узлов, например, в схемах ОУ для обеспечения больших значений коэффициента усиления [28-29].

Анализ вариантов построения rail-to-rail НУ показал, что в настоящее время в рамках данного семейства устройств неизвестны CJFet схемотехнические решения.

Для работы при низких температурах, при жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов с управляющим p-n переходом [25]. Схемы данного класса активно применяются в структуре малошумящих аналоговых интерфейсов и в схемах обработки сигналов датчиков [24,26,27].

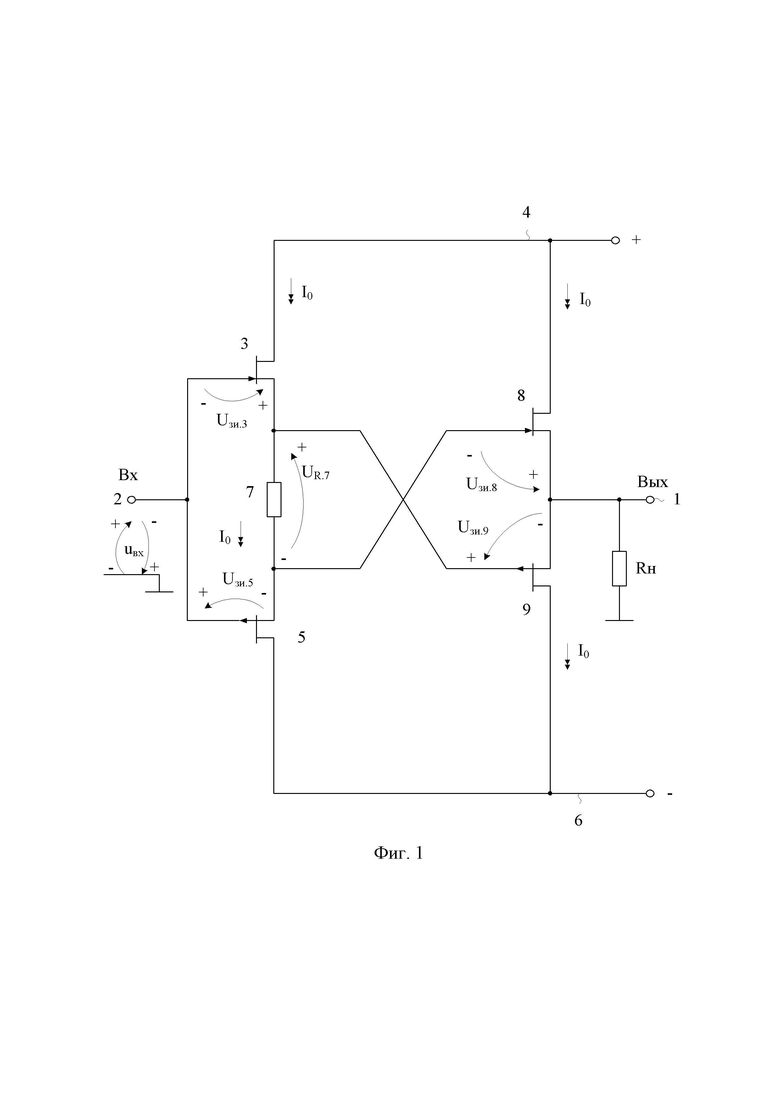

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад, описанный в патенте RU 2684489, фиг. 2, 2019 г., который содержит вход 2 устройства, первый 3 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан с первой 4 шиной источника питания, второй 5 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан со второй 6 шиной источника питания, токостабилизирующий двухполюсник 7, включенный между истоком первого 3 и истоком второго 5 входных полевых транзисторов, первый 8 выходной полевой транзистор, сток которого связан с первой 4 шиной источника питания, второй 9 выходной полевой транзистор, сток которого связан со второй 6 шиной источника питания.

Первый существенный недостаток НУ-прототипа состоит в том, что он не обеспечивает опцию rail-to-rail по выходу и имеет низкое выходное сопротивление. Последнее качество данного НУ затрудняет построение на его основе промежуточных каскадов аналоговых микросхем с высоким усилением.

Основная задача предполагаемого изобретения состоит в создании неинвертирующего CJFet усилителя, обеспечивающего опцию rail-to-rail по выходу и получение повышенных выходных сопротивлений. Последнее качество позволяет создавать высокоомные узлы в аналоговых устройствах и обеспечить их коррекцию амплитудно-частотных характеристик с помощью конденсаторов небольшой емкости [28].

Поставленные задачи достигаются тем, что в неинвертирующем усилителе фиг. 1, содержащем вход 2 устройства, первый 3 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан с первой 4 шиной источника питания, второй 5 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан со второй 6 шиной источника питания, токостабилизирующий двухполюсник 7, включенный между истоком первого 3 и истоком второго 5 входных полевых транзисторов, первый 8 выходной полевой транзистор, сток которого связан с первой 4 шиной источника питания, второй 9 выходной полевой транзистор, сток которого связан со второй 6 шиной источника питания, предусмотрены новые элементы и связи – в схему введена дифференциальная цепь смещения потенциалов 10, первый 11 вход которой соединен с истоком первого 3 входного полевого транзистора, второй вход 12 подключен к истоку второго 5 входного полевого транзистора, затвор первого 8 выходного полевого транзистора соединен с первым 13 выходом дифференциальной цепи смещения потенциалов 10, затвор второго 9 выходного полевого транзистора соединен со вторым 14 выходом дифференциальной цепи смещения потенциалов 10, исток первого 8 выходного полевого транзистора соединен с истоком первого 15 дополнительного выходного полевого транзистора, затвор которого связан с первой 4 шиной источника питания, а сток соединен с токовым выходом 1 устройства, исток второго 9 выходного полевого транзистора соединен с истоком второго 16 дополнительного выходного полевого транзистора, затвор которого связан со второй 6 шиной источника питания, а сток соединен с токовым выходом 1 устройства.

На чертеже фиг. 1 представлена схема неинвертирующего усилителя-прототипа, а на чертеже фиг. 2 – схема заявляемого НУ на комплементарных полевых транзисторах с управляющим p-n переходом в соответствии с п.1 формулы изобретения.

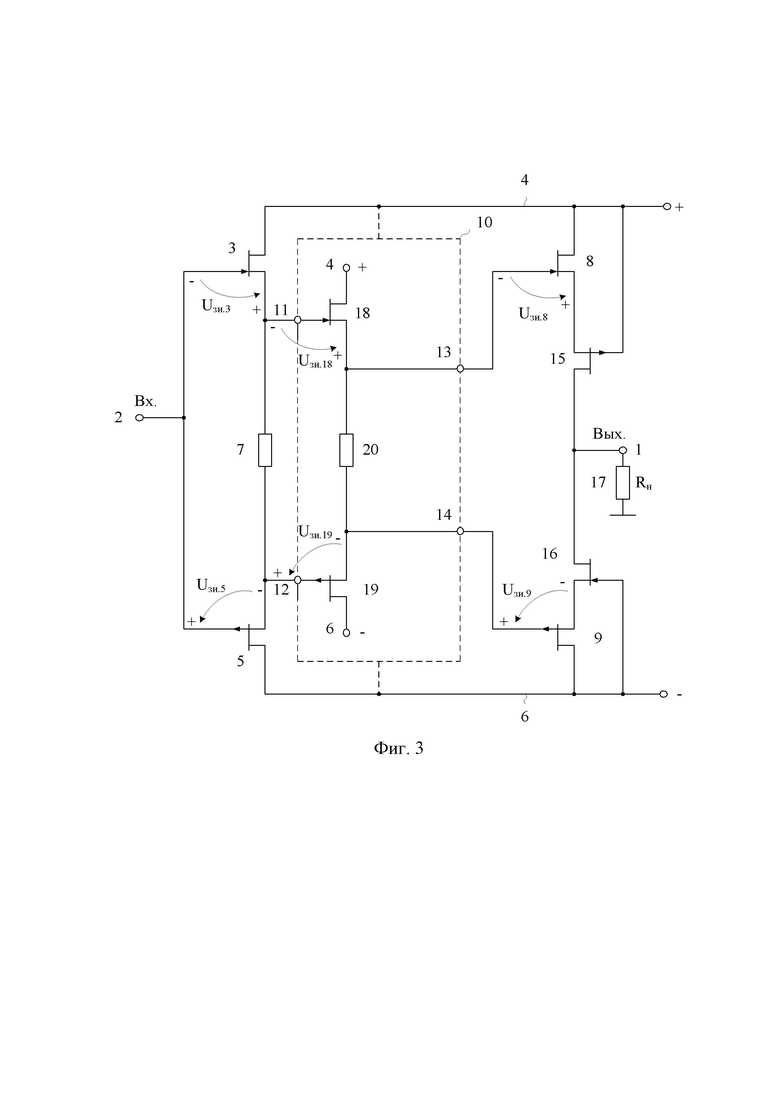

На чертеже фиг. 3 показана схема заявляемого НУ, соответствующая п. 2 формулы изобретения.

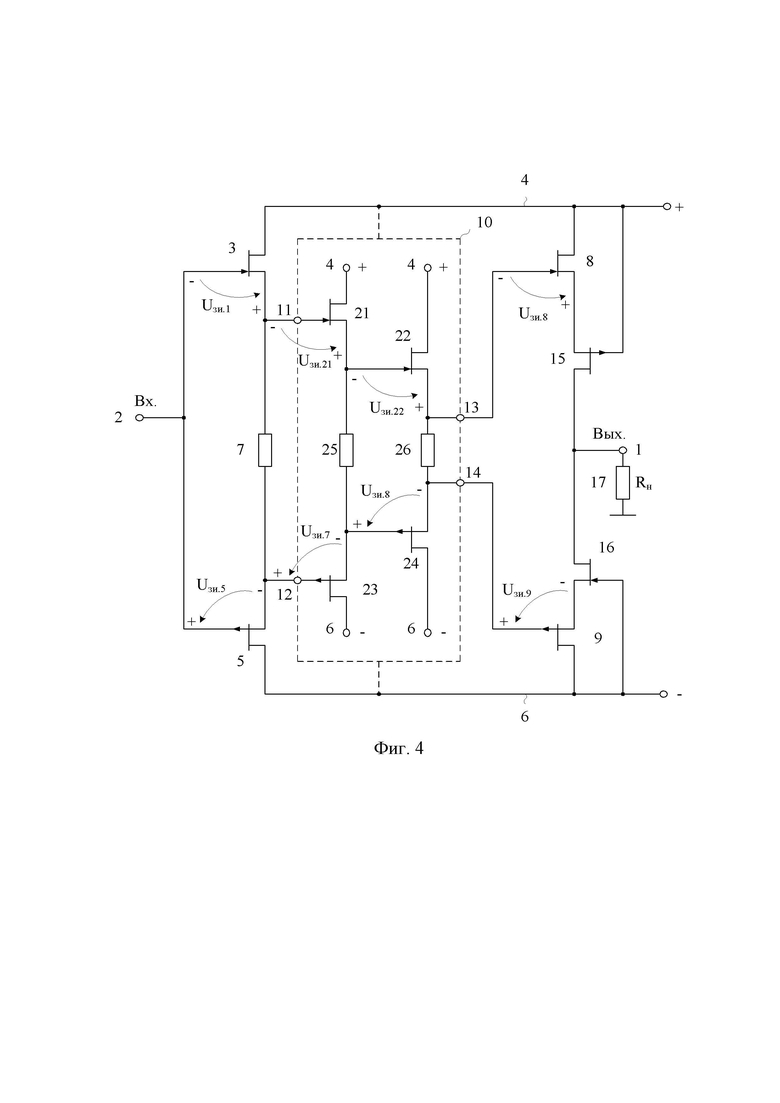

На чертеже фиг. 4 приведена схема НУ, соответствующая п. 3 формулы изобретения.

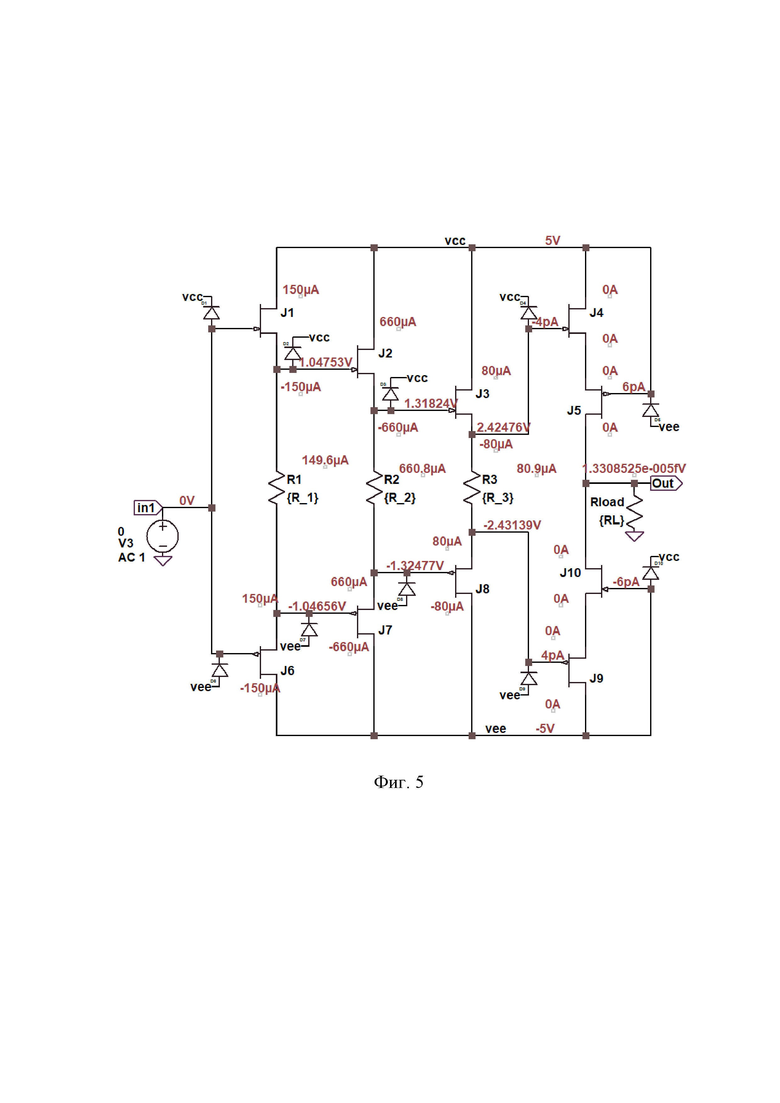

На чертеже фиг. 5 представлен статический режим оптимизированной схемы НУ фиг. 4 в среде LTSpice (Analog Devices, США) при напряжении питания Uпит=±5 В, температруре t=-197°C, сопротивлениях Rн=100 кОм, R_1 = 14кОм; R_2 = 4 кОм; R_3 = 60 кОм и числе параллельно включенных элементарных транзисторов в структуре j-го составного транзистора:

N_2 = 1; N_4=N_10 = 15; N_5=N_9 = 15; N_7 = 1.

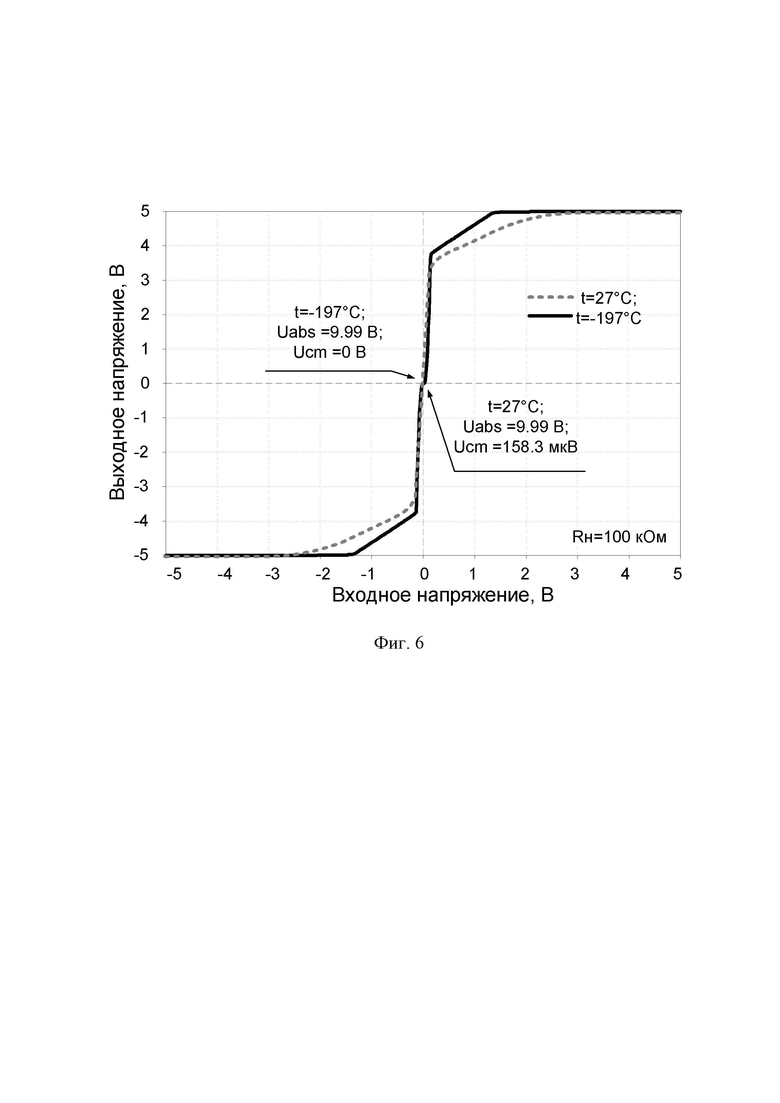

На чертеже фиг. 6 приведена зависимость выходного напряжения НУ фиг. 5 от входного напряжения (V3) при напряжениях питания Uпит=±5 В, сопротивлении нагрузки Rн=100 кОм для температур t=-197°C и t=27°C.

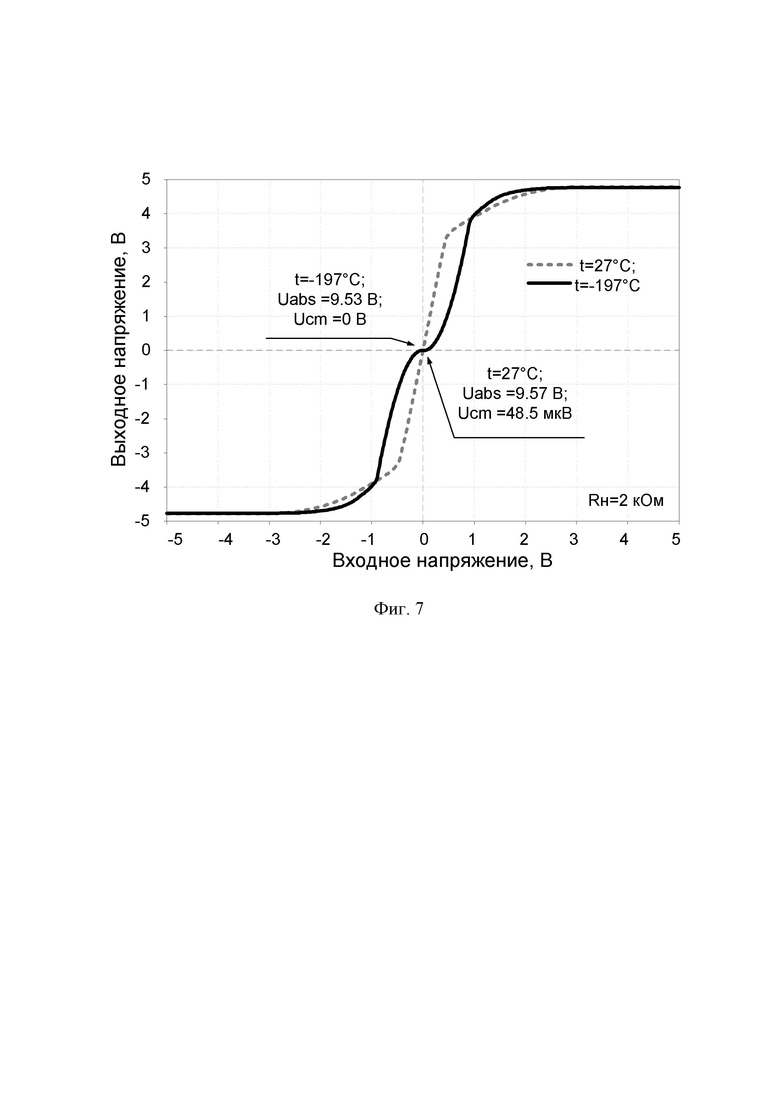

На чертеже фиг. 7 показана зависимость выходного напряжения НУ фиг. 5 от входного напряжения (V3) при напряжениях питания Uпит=±5 В, сопротивлении нагрузки Rн=2 кОм для температур t=-197°C и t=27°C.

Неинвертирующий усилитель с токовым выходом 1 для работы при низких температурах фиг. 2 содержит вход 2 устройства, первый 3 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан с первой 4 шиной источника питания, второй 5 входной полевой транзистор, затвор которого подключен ко входу 2 устройства, а сток связан со второй 6 шиной источника питания, токостабилизирующий двухполюсник 7, включенный между истоком первого 3 и истоком второго 5 входных полевых транзисторов, первый 8 выходной полевой транзистор, сток которого связан с первой 4 шиной источника питания, второй 9 выходной полевой транзистор, сток которого связан со второй 6 шиной источника питания. В схему введена дифференциальная цепь смещения потенциалов 10, первый 11 вход которой соединен с истоком первого 3 входного полевого транзистора, второй вход 12 подключен к истоку второго 5 входного полевого транзистора, затвор первого 8 выходного полевого транзистора соединен с первым 13 выходом дифференциальной цепи смещения потенциалов 10, затвор второго 9 выходного полевого транзистора соединен со вторым 14 выходом дифференциальной цепи смещения потенциалов 10, исток первого 8 выходного полевого транзистора соединен с истоком первого 15 дополнительного выходного полевого транзистора, затвор которого связан с первой 4 шиной источника питания, а сток соединен с токовым выходом 1 устройства, исток второго 9 выходного полевого транзистора соединен с истоком второго 16 дополнительного выходного полевого транзистора, затвор которого связан со второй 6 шиной источника питания, а сток соединен с токовым выходом 1 устройства двухполюсник 17 моделирует свойства нагрузи, которая подключается к выходу 1 НУ.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, дифференциальная цепь смещения потенциалов 10 содержит первый 18 и второй 19 вспомогательные полевые транзисторы, причем затвор первого 18 вспомогательного полевого транзистора соединен с первым 11 входом дифференциальной цепи смещения потенциалов 10, затвор второго 19 вспомогательного полевого транзистора связан со вторым 12 входом дифференциальной цепи смещения потенциалов 10, исток первого 18 вспомогательного полевого транзистора соединен с первым 13 выходом дифференциальной цепи смещения потенциалов 10, исток второго 19 вспомогательного полевого транзистора связан со вторым 14 выходом дифференциальной цепи смещения потенциалов 10, причем между истоком первого 18 вспомогательного полевого транзистора и истоком второго 19 вспомогательного полевого транзистора включен первый 20 дополнительный резистор, сток первого 18 вспомогательного полевого транзистора согласован с первой 4 шиной источника питания, а сток второго 19 вспомогательного полевого транзистора согласован со второй 6 шиной источника питания.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, дифференциальная цепь смещения потенциалов 10 содержит третий 21 и четвертый 22 вспомогательные полевые транзисторы, а также пятый 23 и шестой 24 вспомогательные полевые транзисторы, причем между истоками третьего 21 и пятого 23 вспомогательных полевых транзисторов включен второй 25 дополнительный резистор, между истоками четвертого 22 и шестого 24 вспомогательных полевых транзисторов включен третий 26 дополнительный резистор, стоки третьего 21 и четвертого 22 вспомогательных полевых транзисторов связаны с первой 4 шиной источника питания, стоки пятого 23 и шестого 24 вспомогательных полевых транзисторов связаны со второй 6 шиной источника питания, затвор третьего 21 вспомогательного полевого транзистора подключен к первому 11 входу дифференциальной цепи смещения потенциалов 10, затвор пятого 23 вспомогательного полевого транзистора подключен ко второму 12 входу дифференциальной цепи смещения потенциалов 10, исток четвертого 22 вспомогательного полевого транзистора соединен с первым 13 выходом дифференциальной цепи смещения потенциалов 10, исток шестого 24 вспомогательного полевого транзистора связан со вторым 14 выходом дифференциальной цепи смещения потенциалов 10, затвор четвертого 22 вспомогательного полевого транзистора соединен с истоком третьего 21 вспомогательного полевого транзистора, а затвор шестого 24 вспомогательного полевого транзистора соединен с истоком пятого 23 вспомогательного полевого транзистора.

Рассмотрим работу заявляемого неинвертирующего усилителя фиг. 2 на примере анализа свойств схемы фиг. 3. В данной схеме при малых uвх. обеспечивается закрытое состояние первого 8 входного, первого 15 дополнительного, второго 9 входного, второго 16 дополнительного выходного полевых транзисторов, то есть нулевой сквозной ток между шинами источников питания 4 и 6.

При положительном приращении u(+)вх., начиная с некоторого порогового напряжения первый 8 выходной и первый 15 дополнительный выходной полевые транзисторы входят в активный режим и обеспечивают положительное приращение (i(+)н) токов в нагрузке Rн (17).

При отрицательных u(-)вх. работают второй 9 выходной и второй 16 дополнительный выходной полевой транзисторы, создавая в нагрузке 17 ток другого направления i(-)н (фиг. 3).

Замечательная особенность схемы фиг. 3 (а также фиг. 4) состоит в том, что при максимальном u(+)вх., близком к напряжению на первой 4 шине источника питания, первый 8 выходной полевой транзистор входит в режим насыщения. Как следствие, исток первого 15 дополнительного выходного полевого транзистора оказывается подключен к первой 4 шине источника питания. При этом обеспечивается максимальный ток в нагрузке Rн (17):

i(+)н = I(-)н.max.

За счет рационального выбора схемы дифференциальной цепи смещения потенциалов 10, можно минимизировать зону нечувствительности на амплитудной характеристике НУ (фиг. 6).

Анализ амплитудных характеристик НУ (фиг. 5), представленных на чертежах фиг. 6 и фиг. 7, показывает, что заявляемая схема НУ обеспечивает изменение выходного напряжения от первой 4 шины источника питания, до второй 6 шины источника питания, т.е. реализует опцию rail-to-rail при изменении сопротивления нагрузки в широких пределах (Rн=2÷100кОм).

Если в схеме фиг. 2 – фиг. 5 используются низкоомные нагрузки, то предлагаемые НУ рекомендуется использовать в качестве буферных усилителей с rail-to-rail токовым выходом.

Когда НУ фиг.2-фиг.4 применяется как промежуточный каскад ОУ, на его основе может быть создан высокоимпедансный, узел, в схеме ОУ, обеспечивающий большой коэффициент усиления по напряжению. При этом величина эквивалентного выходного сопротивления (Rвых) НУ, например фиг.3, будет достигать уровня единиц-сотен мегаом:

Yвых= Rвых-1=S15⋅μ15-1+S16⋅μ16-1,

где S15, S16 - крутизна стоко-затворной характеристики первого 15 и второго 16 дополнительного полевого транзисторов в заданной рабочей точке;

μ15, μ16 – коэффициенты внутренней обратной связи транзисторов 15 и 16 (μ≈10-3-10-4), учитывающие влияние напряжения на стоке Uзс на стоко-затворную характеристику (μ=ΔUзи/ΔUзс, при Iи=const).

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известным схемотехническим решением.

Библиографический список

1. Патент RU 2393625, 27.06.2010 г.

2. Патент RU 2523947, 27.07.2014 г.

3. Патент RU 2401509, 10.10.2010 г.

4. Патент RU 2307456, 27.09.2007 г.

5. Патент RU 2409889, 20.01.2011 г.

6. Патент US 211/0227650 фиг.8, 2011 г.

7. Патент US 4791383 фиг.1, 1987 г.

8. Патент US 6542032 фиг.1, 2003 г.

9. Патент US 5963065 фиг.2 1999г.

10. Патент RU 2292638, 27.01.2007 г.

11. Патент RU 2621287, 01.06.2017 г.

12. Патент RU 2613842, 21.03.2017 г.

13. Патент RU 2337469, 27.10.2008 г.

14. Патент RU 2313899, 27.12.2007 г.

15. Патент RU 2275736, 27.04.2006 г.

16. Патент US 6956432 фиг.1, 2005 г.

17. Патент US 6037811 фиг.1 2000 г.

18. Патент US 6265941 фиг.3а, 2001 г.

19. Патент US 5734296 фиг.1, 1998 г.

20. Патент EP 1 500 189 фиг.1, 2003 г.

21. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

22. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

23. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28.

24. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

25. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, no. 2 (7), 2013, pp. 42-46.

26. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. – 2014. – №. 1. – С. 32-37.

27. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

28. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

29. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ ТОКОВ | 2017 |

|

RU2651221C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2766864C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739577C1 |

| Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах | 2024 |

|

RU2837569C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| МНОГОКАСКАДНЫЙ КАСКОДНЫЙ УСИЛИТЕЛЬ С ПОСЛЕДОВАТЕЛЬНЫМ ПИТАНИЕМ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2780357C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

Изобретение относится к радиотехнике. Технический результат заключается в создании неинвертирующего CJFet усилителя, обеспечивающего опцию rail-to-rail по выходу и получение повышенных выходных сопротивлений. Последнее качество позволяет создавать высокоомные узлы в аналоговых устройствах и обеспечить их коррекцию амплитудно-частотных характеристик с помощью конденсаторов небольшой емкости. Неинвертирующий усилитель содержит полевые транзисторы, токостабилизирующий двухполюсник, соединенный таким образом, что обеспечивает изменение выходного напряжения от первой шины источника питания, до второй шины источника питания, то есть реализует опцию rail-to-rail при изменении сопротивления нагрузки в широких пределах. 2 з.п. ф-лы, 7 ил.

1. Неинвертирующий усилитель с токовым выходом (1) для работы при низких температурах, содержащий вход (2) устройства, первый (3) входной полевой транзистор, затвор которого подключен ко входу (2) устройства, а сток связан с первой (4) шиной источника питания, второй (5) входной полевой транзистор, затвор которого подключен ко входу (2) устройства, а сток связан со второй (6) шиной источника питания, токостабилизирующий двухполюсник (7), включенный между истоком первого (3) и истоком второго (5) входных полевых транзисторов, первый (8) выходной полевой транзистор, сток которого связан с первой (4) шиной источника питания, второй (9) выходной полевой транзистор, сток которого связан со второй (6) шиной источника питания, отличающийся тем, что в схему введена дифференциальная цепь смещения потенциалов (10), первый (11) вход которой соединен с истоком первого (3) входного полевого транзистора, второй вход (12) подключен к истоку второго (5) входного полевого транзистора, затвор первого (8) выходного полевого транзистора соединен с первым (13) выходом дифференциальной цепи смещения потенциалов (10), затвор второго (9) выходного полевого транзистора соединен со вторым (14) выходом дифференциальной цепи смещения потенциалов (10), исток первого (8) выходного полевого транзистора соединен с истоком первого (15) дополнительного выходного полевого транзистора, затвор которого связан с первой (4) шиной источника питания, а сток соединен с токовым выходом (1) устройства, исток второго (9) выходного полевого транзистора соединен с истоком второго (16) дополнительного выходного полевого транзистора, затвор которого связан со второй (6) шиной источника питания, а сток соединен с токовым выходом (1) устройства.

2. Усилитель по п.1, отличающийся тем, что дифференциальная цепь смещения потенциалов (10) содержит первый (18) и второй (19) вспомогательные полевые транзисторы, причем затвор первого (18) вспомогательного полевого транзистора соединен с первым (11) входом дифференциальной цепи смещения потенциалов (10), затвор второго (19) вспомогательного полевого транзистора связан со вторым (12) входом дифференциальной цепи смещения потенциалов (10), исток первого (18) вспомогательного полевого транзистора соединен с первым (13) выходом дифференциальной цепи смещения потенциалов (10), исток второго (19) вспомогательного полевого транзистора связан со вторым (14) выходом дифференциальной цепи смещения потенциалов (10), причем между истоком первого (18) вспомогательного полевого транзистора и истоком второго (19) вспомогательного полевого транзистора включен первый (20) дополнительный резистор, сток первого (18) вспомогательного полевого транзистора согласован с первой (4) шиной источника питания, а сток второго (19) вспомогательного полевого транзистора согласован со второй (6) шиной источника питания.

3. Усилитель по п.1, отличающийся тем, что дифференциальная цепь смещения потенциалов (10) содержит третий (21) и четвертый (22) вспомогательные полевые транзисторы, а также пятый (23) и шестой (24) вспомогательные полевые транзисторы, причем между истоками третьего (21) и пятого (23) вспомогательных полевых транзисторов включен второй (25) дополнительный резистор, между истоками четвертого (22) и шестого (24) вспомогательных полевых транзисторов включен третий (26) дополнительный резистор, стоки третьего (21) и четвертого (22) вспомогательных полевых транзисторов связаны с первой (4) шиной источника питания, стоки пятого (23) и шестого (24) вспомогательных полевых транзисторов связаны со второй (6) шиной источника питания, затвор третьего (21) вспомогательного полевого транзистора подключен к первому (11) входу дифференциальной цепи смещения потенциалов (10), затвор пятого (23) вспомогательного полевого транзистора подключен ко второму (12) входу дифференциальной цепи смещения потенциалов (10), исток четвертого (22) вспомогательного полевого транзистора соединен с первым (13) выходом дифференциальной цепи смещения потенциалов (10), исток шестого (24) вспомогательного полевого транзистора связан со вторым (14) выходом дифференциальной цепи смещения потенциалов (10), затвор четвертого (22) вспомогательного полевого транзистора соединен с истоком третьего (21) вспомогательного полевого транзистора, а затвор шестого (24) вспомогательного полевого транзистора соединен с истоком пятого (23) вспомогательного полевого транзистора.

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДРАЙВЕР КОММУТАТОРА РАЗРЯДНОГО ТОКА ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2014 |

|

RU2572389C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| US 5444413 A, 22.08.1995. | |||

Авторы

Даты

2019-12-25—Публикация

2019-08-21—Подача