Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных усилителей и выходных каскадов усиления по мощности в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем микроэлектронных двухтактных буферных усилителей (БУ), которые реализуются на комплементарных биполярных (BJT) или полевых (КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-29]. Благодаря высокой симметрии, простоте и относительно малому напряжению смещения нуля (Uсм=100ч200 мВ) вышеназванные схемотехнические решения БУ наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-29].

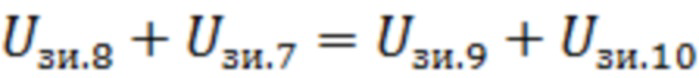

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1) на комплементарных полевых транзисторах, представленный в патенте US № 7.764.123, fig. 3, 2010 г. Данная схема рассмотрена и в других патентах (US № 5.351.012, 1994 г.; US № 6.215.357 fig. 3, 2001 г.; US № 5.973.534), а также в ряде публикаций, например [28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347]. Схема БУ-прототипа фиг. 1 содержит потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан со второй 6 шиной источника питания, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан с первой 4 шиной источника питания, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, затвор подключен к истоку первого 7 входного полевого транзистора, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, затвор подключен к истоку второго 8 входного полевого транзистора, а сток соединен со вторым 5 токовым выходом устройства.

БУ-прототип является основой различных входных и выходных каскадов ОУ с потенциальной отрицательной обратной связью [29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154], а также ОУ с токовой отрицательной обратной связью [28,29]. Кроме этого, данный БУ, в связи с его высокой значимостью в приборостроении, выпускается многими фирмами в виде самостоятельных серийных микросхем (NA5033, ORA633, BUF-601, BUF-604, BUF-634, AD9630, MAX405, KM432UE1, M142UE2, M143UE2 и др.), реализуемых на КМОП, BJT, SiGe и других технологических процессах.

Существенный недостаток известного буферного усилителя состоит в том, что статический режим транзисторов его схемы определяется двумя независимыми источниками опорного тока (I1, I2, фиг. 1). Это отрицательно сказывается на работе БУ в условиях низких температур, а также затрудняет управление нагрузочной способностью БУ при изменении сопротивления его нагрузки в широких пределах. В практических схемах БУ (фиг. 1) высококачественные источники опорного тока I1, I2, существенно влияющие на параметры БУ, выполняются по достаточно сложным транзисторным схемам, что отрицательно влияет на общее энергопотребление. Таким образом, БУ-прототип имеет ограниченное применение, прежде всего, в тяжелых условиях эксплуатации (низкие температуры, проникающая радиация).

Основная задача предлагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ на комплементарных полевых транзисторах, обеспечивающего (при высокой линейности амплитудной характеристики) повышенную стабильность статического режима транзисторов и низкий уровень шумов, в том числе при работе в диапазоне низких температур.

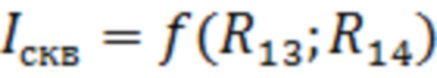

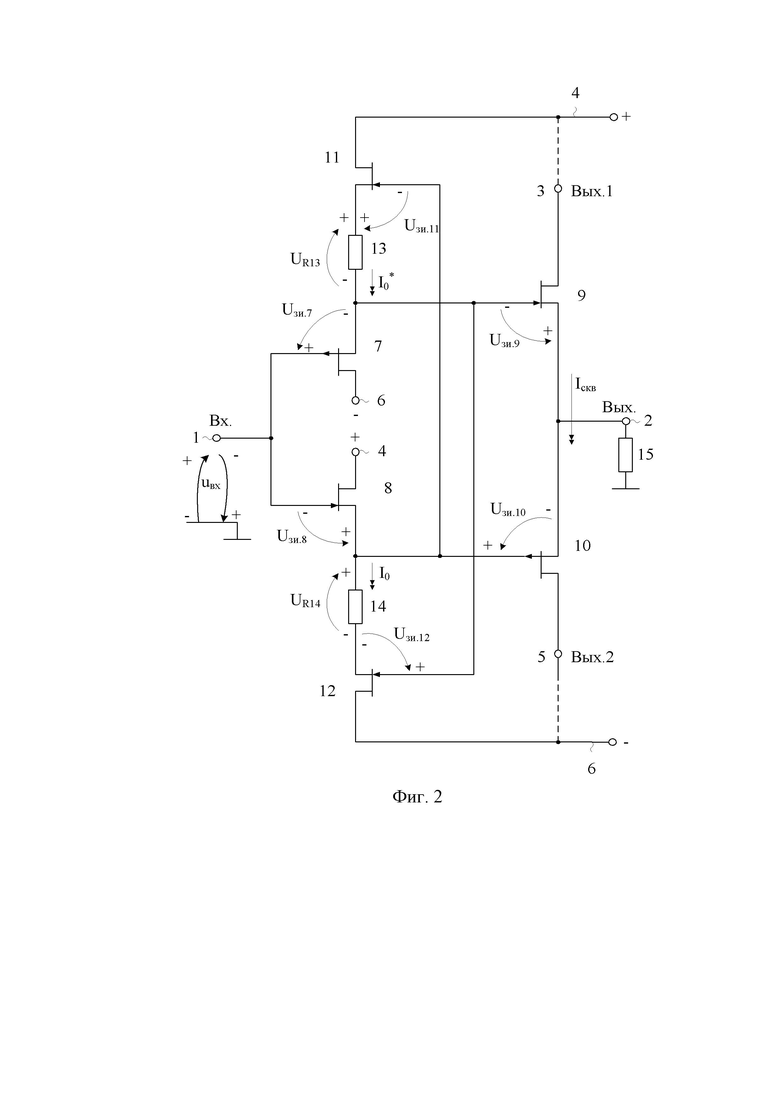

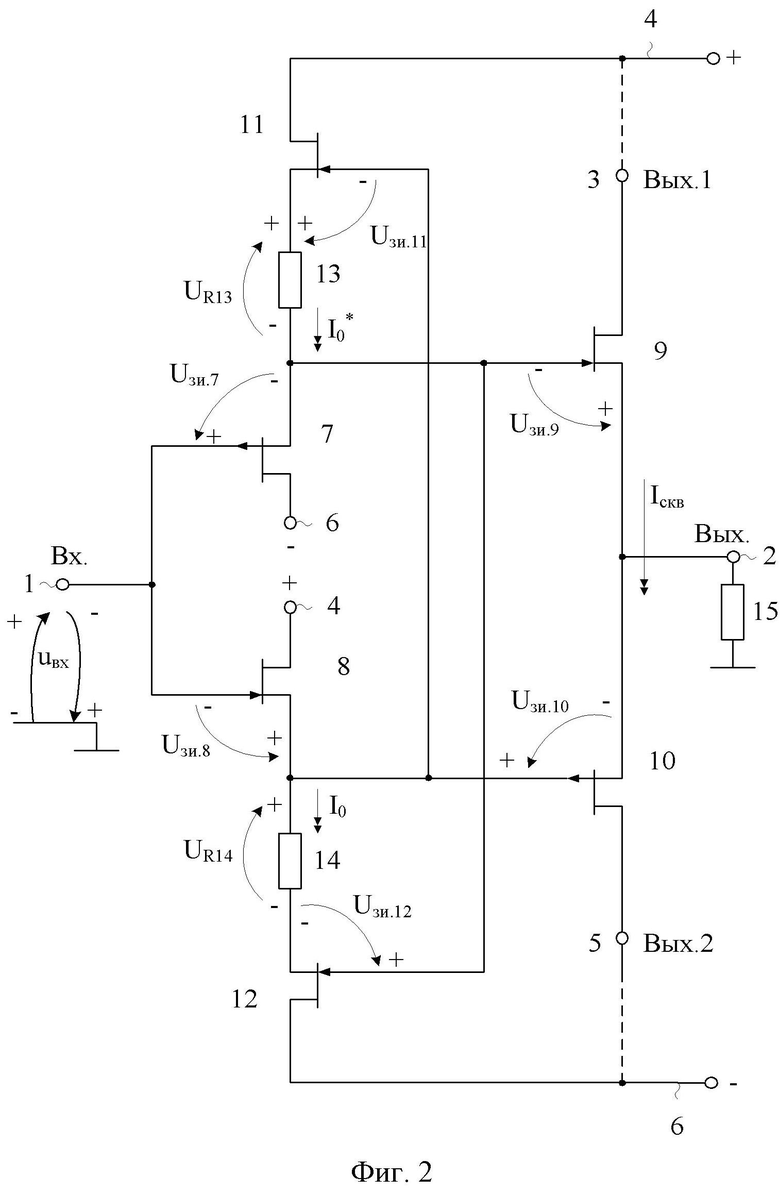

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан со второй 6 шиной источника питания, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан с первой 4 шиной источника питания, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, затвор подключен к истоку первого 7 входного полевого транзистора, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, затвор подключен к истоку второго 8 входного полевого транзистора, а сток соединен со вторым 5 токовым выходом устройства, предусмотрены новые элементы и связи – в схему введены первый 11 и второй 12 дополнительные полевые транзисторы с разными типами каналов, причем исток первого 11 дополнительного полевого транзистора связан с истоком первого 7 входного полевого транзистора через первый 13 дополнительный резистор, его сток подключен к первой 4 шине источника питания, а затвор связан с истоком второго 8 полевого транзистора, исток второго 12 дополнительного полевого транзистора связан с истоком второго 8 входного полевого транзистора через второй 14 дополнительный резистор, его сток подключен ко второй 6 шине источника питания, а затвор связан с истоком первого 7 входного полевого транзистора.

Первый 3 и второй 5 токовые выходы заявляемого БУ могут подключаться в некоторых практических схемах его включения (например, в усилителях с токовой отрицательной обратной связью [28,29]) к токовым зеркалам и другим выходным подсхемам того или иного проектируемого аналогового устройства, решающего практические задачи обработки аналоговых сигналов. В частном случае, в соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства соединен с первой 4 шиной источника питания, а второй 5 токовый выход устройства соединен со второй 6 шиной источника питания. В данном варианте построения БУ фиг. 2 токовые выходы 3 и 5 не используются, а БУ выполняет только одну функцию – согласование с источником сигнала (по величине входного сопротивления), а также передачу в нагрузку входного напряжения с коэффициентом передачи, близким к единице.

На фиг. 1 представлена схема БУ-прототипа, а на чертеже фиг. 2 – схема заявляемого буферного усилителя в соответствии с п.1, п.2 формулы изобретения.

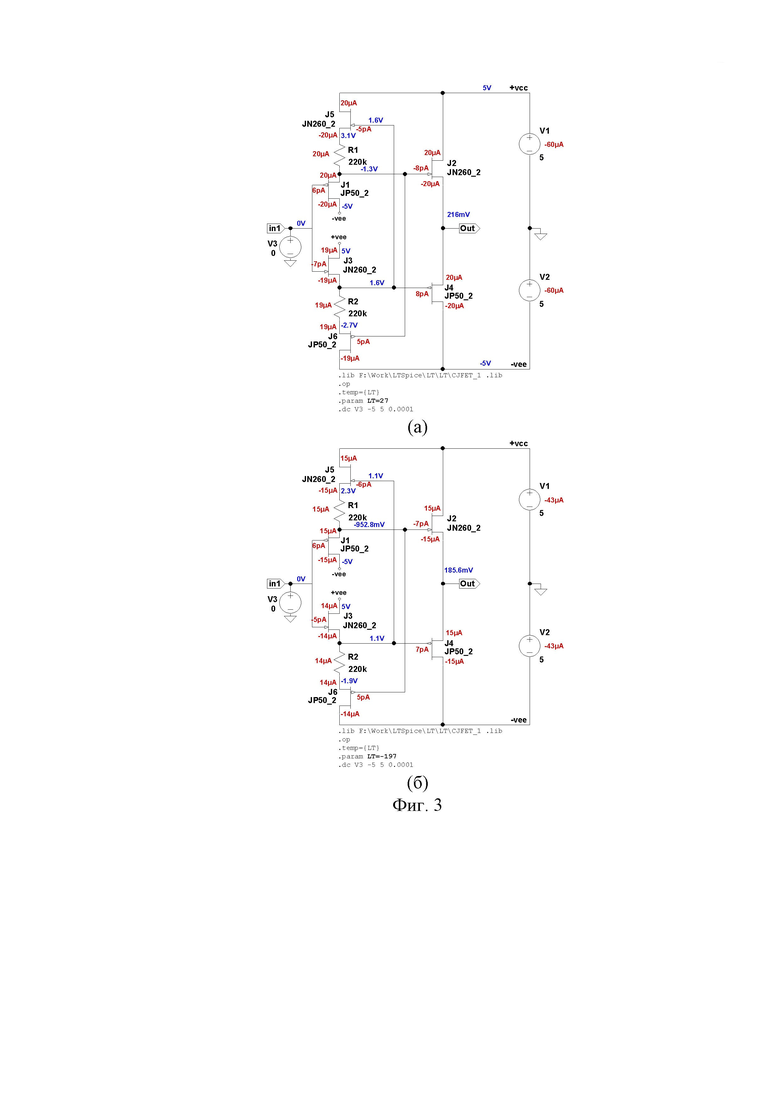

На фиг. 3 показан статический режим заявляемого буферного усилителя фиг. 2 в среде компьютерного моделирования LTspice (фирма Analog Devices) на моделях комплементарных CJFet полевых транзисторов [31] при температурах 27°С (а) и -197°С (б).

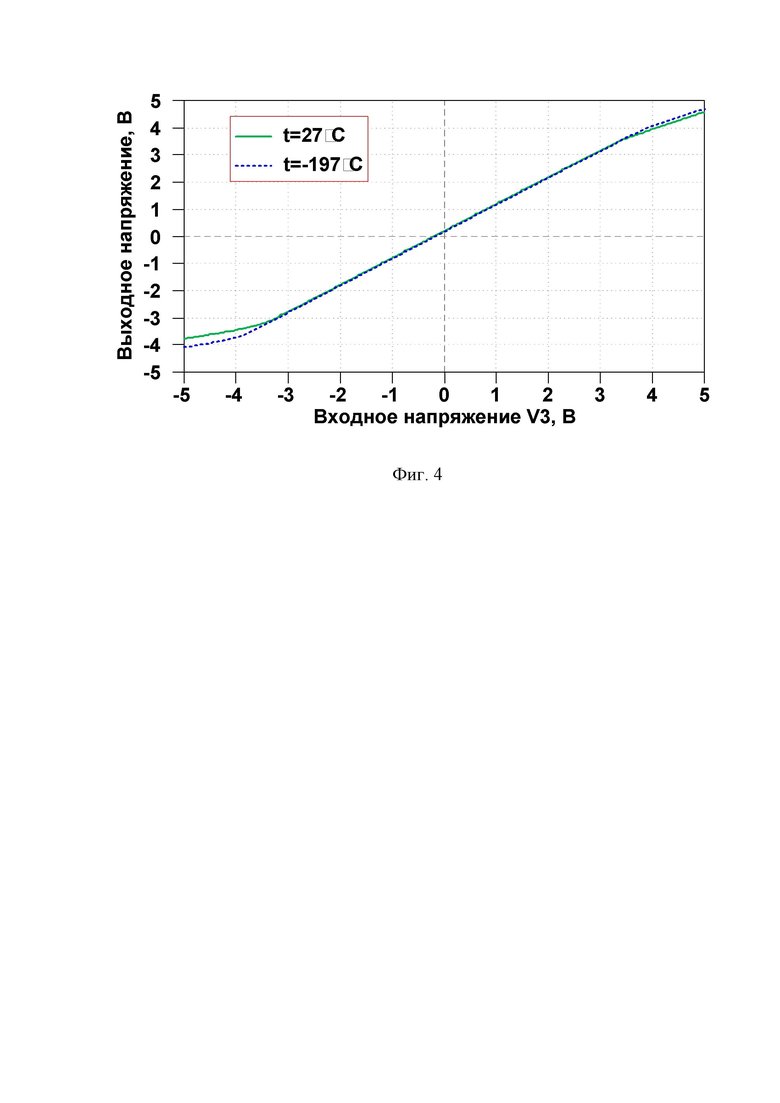

На фиг. 4 приведена зависимость выходного напряжения БУ фиг. 3 от входного напряжения в диапазоне температур 27°С и -197°С.

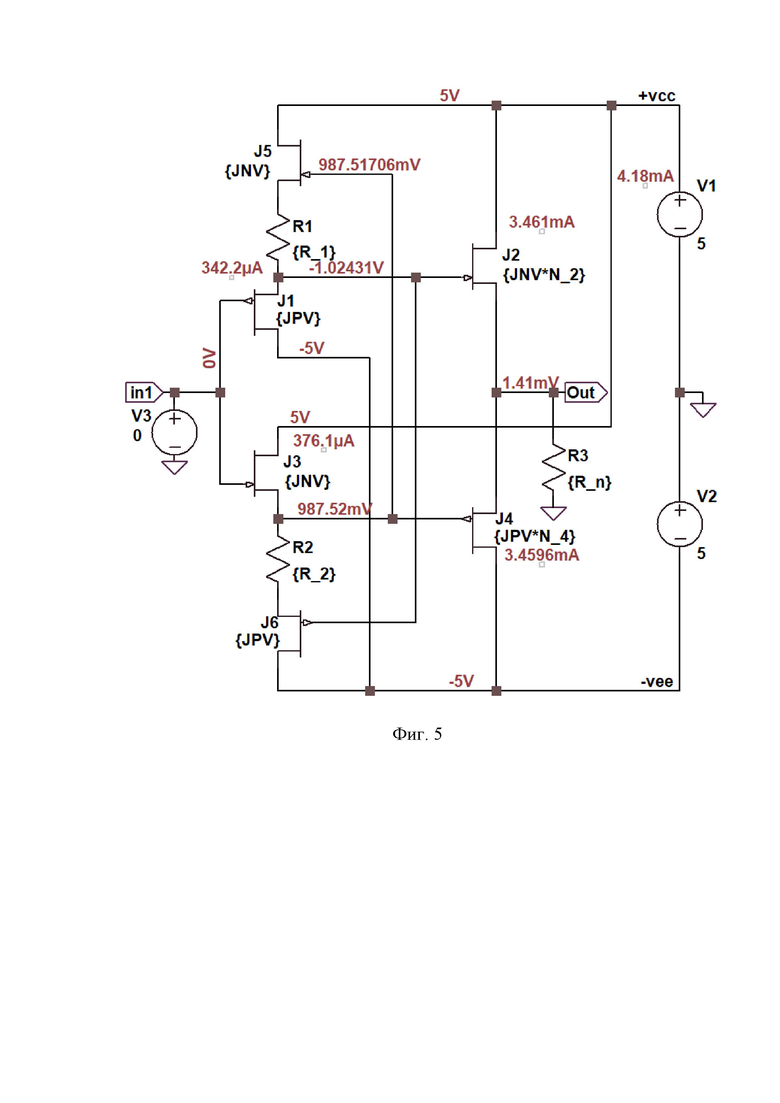

На фиг. 5 представлен статический режим заявляемого БУ фиг. 2 при оптимальных значениях параметров элементов, рассчитанных с помощью программы параметрической оптимизации в среде LTspice-17 для случая, когда приоритетным критерием оптимизации является напряжение смещения нуля Uсм. В заявляемой схеме БУ этот параметр (Uсм) уменьшается (в сравнении с неоптимальным значением, фиг. 3) более чем в 150 раз. Данный эффект обеспечивается новыми элементами и связями между ними в соответствии с формулой изобретения.

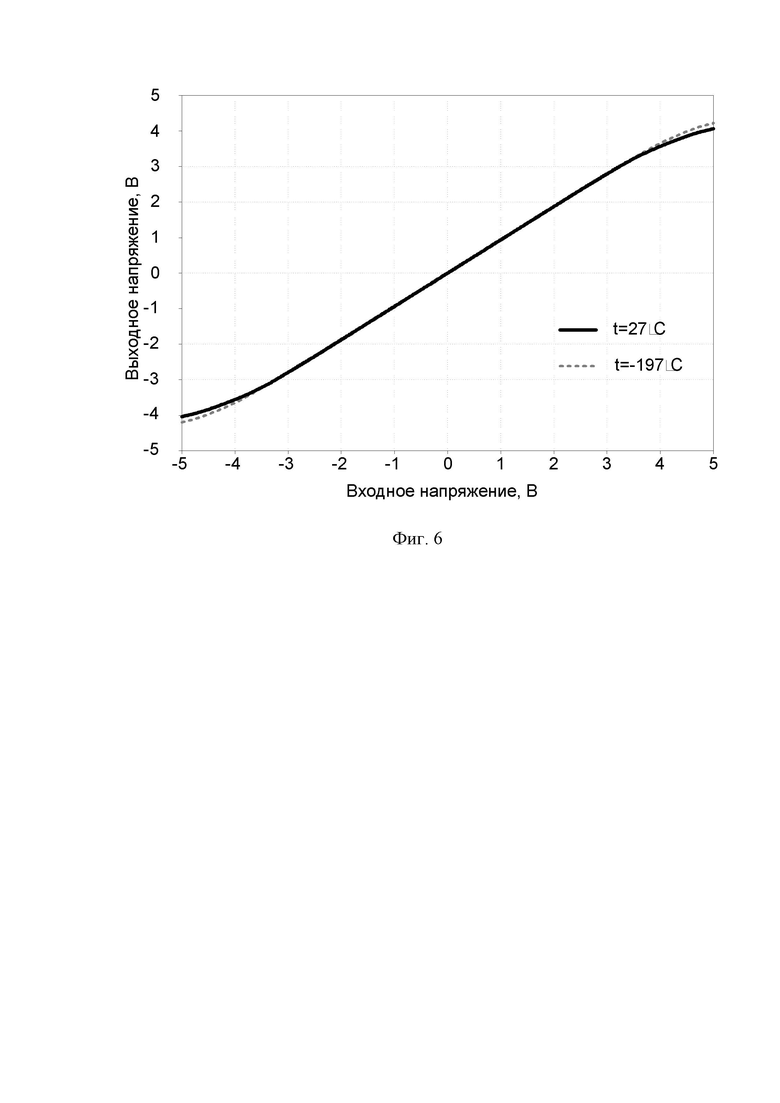

На фиг. 6 показана зависимость выходного напряжения оптимизированной схемы БУ фиг. 5 от входного при температурах 27°С и -197°С. Учитывая, что полевые транзисторы с управляющим p-n переходом успешно работают в условиях радиации [30,31], можно утверждать, что заявляемый БУ характеризуется также высокой радиационной стойкостью к потоку нейтронов и накопленной дозе радиации.

Буферный усилитель на основе комплементарных полевых транзисторов с управляющим p-n переходом для работы при низких температурах фиг. 2 содержит потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан со второй 6 шиной источника питания, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, а сток связан с первой 4 шиной источника питания, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, затвор подключен к истоку первого 7 входного полевого транзистора, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, затвор подключен к истоку второго 8 входного полевого транзистора, а сток соединен со вторым 5 токовым выходом устройства. В схему введены первый 11 и второй 12 дополнительные полевые транзисторы с разными типами каналов, причем исток первого 11 дополнительного полевого транзистора связан с истоком первого 7 входного полевого транзистора через первый 13 дополнительный резистор, его сток подключен к первой 4 шине источника питания, а затвор связан с истоком второго 8 полевого транзистора, исток второго 12 дополнительного полевого транзистора связан с истоком второго 8 входного полевого транзистора через второй 14 дополнительный резистор, его сток подключен ко второй 6 шине источника питания, а затвор связан с истоком первого 7 входного полевого транзистора.

На чертеже фиг. 2 двухполюсник 15 моделирует свойства нагрузки БУ.

В частном случае на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства соединен с первой 4 шиной источника питания, а второй 5 токовый выход устройства соединен со второй 6 шиной источника питания. В этой схеме включения заявляемый БУ работает как устройство согласования источника сигнала с нагрузкой.

Рассмотрим работу предлагаемого БУ фиг. 2.

Особенность и уникальностью схемы заявляемого БУ состоит в том, что статический режим её транзисторов по току определяется первым 13 и вторым 14 дополнительными резисторами, что позволяет за счет изменения их номиналов обеспечить оптимизацию статического режима по одному из критериев, например, напряжению смещения нуля БУ, статическому току потребления и т.д.

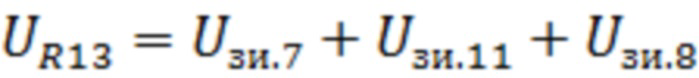

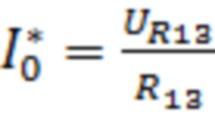

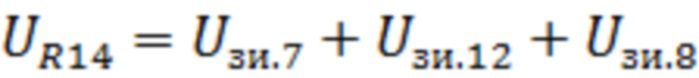

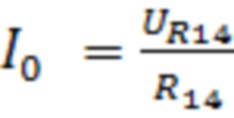

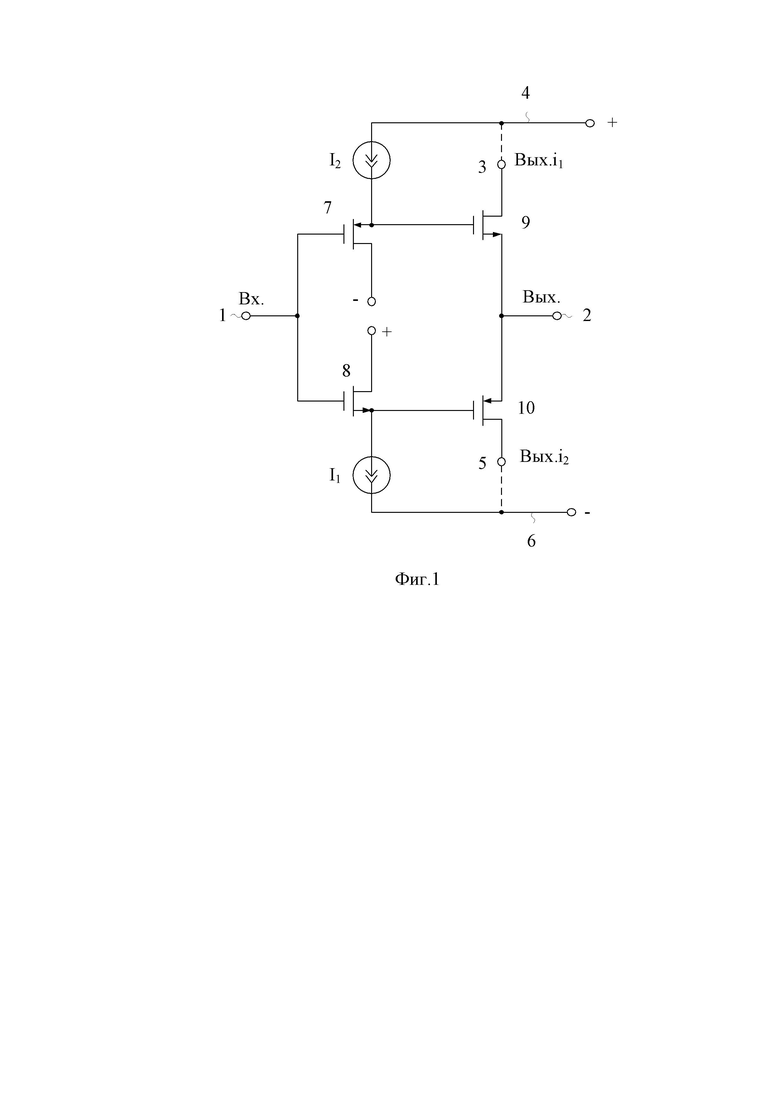

Статические токи через первый 13 и второй 14 дополнительные резисторы определяются уравнениями на основе второго закона Кирхгофа:

, (1)

, (1)

, (2)

, (2)

, (3)

, (3)

, (4)

, (4)

где Uзи.i – напряжение затвор-исток i-го полевого транзистора при токе истока, равном  (I0).

(I0).

Аналогично, статический ток истоков первого 9 и второго 10 выходных полевых транзисторов определяется уравнениями

. (5)

. (5)

При этом сквозной ток

. (6)

. (6)

Таким образом, в схеме фиг. 2 токи истоков первого 9 и второго 10 выходных транзисторов определяются (6) сопротивлениями первого 13 и второго 14 дополнительных резисторов.

Если первый 7 входной и второй 9 выходной полевые транзисторы, а также второй 8 входной и второй 10 выходной полевые транзисторы идентичны, то из уравнений (2) и (6) следует, что токи стока этих транзисторов определяются сопротивлениями двух резисторов 13 и 14. Как следствие, для регулировки напряжения смещения нуля БУ фиг. 2 эти резисторы, а также, например, число параллельно включенных элементарных полевых транзисторов в структуре составных выходных транзисторов 9 и 10, может быть неодинаково. Возможности такой подстройки величины напряжения смещения нуля БУ продемонстрированы в схеме фиг.5. В частном случае вместо параллельного включения нескольких элементарных полевых транзисторов в структуре составных полевых транзисторов 9 и 10 возможно изменение геометрических размеров канала данных активных элементов (выходных транзисторов 9 и 10).

Таким образом, заявляемый БУ допускает параметрическую оптимизацию параметров, например, по критерию минимизации напряжения смещения нуля, которая в реальных схемах обеспечивается за счет оптимального выбора сопротивлений первого 13 и второго 14 дополнительных резисторов, а также длины и ширины канала первого 9 и второго 10 выходных полевых транзисторов. Другие известные схемы БУ рассматриваемого класса таким свойством не обладают. В них из-за неидентичности напряжения отсечки полевых транзисторов с p- и n-каналами, которую невозможно устранить технологическим путем, напряжение смещения нуля БУ всегда остается достаточно большим (сотни милливольт).

Таким образом, компьютерное моделирование в среде LTspice и оптимизация заявляемой схемы БУ (фиг. 4, фиг. 5, фиг. 6) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [30,31], имеет существенные достоинства в сравнении с известными вариантами построения БУ при их практической реализации, в т.ч. в рамках КМОП технологического процесса.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154.

30. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

| название | год | авторы | номер документа |

|---|---|---|---|

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| Быстродействующий выходной каскад аналоговых микросхем на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах | 2019 |

|

RU2711725C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2712410C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2020 |

|

RU2721940C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| ДВУХТАКТНЫЙ ВЫХОДНОЙ КАСКАД КЛАССА AB АНАЛОГОВЫХ МИКРОСХЕМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2706869C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| ШИРОКОПОЛОСНЫЙ ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ-ТОК» НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739213C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

Изобретение относится к аналоговой микроэлектронике. Технический результат заключается в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ на комплементарных полевых транзисторах, обеспечивающего повышенную стабильность статического режима транзисторов и низкий уровень шумов, в том числе при работе в диапазоне низких температур. Усилитель содержит источник питания, полевые транзисторы, дополнительный резистор. заявляемый БУ допускает параметрическую оптимизацию параметров, например, по критерию минимизации напряжения смещения нуля, которая в реальных схемах обеспечивается за счет оптимального выбора сопротивлений первого и второго дополнительных резисторов, а также длины и ширины канала первого и второго выходных полевых транзисторов. 1 з.п. ф-лы, 7 ил.

1. Буферный усилитель на основе комплементарных полевых транзисторов с управляющим p-n переходом для работы при низких температурах, содержащий потенциальный вход (1) и потенциальный выход (2) устройства, первый 3 токовый выход устройства, согласованный с первой (4) шиной источника питания, второй (5) токовый выход устройства, согласованный со второй (6) шиной источника питания, первый (7) входной полевой транзистор, затвор которого соединен с потенциальным входом (1) устройства, а сток связан со второй (6) шиной источника питания, второй (8) входной полевой транзистор, затвор которого соединен с потенциальным входом (1) устройства, а сток связан с первой (4) шиной источника питания, первый (9) выходной полевой транзистор, исток которого связан с потенциальным выходом (2) устройства, затвор подключен к истоку первого (7) входного полевого транзистора, а сток соединен с первым (3) токовым выходом устройства, второй (10) выходной полевой транзистор, исток которого соединен с потенциальным выходом (2) устройства, затвор подключен к истоку второго (8) входного полевого транзистора, а сток соединен со вторым (5) токовым выходом устройства, отличающийся тем, что в схему введены первый (11) и второй (12) дополнительные полевые транзисторы с разными типами каналов, причем исток первого (11) дополнительного полевого транзистора связан с истоком первого (7) входного полевого транзистора через первый (13) дополнительный резистор, его сток подключен к первой (4) шине источника питания, а затвор связан с истоком второго (8) полевого транзистора, исток второго (12) дополнительного полевого транзистора связан с истоком второго (8) входного полевого транзистора через второй (14) дополнительный резистор, его сток подключен ко второй (6) шине источника питания, а затвор связан с истоком первого (7) входного полевого транзистора.

2. Усилитель по п. 1, отличающийся тем, что первый (3) токовый выход устройства соединен с первой (4) шиной источника питания, а второй (5) токовый выход устройства соединен со второй (6) шиной источника питания.

| US 7764132 B2, 27.07.2010 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДРАЙВЕР КОММУТАТОРА РАЗРЯДНОГО ТОКА ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2014 |

|

RU2572389C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| US 5444413 A, 22.08.1995. | |||

Авторы

Даты

2020-01-14—Публикация

2019-06-19—Подача