Изобретение относится к области цифровой вычислительной техники и может быть использовано в автоматических и автоматизированных измерительных системах различного назначения для коррекции динамической погрешности.

Известно устройство идентификации параметров динамических систем в основе которого лежит фильтр Калмана. Его эффективное функционирование возможно в случае известной априорной информации о законах распределения шумов, что является существенным недостатком [1].

Наиболее близким по технической сущности к заявленному изобретению является устройство идентификации Лагранжевых динамических систем на основе итерационной регуляризации [2]. Однако итерационная форма построения, реализованного в нем алгоритма существенно усложняет задачу его использования.

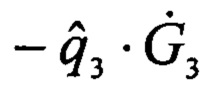

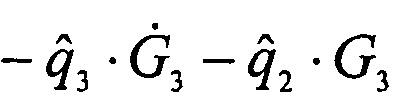

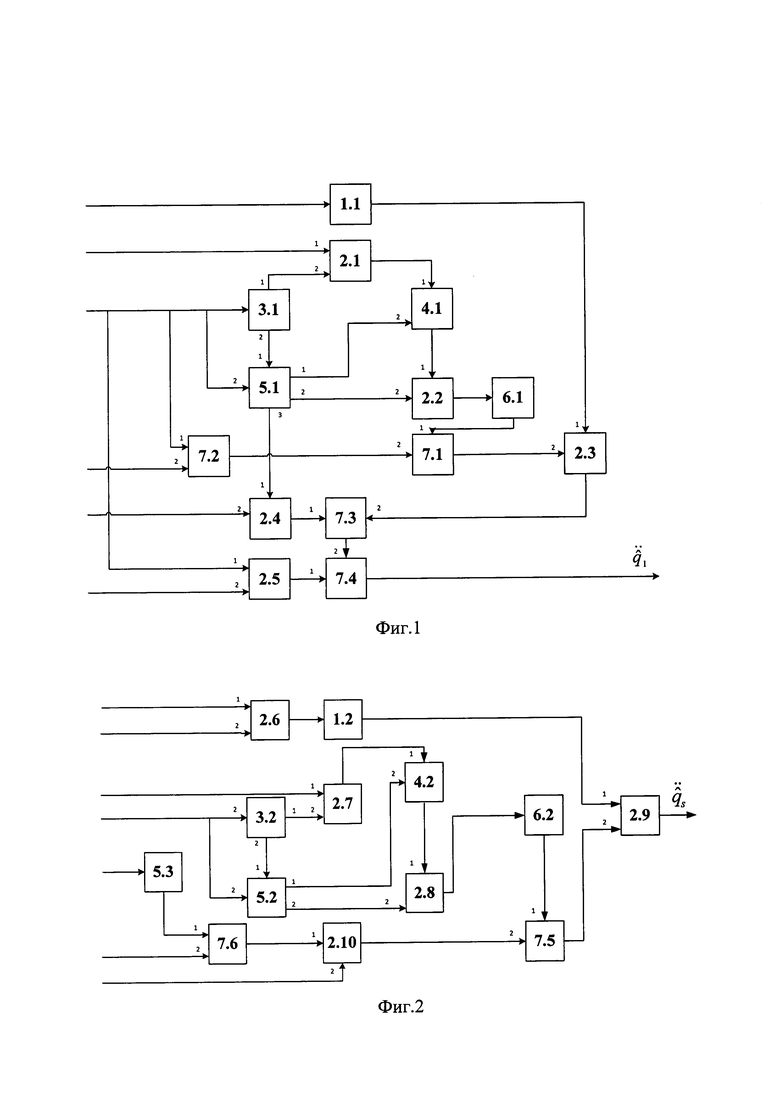

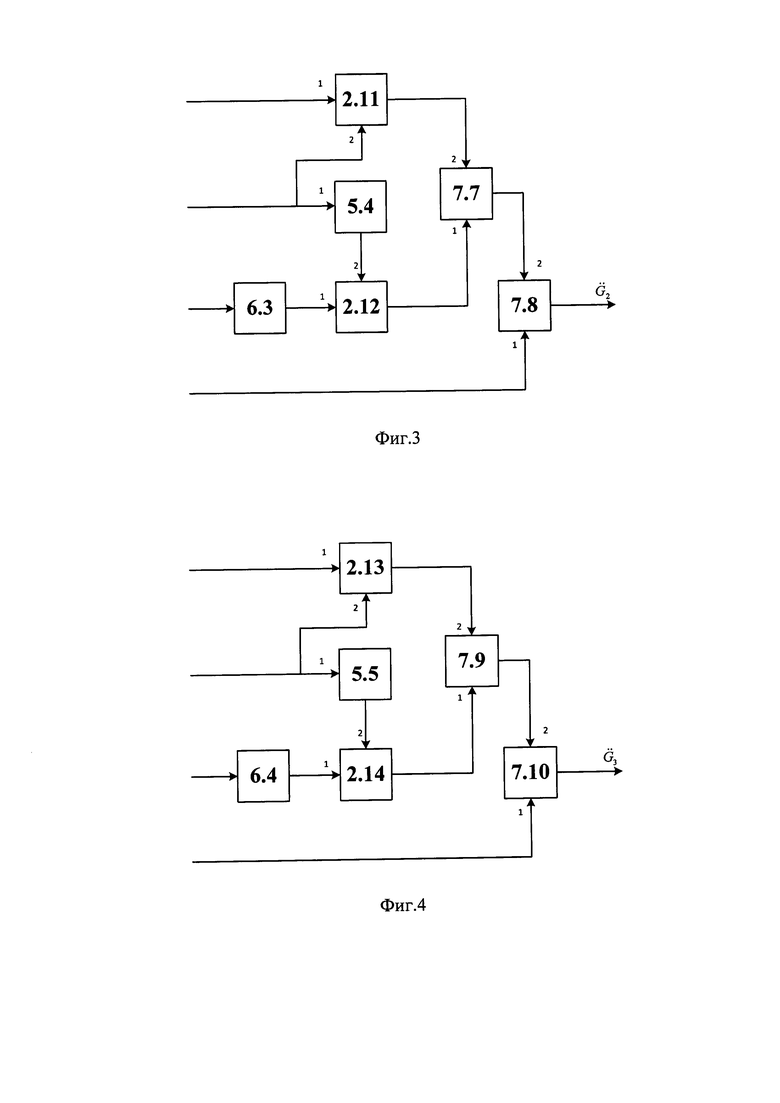

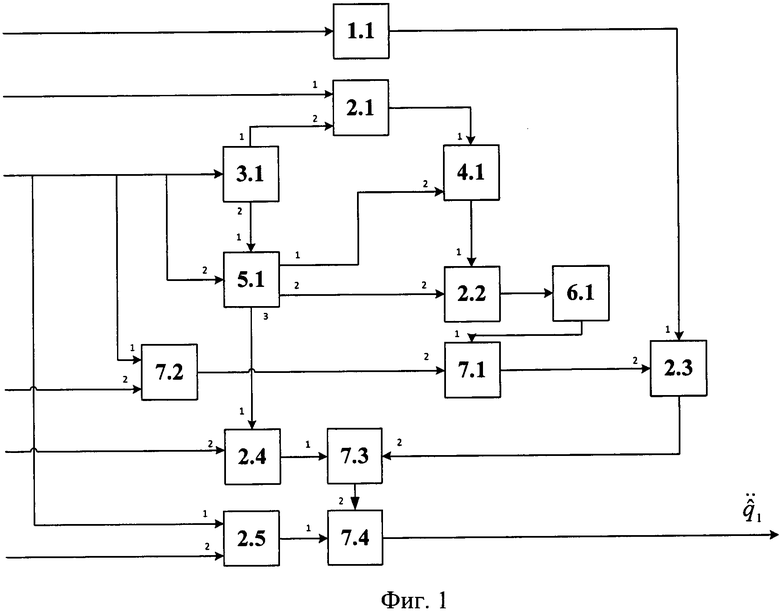

Цель изобретения - повысить точность коррекции динамической погрешности измерительных систем. Указанный технический результат достигается за счет использования условия максимума функции обобщенной мощности в устройстве оценки параметров возмущенных процессов с использованием максимума обобщенной мощности (фиг. 1) - (фиг. 4), которое содержит следующие блоки:

1.1 - первый блок возведения в отрицательную степень;

1.2 - второй блок возведения в отрицательную степень;

2.1 - первый блок умножения;

2.2 - второй блок умножения;

2.3 - третий блок умножения;

2.4 - четвертый блок умножения;

2.5 - пятый блок умножения;

2.6 - шестой блок умножения;

2.7 - седьмой блок умножения;

2.8 - восьмой блок умножения;

2.9 - девятый блок умножения;

2.10 - десятый блок умножения;

2.11 - одиннадцатый блок умножения;

2.12 - двенадцатый блок умножения;

2.13 - тринадцатый блок умножения;

2.14 - четырнадцатый блок умножения;

3.1 - первый блок формирования значения по модулю;

3.2 - второй блок формирования значения по модулю;

4.1 - первый блок формирования деления;

4.2 - второй блок формирования деления;

5.1 - первый блок дифференцирования;

5.2 - второй блок дифференцирования;

5.3 - третий блок дифференцирования;

5.4 - четвертый блок дифференцирования;

5.5 - пятый блок дифференцирования;

6.1- первый блок формирования отрицания;

6.2 - второй блок формирования отрицания;

6.3 - третий блок формирования отрицания;

6.4 - четвертый блок формирования отрицания;

7.1 - первый блок формирования разности;

7.2 - второй блок формирования разности;

7.3 - третий блок формирования разности;

7.4 - четвертый блок формирования разности;

7.5 - пятый блок формирования разности;

7.6 - шестой блок формирования разности;

7.7 - седьмой блок формирования разности;

7.8 - восьмой блок формирования разности;

7.9 - девятый блок формирования разности;

7.10 - десятый блок формирования разности;

входы блоков 1.1, 2.1, 2.4, 2.5, 3.1, 5.1, 7.2 (фиг. 1) являются входами устройства, выход блока 1.1 соединен с первым входом блока 2.3, первый выход блока 3.1 соединен со вторым входом блока 2.1, выход блока 2.1 соединен с первым входом блока 4.1, второй выход блока 3.1 соединен с первым входом блока 5.1, первый выход которого соединен со вторым входом 4.1, при этом выход блока 4.1 соединен с первым входом блока 2.2, второй выход блока 5.1 соединен со вторым входом блока 2.2, выход блока 2.2 соединен с входом блока 6.1, выход которого соединен с первым входом блока 7.1, выход блока 7.2 соединен со вторым входом блока 7.1, выход которого соединен со вторым входом блока 2.3, выход которого соединен со вторым входом блока 7.3, третий выход блока 5.1 соединен с входом блока 2.4, выход которого соединен с первым входом блока 7.3, выход которого соединен со вторым входом блока 7.4, выход блока 2.5 соединен с первым входом блока 7.4, выход блока 7.4 является первым выходом устройства; входы блоков 2.6, 2.7, 2.10, 3.2, 5.2, 5.3, 7.6 (фиг. 2) являются входами устройства, выход блока 2.6 соединен с входом блока 1.2, выход которого соединен с первым входом блока 2.9, первый выход блока 3.2 соединен со вторым входом блока 2.7, выход которого соединен с первым входом блока 4.2, второй выход блока 3.2 соединен с первым входом блока 5.2, первый выход которого соединен со вторым входом блока 4.2, выход которого соединен с первым входом блока 2.8, второй выход блока 5.2 соединен со вторым входом блока 2.8, выход которого соединен с входом блока 6.2, выход которого соединен с первым входом блока 7.5, выход блока 5.3 соединен с первым входом блока 7.6, выход которого соединен с первым входом блока 2.10, выход которого соединен со вторым входом блока 7.5, выход которого соединен со вторым входом блока 2.9, выход блока 2.9 является вторым выходом устройства; входы блоков 2.11, 5.4, 6.3, 7.8 (фиг. 3) являются входами устройства, выход блока 2.11 соединен со вторым входом блока 7.7, выход блока 5.4 соединен со вторым входом блока 2.12, выход блока 6.3 соединен с первым входом блока 2.12, выход которого соединен с первым входом блока 7.7, выход которого соединен со вторым входом блока 7.8, выход блока 7.8 является третьим выходом устройства; входы блоков 2.13, 5.5, 6.4, 7.10 (фиг. 4) являются входами устройства, выход блока 2.13 соединен со вторым входом блока 7.9, выход блока 5.5 соединен со вторым входом блока 2.14, выход блока 6.4 соединен с первым входом блока 2.14, выход которого соединен с первым входом блока 7.9, выход которого соединен со вторым входом блока 7.10, выход блока 7.10 является четвертым выходом устройства.

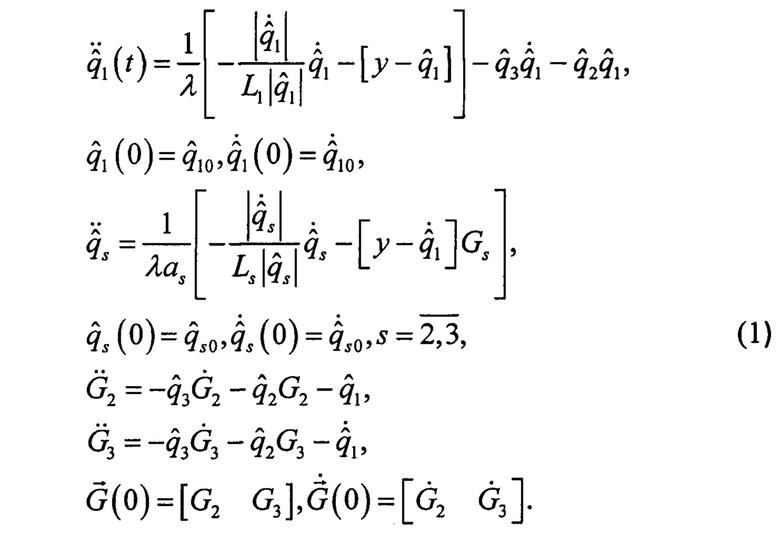

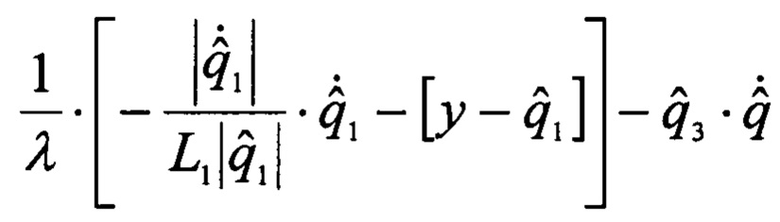

Структура описываемого устройства определяется решением задачи, чья постановка приведена в [3], согласно которой общий вид математической модели процесса динамической системы с двумя идентифицируемыми параметрами представлен выражениями

где q - вектор состояния,

у - результат измерений,

а, λ - неопределенные множители Лагранжа,

L - константа, зависящая от формы линии переключения,

G - функция чувствительности.

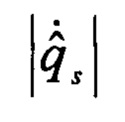

Устройство работает следующим образом. В исходном состоянии на входы устройства (фиг. 1) подаются: λ, L1, у,  На вход первого блока 1.1 возведения в отрицательную степень подается значение λ, с выхода которого значение λ-1 поступает на первый вход третьего блока 2.3 умножения, значение L1 поступает на первый вход первого блока 2.1 умножения, значение q1 поступает на вход первого блока 3.1 формирования значения по модулю, второй вход первого блока 5.1 дифференцирования, первый вход второго блока 7.2 формирования разности и первый вход пятого блока 2.5 умножения, значение

На вход первого блока 1.1 возведения в отрицательную степень подается значение λ, с выхода которого значение λ-1 поступает на первый вход третьего блока 2.3 умножения, значение L1 поступает на первый вход первого блока 2.1 умножения, значение q1 поступает на вход первого блока 3.1 формирования значения по модулю, второй вход первого блока 5.1 дифференцирования, первый вход второго блока 7.2 формирования разности и первый вход пятого блока 2.5 умножения, значение  с первого выхода первого блока 3.1 формирования значения по модулю поступает на второй вход первого блока 2.1 умножения, с выхода которого значение

с первого выхода первого блока 3.1 формирования значения по модулю поступает на второй вход первого блока 2.1 умножения, с выхода которого значение  поступает на первый вход первого блока 4.1 формирования деления, со второго выхода значение

поступает на первый вход первого блока 4.1 формирования деления, со второго выхода значение  поступает на первый вход первого блока 5.1 дифференцирования, с первого выхода которого значение

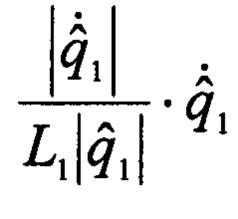

поступает на первый вход первого блока 5.1 дифференцирования, с первого выхода которого значение  поступает на второй вход первого блока 4.1 формирования деления, с выхода которого значение

поступает на второй вход первого блока 4.1 формирования деления, с выхода которого значение  поступает на первый вход второго блока 2.2 умножения, со второго выхода первого блока 5.1 дифференцирования значение

поступает на первый вход второго блока 2.2 умножения, со второго выхода первого блока 5.1 дифференцирования значение  поступает на второй вход второго блока 2.2 умножения, с выхода которого значение

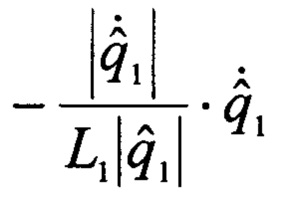

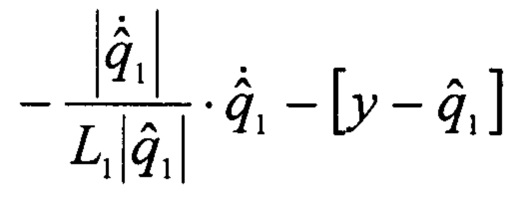

поступает на второй вход второго блока 2.2 умножения, с выхода которого значение  поступает на вход первого блока 6.1 формирования отрицания, с выхода которого значение

поступает на вход первого блока 6.1 формирования отрицания, с выхода которого значение  поступает на первый вход первого блока 7.1 формирования разности, с третьего выхода первого блока 5.1 дифференцирования значение

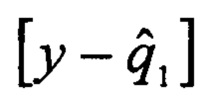

поступает на первый вход первого блока 7.1 формирования разности, с третьего выхода первого блока 5.1 дифференцирования значение  поступает на первый вход четвертого блока 2.4 умножения, значение у подается на первый вход второго блока 7.2 формирования разности, с выхода которого, значение

поступает на первый вход четвертого блока 2.4 умножения, значение у подается на первый вход второго блока 7.2 формирования разности, с выхода которого, значение  подается на второй вход первого блока 7.1 формирования разности, с выхода которого значение

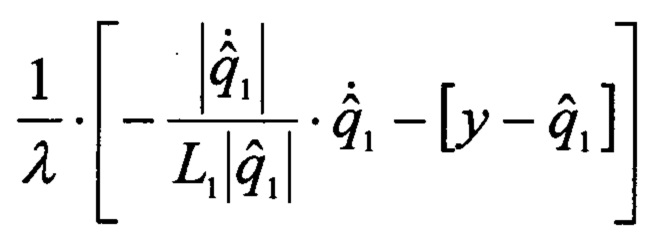

подается на второй вход первого блока 7.1 формирования разности, с выхода которого значение  подается на второй вход третьего блока 2.3 умножения, с выхода которого значение

подается на второй вход третьего блока 2.3 умножения, с выхода которого значение  подается на второй вход третьего блока 7.3 формирования разности, значение

подается на второй вход третьего блока 7.3 формирования разности, значение  поступает на второй вход четвертого блока 2.4 умножения с выхода которого значение

поступает на второй вход четвертого блока 2.4 умножения с выхода которого значение  поступает на первый вход третьего блока 7.3 формирования разности, с выхода которого значение

поступает на первый вход третьего блока 7.3 формирования разности, с выхода которого значение  поступает на второй вход четвертого блока 7.4 формирования разности, значение

поступает на второй вход четвертого блока 7.4 формирования разности, значение  поступает на второй вход пятого блока 2.5 умножения, с выхода которого значение

поступает на второй вход пятого блока 2.5 умножения, с выхода которого значение  поступает на первый вход четвертого блока 7.4 формирования разности, на выходе которого формируется значение

поступает на первый вход четвертого блока 7.4 формирования разности, на выходе которого формируется значение

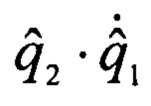

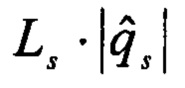

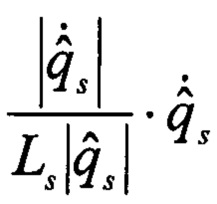

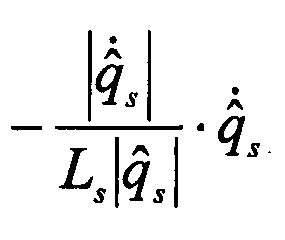

В исходном состоянии на входы устройства (фиг. 2) подаются: λ, as, Ls, у,  Gs. На первый вход шестого блока 2.6 умножения подается значение λ, на второй вход этого же блока подается значение as, с выхода которого значение λ⋅as поступает на вход второго блока 1.2 возведения в отрицательную степень, с выхода которого значение

Gs. На первый вход шестого блока 2.6 умножения подается значение λ, на второй вход этого же блока подается значение as, с выхода которого значение λ⋅as поступает на вход второго блока 1.2 возведения в отрицательную степень, с выхода которого значение  поступает на первый вход девятого блока 2.9 умножения, значение Ls поступает на первый вход седьмого блока 2.7 умножения, значение

поступает на первый вход девятого блока 2.9 умножения, значение Ls поступает на первый вход седьмого блока 2.7 умножения, значение поступает на второй вход второго блока 3.2 формирования значения по модулю и на второй вход второго блока 5.2 дифференцирования, значение

поступает на второй вход второго блока 3.2 формирования значения по модулю и на второй вход второго блока 5.2 дифференцирования, значение  подается с первого выхода блока 3.2 формирования значения по модулю на второй вход седьмого блока 2.7 умножения и со второго выхода этого же блока на первый вход второго блока 5.2 дифференцирования, с первого выхода которого значение

подается с первого выхода блока 3.2 формирования значения по модулю на второй вход седьмого блока 2.7 умножения и со второго выхода этого же блока на первый вход второго блока 5.2 дифференцирования, с первого выхода которого значение  подается на второй вход второго блока 4.2 формирования деления и со второго его выхода подается на второй вход восьмого блока 2.8 умножения, значение

подается на второй вход второго блока 4.2 формирования деления и со второго его выхода подается на второй вход восьмого блока 2.8 умножения, значение  с выхода седьмого блока 2.7 умножения подается на первый вход второго блока 4.2 формирования деления, с выхода которого значение

с выхода седьмого блока 2.7 умножения подается на первый вход второго блока 4.2 формирования деления, с выхода которого значение  подается на первый вход восьмого 2.8 блока умножения, с выхода которого значение

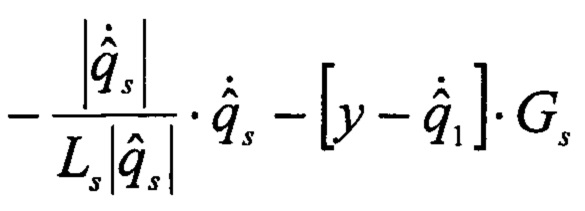

подается на первый вход восьмого 2.8 блока умножения, с выхода которого значение  поступает на вход второго блока 6.2 формирования отрицания, с выхода которого значение

поступает на вход второго блока 6.2 формирования отрицания, с выхода которого значение  подается на первый вход пятого блока 7.5 формирования разности, значение q1 поступает на вход третьего блока 5.3 дифференцирования, с выхода которого значение

подается на первый вход пятого блока 7.5 формирования разности, значение q1 поступает на вход третьего блока 5.3 дифференцирования, с выхода которого значение  подается на первый вход шестого блока 7.6 формирования разности, на второй вход которого подается значение y, с выхода которого значение

подается на первый вход шестого блока 7.6 формирования разности, на второй вход которого подается значение y, с выхода которого значение  поступает на первый вход десятого блока 2.10 умножения, на второй вход которого поступает значение Gs, значение

поступает на первый вход десятого блока 2.10 умножения, на второй вход которого поступает значение Gs, значение  с выхода десятого блока 2.10 умножения подается на второй вход пятого блока 7.5 формирования разности, с выхода которого значение

с выхода десятого блока 2.10 умножения подается на второй вход пятого блока 7.5 формирования разности, с выхода которого значение  подается на второй вход девятого блока 2.9 умножения, на выходе которого формируется значение

подается на второй вход девятого блока 2.9 умножения, на выходе которого формируется значение

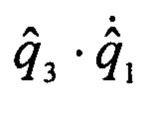

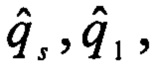

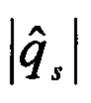

В исходном состоянии на входы устройства (фиг. 3) подаются: G2,

G2,  На первый вход одиннадцатого блока 2.11 умножения подается значение

На первый вход одиннадцатого блока 2.11 умножения подается значение  на второй вход этого же блока поступает значение G2, значение

на второй вход этого же блока поступает значение G2, значение  с выхода одиннадцатого блока 2.11 умножения поступает на второй вход седьмого блока 7.7 формирования разности, значение G2 поступает на вход четвертого блока 5.4 дифференцирования, с выхода которого значение

с выхода одиннадцатого блока 2.11 умножения поступает на второй вход седьмого блока 7.7 формирования разности, значение G2 поступает на вход четвертого блока 5.4 дифференцирования, с выхода которого значение  поступает на второй вход двенадцатого блока 2.12 умножения, значение

поступает на второй вход двенадцатого блока 2.12 умножения, значение  поступает на вход третьего блока 6.3 формирования отрицания, с выхода которого значение

поступает на вход третьего блока 6.3 формирования отрицания, с выхода которого значение  поступает на первый вход двенадцатого блока 2.12 умножения, с выхода которого значение

поступает на первый вход двенадцатого блока 2.12 умножения, с выхода которого значение  поступает на первый вход седьмого блока 7.7 формирования разности, с выхода которого значение

поступает на первый вход седьмого блока 7.7 формирования разности, с выхода которого значение  поступает на второй вход восьмого блока 7.8 формирования разности, значение

поступает на второй вход восьмого блока 7.8 формирования разности, значение  поступает на первый вход восьмого блока 7.8 формирования разности, на выходе которого формируется значение

поступает на первый вход восьмого блока 7.8 формирования разности, на выходе которого формируется значение

В исходном состоянии на входы устройства (фиг. 4) подаются:  G3,

G3,  На первый вход тринадацатого блока 2.13 умножения подается значение

На первый вход тринадацатого блока 2.13 умножения подается значение  на второй вход этого же блока поступает значение G3, значение

на второй вход этого же блока поступает значение G3, значение  с выхода тринадацатого блока 2.13 умножения, поступает на второй вход девятого блока 7.9 формирования разности, значение G3 поступает на вход пятого блока 5.5 дифференцирования, с выхода которого значение

с выхода тринадацатого блока 2.13 умножения, поступает на второй вход девятого блока 7.9 формирования разности, значение G3 поступает на вход пятого блока 5.5 дифференцирования, с выхода которого значение  поступает на второй вход четырнадцатого блока 2.14 умножения, значение

поступает на второй вход четырнадцатого блока 2.14 умножения, значение  поступает на вход четвертого блока 6.4 формирования отрицания, с выхода которого значение

поступает на вход четвертого блока 6.4 формирования отрицания, с выхода которого значение  поступает на первый вход четырнадцатого блока 2.14 умножения, с выхода которого значение

поступает на первый вход четырнадцатого блока 2.14 умножения, с выхода которого значение  поступает на первый вход девятого блока 7.9 формирования разности, с выхода которого значение

поступает на первый вход девятого блока 7.9 формирования разности, с выхода которого значение  поступает на второй вход десятого блока 7.10 формирования разности, значение

поступает на второй вход десятого блока 7.10 формирования разности, значение  поступает на первый вход десятого блока 7.10 формирования разности, на выходе которого формируется значение

поступает на первый вход десятого блока 7.10 формирования разности, на выходе которого формируется значение

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Сейдж Э.П., Меле Д.Л. Идентификация систем управления. М.: Наука, 1974. с. 204-212.

2. Патент RU №2528133 от 16.07.2014 г. Устройство идентификации Лагранжевых динамических систем на основе итерационной регуляризации. Авторы: Андрашитов Д.С., Костоглотов А.А.

3. Андрашитов Д.С., Костоглотов А.А., Лазаренко С.В., Пугачев И.В. Вариационный метод идентификации адаптивных динамических систем с построением дополнительных инвариантов // Информационно-измерительные и управляющие системы, 2016 г., Т. 14, №11, С. 55-63.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство идентификации параметров динамических звеньев информационно-управляющих систем | 2014 |

|

RU2632681C2 |

| ИНФОРМАЦИОННАЯ СИСТЕМА ПОСАДКИ | 1992 |

|

RU2023984C1 |

| Устройство идентификации параметров передаточной характеристики MEMS-акселерометра | 2021 |

|

RU2767012C1 |

| УСТРОЙСТВО ИДЕНТИФИКАЦИИ ПАРАМЕТРОВ ДИНАМИЧЕСКИХ СИСТЕМ НА ОСНОВЕ ВАРИАЦИОННЫХ ПРИНЦИПОВ | 2011 |

|

RU2464615C1 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| УСТРОЙСТВО ДЛЯ ВЕСОВОГО ДОЗИРОВАНИЯ ВЕЩЕСТВ, ПОДЛЕЖАЩИХ СМЕШИВАНИЮ | 1986 |

|

SU1387608A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| КОМПЛЕКСНАЯ СИСТЕМА НАВИГАЦИИ | 1992 |

|

RU2023983C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

Изобретение относится к области цифровой вычислительной техники. Технический результат заключается в повышении точности коррекции динамической погрешности измерительных систем. Технический результат достигается за счет устройства оценки параметров возмущенных процессов с использованием максимума обобщенной мощности, которое содержит первый и второй блоки возведения в отрицательную степень; первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый блоки умножения; первый и второй блоки формирования значения по модулю; первый и второй блоки формирования деления; первый, второй, третий, четвертый и пятый блоки дифференцирования; первый, второй, третий и четвертый блоки формирования отрицания; первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый блоки формирования разности. 4 ил.

Устройство оценки параметров возмущенных процессов с использованием максимума обобщенной мощности, содержащее первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый блоки умножения; первый, второй и третий блоки формирования разности, при этом входы первого блока возведения в отрицательную степень, первого блока умножения, четвертого блока умножения, пятого блока умножения, первого блока формирования значения по модулю, первого блока дифференцирования, второго блока формирования разности, шестого блока умножения, седьмого блока умножения, десятого блока умножения, второго блока формирования значения по модулю, второго блока дифференцирования, третьего блока дифференцирования, шестого блока формирования разности, одиннадцатого блока умножения, четвертого блока дифференцирования, третьего блока формирования отрицания, восьмого блока формирования разности, тринадцатого блока умножения, пятого блока дифференцирования, четвертого блока формирования отрицания, десятого блока формирования разности являются входами устройства, а выходы четвертого блока формирования разности, девятого блока умножения, восьмого блока формирования разности, десятого блока формирования разности являются соответственно первым, вторым, третьим и четвертым выходами устройства, которое отличающееся тем, что в устройство введены первый и второй блоки возведения в отрицательную степень, первый и второй блоки формирования значения по модулю, первый и второй блоки формирования деления, первый, второй, третий, четвертый и пятый блоки дифференцирования, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый блоки формирования отрицания, причем выход первого блока возведения в отрицательную степень соединен с первым входом третьего блока умножения, первый выход первого блока формирования значения по модулю соединен со вторым входом первого блока умножения, выход первого блока умножения соединен с первым входом первого блока формирования деления, второй выход первого блока формирования значения по модулю соединен с первым входом первого блока дифференцирования, первый выход которого соединен со вторым входом первого блока формирования деления, при этом выход первого блока формирования деления соединен с первым входом второго блока умножения, второй выход первого блока дифференцирования соединен со вторым входом второго блока умножения, выход второго блока умножения соединен с входом первого блока формирования отрицания, выход которого соединен с первым входом первого блока формирования разности, выход второго блока формирования разности соединен со вторым входом первого блока формирования разности, выход которого соединен со вторым входом третьего блока умножения, выход которого соединен со вторым входом третьего блока формирования разности, третий выход первого блока дифференцирования соединен с входом четвертого блока умножения, выход которого соединен с первым входом третьего блока формирования разности, выход которого соединен со вторым входом четвертого блока формирования разности, выход пятого блока умножения соединен с первым входом четвертого блока формирования разности, выход шестого блока умножения соединен с входом второго блока возведения в отрицательную степень, выход которого соединен с первым входом девятого блока умножения, первый выход второго блока формирования значения по модулю соединен со вторым входом седьмого блока умножения, выход которого соединен с первым входом второго блока формирования деления, второй выход второго блока формирования значения по модулю соединен с первым входом второго блока дифференцирования, первый выход которого соединен со вторым входом второго блока формирования деления, выход которого соединен с первым входом восьмого блока умножения, второй выход второго блока дифференцирования соединен со вторым входом восьмого блока умножения, выход которого соединен с входом второго блока формирования отрицания, выход которого соединен с первым входом пятого блока формирования разности, выход третьего блока дифференцирования соединен с первым входом шестого блока формирования разности, выход которого соединен с первым входом десятого блока умножения, выход которого соединен со вторым входом пятого блока формирования разности, выход которого соединен со вторым входом девятого блока умножения, выход одиннадцатого блока умножения соединен со вторым входом седьмого блока формирования разности, выход четвертого блока дифференцирования соединен со вторым входом двенадцатого блока умножения, выход третьего блока формирования отрицания соединен с первым входом двенадцатого блока умножения, выход которого соединен с первым входом седьмого блока формирования разности, выход которого соединен со вторым входом восьмого блока формирования разности, выход тринадцатого блока умножения соединен со вторым входом девятого блока формирования разности, выход пятого блока дифференцирования соединен со вторым входом четырнадцатого блока умножения, выход четвертого блока формирования отрицания соединен с первым входом четырнадцатого блока умножения, выход которого соединен с первым входом блока девятого блока формирования разности, выход которого соединен со вторым входом десятого блока формирования разности.

| ОЦЕНКА ПАРАМЕТРОВ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ПРОЦЕССОМ В ЗАДАННЫХ СЕГМЕНТАХ ПЕРЕМЕЩЕНИЯ | 2009 |

|

RU2483340C2 |

| СПОСОБ ОПЕРАТИВНОГО ДИНАМИЧЕСКОГО АНАЛИЗА НЕЧЕТКОГО СОСТОЯНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ОБЪЕКТА ИЛИ ПРОЦЕССА | 1999 |

|

RU2156496C1 |

| Устройство оценки параметров с использованием априорной информации в форме интеграла действия | 2016 |

|

RU2657477C1 |

| СПОСОБ КОМПЛЕКСНОГО КОНТРОЛЯ СОСТОЯНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ОБЪЕКТА ПО РАЗНОРОДНОЙ ИНФОРМАЦИИ | 2011 |

|

RU2459245C1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

Авторы

Даты

2020-02-07—Публикация

2019-04-05—Подача