Предлагаемое изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.), работающих в условиях низких температур и воздействия радиации.

В современной микроэлектронике достаточно перспективны архитектуры операционных усилителей (ОУ) на основе полевых транзисторов с управляющим p-n переходом (JFET) и КМОП транзисторов [1-12].

Ближайшим прототипом заявляемого устройства является операционный усилитель [1] на комплементарных полевых транзисторах с управляющим p-n переходом, представленный в статье фирмы Linear Integrated System (микросхемы LSK489/LSJ689; Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17, США). Он содержит первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, затворы которых соединены с первым 1 входом устройства, третий 6 и четвертый 7 входные полевые транзисторы, затворы которых подключены ко второму 2 входу устройства, первый 8 выходной полевой транзистор, затвор которого соединен с первым 9 источником напряжения смещения, сток связан с токовым выходом 3 устройства, а исток подключён к первой 10 шине источника питания через первый 11 токостабилизирующий двухполюсник и соединен со стоком третьего 6 входного полевого транзистора, второй 12 выходной полевой транзистор, затвор которого соединен со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток связан со второй 14 шиной источника питания через второй 15 токостабилизирующий двухполюсник и соединен со стоком четвертого 7 входного полевого транзистора, причем сток первого 4 входного полевого транзистора связан с первой 10 шиной источника питания, а сток второго 5 входного полевого транзистора связан со второй 14 шиной источника питания.

Существенный недостаток ОУ-прототипа состоит в том, что в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенные значения коэффициента усиления по напряжению (К0).

Основная задача предлагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного JFet операционного усилителя, который обеспечивает малый уровень систематической составляющей напряжения смещения нуля и повышенные значения коэффициента усиления по напряжению, а также КМОП ОУ.

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащем первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, затворы которых соединены с первым 1 входом устройства, третий 6 и четвертый 7 входные полевые транзисторы, затворы которых подключены ко второму 2 входу устройства, первый 8 выходной полевой транзистор, затвор которого соединен с первым 9 источником напряжения смещения, сток связан с токовым выходом 3 устройства, а исток подключён к первой 10 шине источника питания через первый 11 токостабилизирующий двухполюсник и соединен со стоком третьего 6 входного полевого транзистора, второй 12 выходной полевой транзистор, затвор которого соединен со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток связан со второй 14 шиной источника питания через второй 15 токостабилизирующий двухполюсник и соединен со стоком четвертого 7 входного полевого транзистора, причем сток первого 4 входного полевого транзистора связан с первой 10 шиной источника питания, а сток второго 5 входного полевого транзистора связан со второй 14 шиной источника питания, предусмотрены новые элементы и связи – между объединенными истоками первого 4 и третьего 6 входных полевых транзисторов и второй 14 шиной источника питания включен третий 16 токостабилизирующий двухполюсник на полевом транзисторе, между объединенными истоками второго 5 и четвертого 7 входных полевых транзисторов и первой 10 шиной источника питания включен четвертый 17 токостабилизирующий двухполюсник на полевом транзисторе, причем выходные статические токи первого 11, второго 15, третьего 16 и четвертого 17 токостабилизирующих двухполюсников одинаковы в широком диапазоне внешних воздействий и изменении напряжений питания.

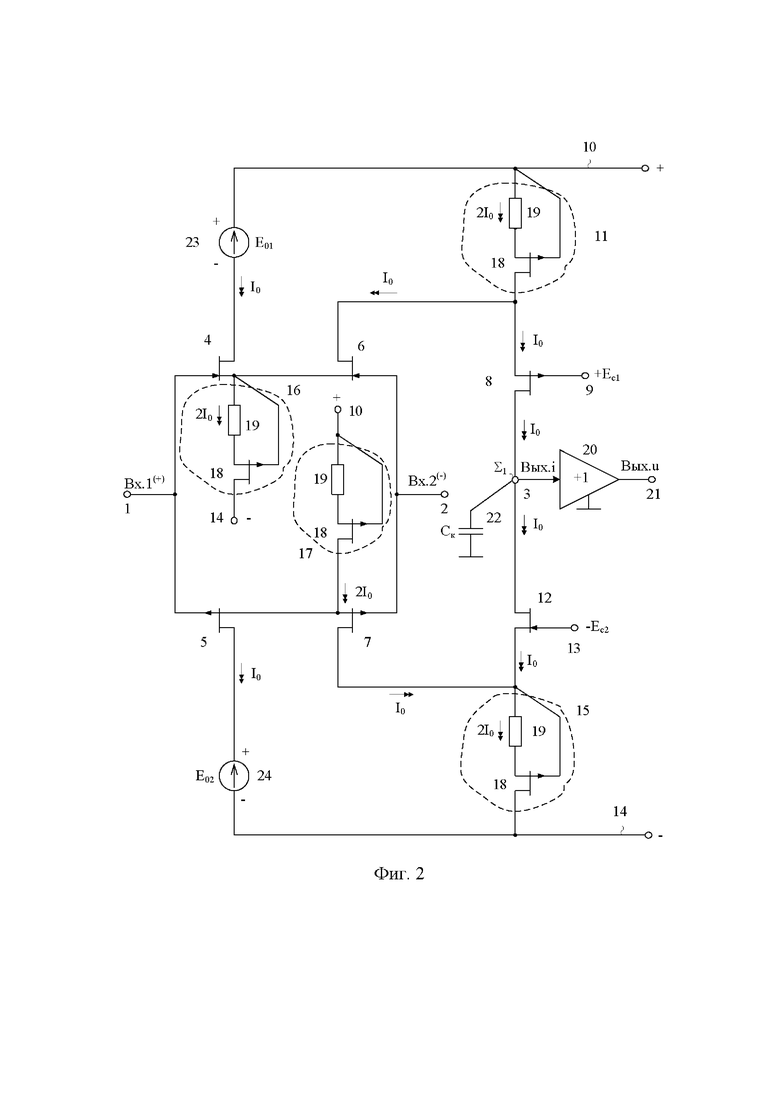

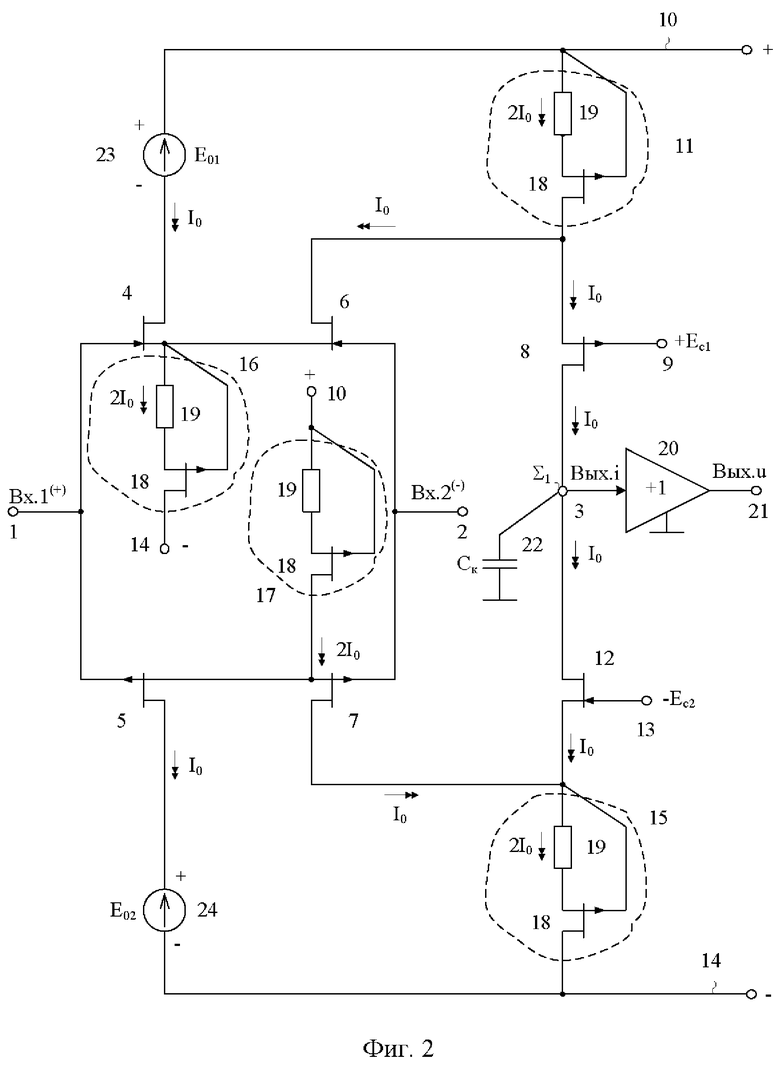

На чертеже фиг. 1 представлена схема ОУ-прототипа, опубликованного в [1], а на чертеже фиг. 2 – схема заявляемого ОУ в соответствии с пп. 1, 2, 3, 4 формулы изобретения.

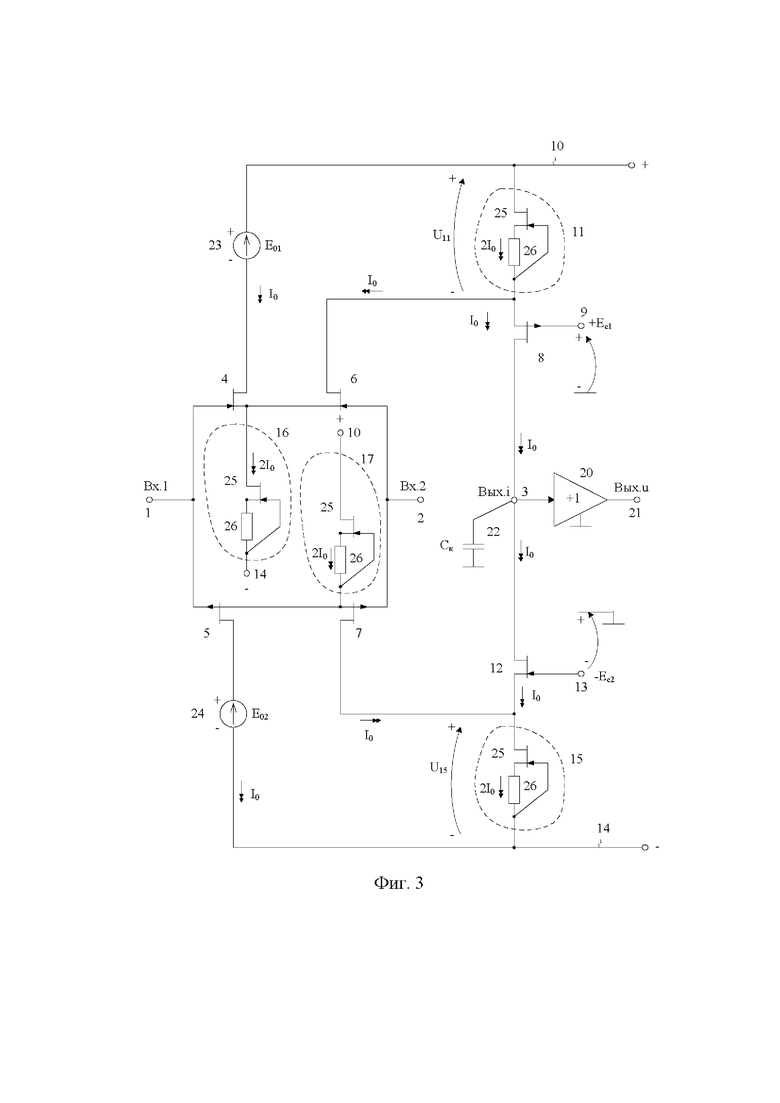

На чертеже фиг. 3 показана схема заявляемого ОУ фиг. 2 в соответствии с пп. 5 и 6 формулы изобретения.

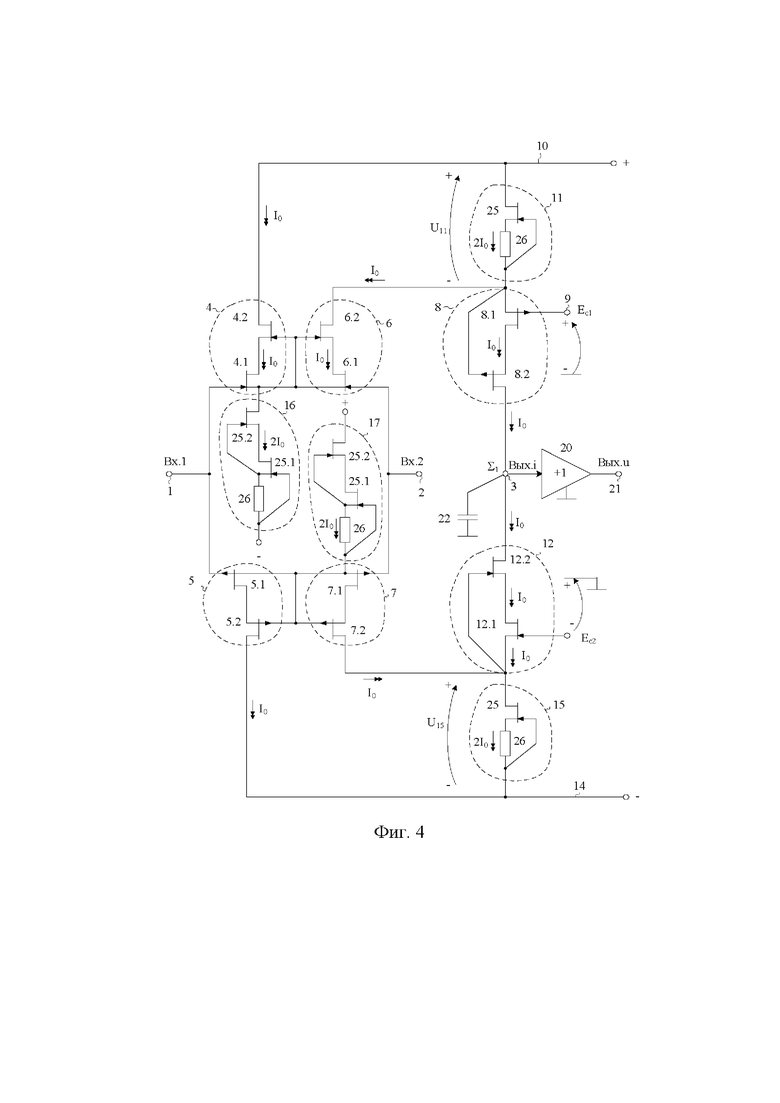

На чертеже фиг. 4 показан пример построения заявляемого операционного усилителя фиг. 2 для случая, когда первый 8 и второй 12 выходные полевые транзисторы, первый 4, третий 6, второй 5 и четвертый 7 входные полевые транзисторы, а также полевые транзисторы в структуре третьего 16 и четвертого 17 токостабилизирующих двухполюсников реализованы как каскодные составные транзисторы. При этом в данной схеме возможны и другие (разные) сочетания каскодных и некаскодных полевых транзисторов.

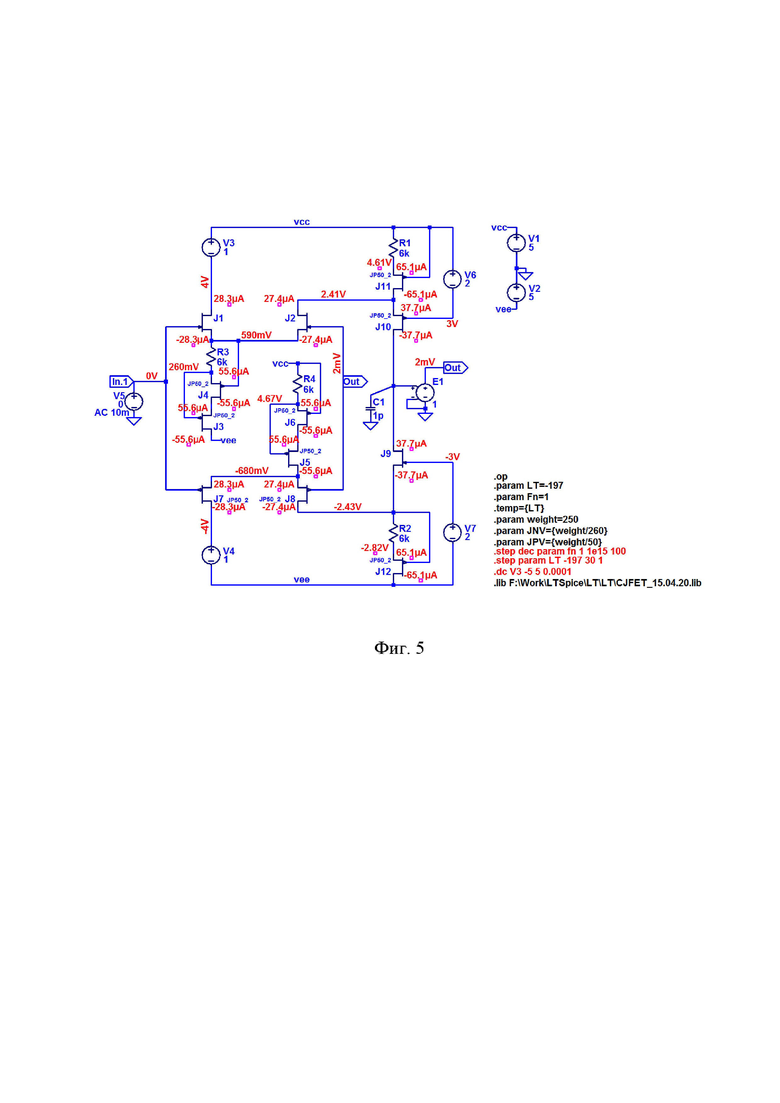

На чертеже фиг. 5 приведена схема заявляемого ОУ фиг. 2 спроектированного в программной среде LTSpice (Analog Device, США) на комплементарных полевых транзисторах с управляющим pn-переходом (CJFET, «Интеграл», г. Минск, Беларусь) при напряжении питания ± 5 В, температуре -197ºС и микроамперных статических токах JFET (28-65 мкА).

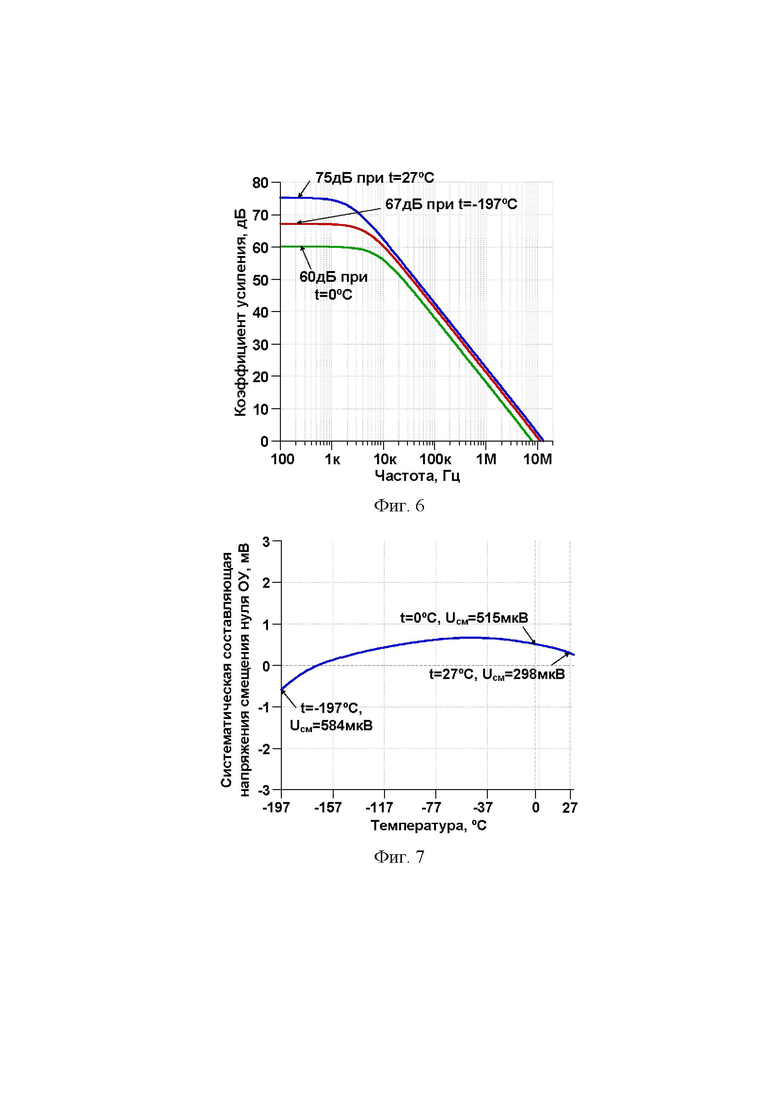

На чертеже фиг. 6 представлено компьютерное моделирование логарифмической амплитудно-частотной характеристики (ЛАЧХ) ОУ фиг. 5, где разомкнутый коэффициент усиления (К0) измерялся при t=0ºC; 27ºC; -197ºC.

На чертеже фиг. 7 приведена зависимость систематической составляющей напряжения смещения нуля ОУ рис. 5 от температуры в диапазоне от -197°C до 30°C.

Операционный усилитель на комплементарных полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы устройства, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, затворы которых соединены с первым 1 входом устройства, третий 6 и четвертый 7 входные полевые транзисторы, затворы которых подключены ко второму 2 входу устройства, первый 8 выходной полевой транзистор, затвор которого соединен с первым 9 источником напряжения смещения, сток связан с токовым выходом 3 устройства, а исток подключён к первой 10 шине источника питания через первый 11 токостабилизирующий двухполюсник и соединен со стоком третьего 6 входного полевого транзистора, второй 12 выходной полевой транзистор, затвор которого соединен со вторым 13 источником напряжения смещения, сток подключен к токовому выходу 3 устройства, а исток связан со второй 14 шиной источника питания через второй 15 токостабилизирующий двухполюсник и соединен со стоком четвертого 7 входного полевого транзистора, причем сток первого 4 входного полевого транзистора связан с первой 10 шиной источника питания, а сток второго 5 входного полевого транзистора связан со второй 14 шиной источника питания. Между объединенными истоками первого 4 и третьего 6 входных полевых транзисторов и второй 14 шиной источника питания включен третий 16 токостабилизирующий двухполюсник на полевом транзисторе, между объединенными истоками второго 5 и четвертого 7 входных полевых транзисторов и первой 10 шиной источника питания включен четвертый 17 токостабилизирующий двухполюсник на полевом транзисторе, причем выходные статические токи первого 11, второго 15, третьего 16 и четвертого 17 токостабилизирующих двухполюсников одинаковы в широком диапазоне внешних воздействий и изменении напряжений питания.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, тип канала полевых транзисторов в структуре первого 11, второго 15, третьего 16 и четвертого 17 токостабилизирующих двухполюсников соответствует типу канала второго 5 и четвертого 7 входных полевых транзисторов, а также первого 8 выходного полевого транзистора.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, первый 11, второй 15, третий 16 и четвертый 17 токостабилизирующие двухполюсники выполнены по идентичным схемам, каждая из которых содержит первый 18 вспомогательный полевой транзистор, между затвором и истоком которого включен первый 19 вспомогательный резистор.

На чертеже фиг. 2, в соответствии с п. 4 формулы изобретения, токовый выход устройства 3 связан со входом буферного усилителя 20, выход которого является потенциальным выходом устройства 21.

На чертеже фиг. 3, в соответствии с п. 5 формулы изобретения, тип канала полевых транзисторов в структуре первого 11, второго 15, третьего 16 и четвертого 17 токостабилизирующих двухполюсников соответствует типу канала первого 4 и третьего 6 входных полевых транзисторов, а также второго 12 выходного полевого транзистора.

Кроме того, на чертеже фиг. 3, в соответствии с п. 6 формулы изобретения, первый 11, второй 15, третий 16 и четвертый 17 токостабилизирующие двухполюсники выполнены по идентичным схемам, каждая из которых содержит второй 25 вспомогательный полевой транзистор, между затвором и истоком которого включен второй 26 вспомогательный резистор.

На чертеже фиг. 4, который характеризует направление дальнейшего совершенствования схемы заявляемого ОУ, первый 4 входной полевой транзистор является составным и содержит первый 4.1 и второй 4.2 дополнительные полевые транзисторы, второй 5 входной полевой транзистор является составным и содержит третий 5.1 и четвертый 5.2 дополнительные полевые транзисторы, третий 6 входной полевой транзистор является составным и содержит пятый 6.1 и шестой 6.2 дополнительные полевые транзисторы, четвертый 7 входной полевой транзистор является составным и содержит седьмой 7.1 и восьмой 7.2 дополнительные полевые транзисторы, второй 25 вспомогательный полевой транзистор третьего 16 токостабилизирующего двухполюсника является составным и содержит девятый 25.1 и десятый 25.2 дополнительные полевые транзисторы, второй 25 вспомогательный полевой транзистор четвертого 17 токостабилизирующего двухполюсника является составным и содержит девятый 25.1 и десятый 25.2 дополнительные полевые транзисторы, первый 8 выходной полевой транзистор является составным и содержит одиннадцатый 8.1 и двенадцатый 8.2 дополнительные полевые транзисторы, второй 12 выходной полевой транзистор является составным и содержит тринадцатый 12.1 и четырнадцатый 12.2 дополнительные полевые транзисторы. При этом возможно и другое сочетание каскодных и некаскодных транзисторов в схеме фиг. 4.

На чертежах фиг. 1 - фиг. 4 конденсатор Ск обеспечивает коррекцию амплитудно-частотной характеристики ОУ.

Рассмотрим работу предлагаемого ОУ фиг. 2 в сравнении с ОУ-прототипом фиг. 1.

Для достижения заявляемого эффекта в схеме фиг. 2 предусмотрено применение специальных элементов стабилизации статического режима – третьего 16 и четвертого 17 токостабилизирующих двухполюсников, выполненных по идентичным схемам, каждая из которых содержит первый 18 вспомогательный полевой транзистор, между затвором и истоком котором включен первый 19 вспомогательный резистор. Таким образом, в заявляемой схеме фиг. 2 реализуется высокая идентичность токов в элементах стабилизации статического режима - третьего 16 и четвертого 17 токостабилизирующих двухполюсников, а также токов первого 11 и второго 15 токостабилизирующих двухполюсников. Это является важным условием получения малых значений систематической составляющей напряжения смещения нуля (Uсм) ОУ. Данный вывод подтверждается результатами компьютерного моделирования на чертеже фиг. 7, который показывает, что Uсм в заявляемой модификации ОУ лежит в диапазоне десятков микровольт, что недостижимо в ОУ-прототипе фиг. 1 без технологической или внешней балансировки Uсм.

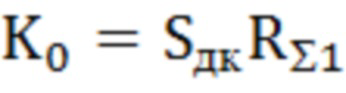

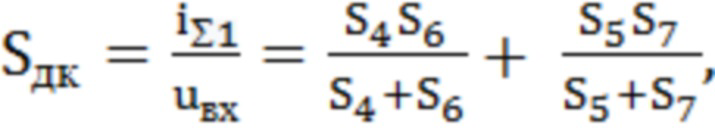

Кроме этого, реализация первого 11 и второго 15 токостабилизирующих двухполюсников по идентичным схемам на первом 18 вспомогательном полевом транзисторе существенно повышает коэффициент усиления (К0) по напряжению ОУ фиг.2, так как

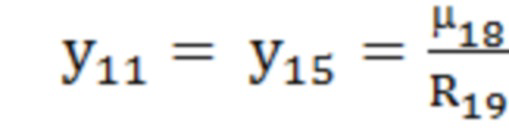

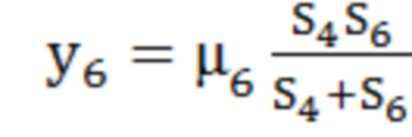

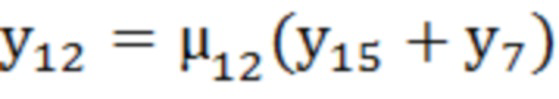

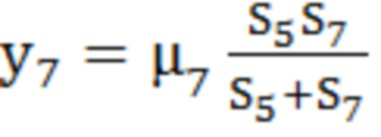

, (1)

, (1)

где RΣ1 – эквивалентное сопротивление высокоимпедансного узла Σ1,  – эквивалентная крутизна преобразования входного дифференциального напряжения uвх ОУ фиг.2 в выходной ток iΣ1 высокоимпендасного узла Σ1:

– эквивалентная крутизна преобразования входного дифференциального напряжения uвх ОУ фиг.2 в выходной ток iΣ1 высокоимпендасного узла Σ1:

(2)

(2)

где  – крутизна стоко-затворной характеристики i-го полевого транзистора.

– крутизна стоко-затворной характеристики i-го полевого транзистора.

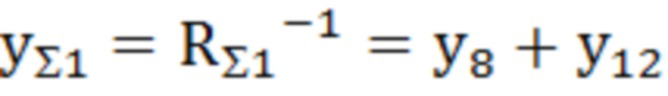

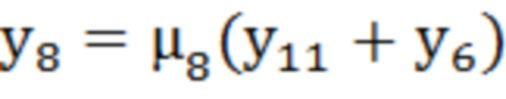

Причем проводимость, обратная выходному сопротивлению RΣ1, определяется формулами:

, (3)

, (3)

, (4)

, (4)

, (5)

, (5)

, (6)

, (6)

, (7)

, (7)

, (8)

, (8)

В формулах (4)÷(8) принято, что параметр μi – это коэффициент внутренней обратной связи полевых транзисторов, характеризующий влияние изменений напряжения сток-затвор на напряжение затвор-исток (эффект модуляции длинны канала) при постоянном токе истока.

Из последних уравнений (3)÷(8) следует, что в предлагаемой схеме ОУ коэффициент К0 существенно возрастает за счет увеличения второго сомножителя в формуле (1) – эквивалентного сопротивления RΣ1. Данный вывод подтверждается результатами моделирования на чертеже фиг. 6, который показывает, что заявляемый ОУ в микромощном исполнении и имеющий один высокоимпедансный узел Σ1, характеризуется высокими значениями К0=60÷75 дБ. Это достаточно для многих применений ОУ в аналоговых интерфейсах.

Дальнейшая минимизация основных составляющих Uсм ОУ фиг.2 связана с введением первой 23 и второй 24 цепей согласования потенциалов, которые предназначены для симметрирования статических напряжений затвор-исток первого 4 и третьего 6 входных полевых транзисторов, а так же соответственно второго 5 и четвертого 7 входных полевых транзисторов. Данное схемотехническое решение позволяет уменьшить влияние эффекта модуляции длины канала первого 4 и третьего 6 входных полевых транзисторов (второго 5 и четвертого 7 входных полевых транзисторов) на смещение их стоко-затворных характеристик и, в конечном итоге, уменьшает вторую составляющую Uсм, обусловленную влиянием коэффициента внутренней обратной связи μ. Причем, в предлагаемых схемах ОУ, из-за разных напряжений затвор-исток JFet с p-каналом (первый 8 выходной полевой транзистор) и n-каналом (второй 12 выходной полевой транзистор) должно соблюдаться неравенство Eс1≠ Eс2.

Представленный на чертеже фиг. 4 схемотехнический прием (выполнение первого 4, второго 5, третьего 6 и четвертого 7 входных полевых транзисторов в виде составных транзисторов) обеспечивает «автоматическое» симметрирование статических режимов первого 4 и третьего 6 входных полевых транзисторов, а также второго 5 и четвертого 7 входных полевых транзисторов по напряжению затвор-сток в широком диапазоне температур и радиационных воздействий. Поэтому данную схему следует использовать для получения экстремально малых значений Uсм в тяжелых условиях эксплуатации ОУ.

Каскодное построение первого 8 и второго 12 выходных полевых транзисторов положительно сказывается на величине разомкнутого коэффициента усиления по напряжению в ОУ фиг. 4.

Рассмотренные схемы ОУ работоспособны на КМОП транзисторах со встроенным каналом. Для этого необходимо вместо JFET транзисторов схемы фиг. 2 (фиг. 3) использовать соответствующие КМОП транзисторы. При этом основные свойства ОУ в данном элементом базисе сохраняются.

Таким образом, заявляемое устройство имеет (в сравнении с ОУ-прототипом [1] на известных серийных микросхемах LSJ689, LSK489 фирмы Linear Integrated Systems, США [13,14]) более высокие обобщенные показатели качества: улучшенные Uсм, К0, а также малый ток потребления в статическом режиме. За счет использования JFet обеспечивается высокая радиационная стойкость, криогенный диапазон температур и экстремально низкий уровень шумов.

Предлагаемый ОУ может быть рекомендован для практического использования в космическом приборостроении и физике высоких энергий.БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17. URL: http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf

2. V. Chumakov, et al. “Basic Modifications of “Floating” Differential Stages Based on Complementary Field-Effect Transistors with a Control p-n Junction,” Preprints 2021, 2021040276, DOI: 10.20944/preprints202104.0276.v1.

3. Патент US № 6600363, 2003 г.

4. Патент US № 7821333, 2010 г.

5. RU 2523124, 2013 г.

6. RU 2615066, 2015 г.

7. RU 2517699, 2012 г.

8. RU 2621287, 2017 г.

9. RU 2627094, 2017 г.

10. RU 2684473, 2019 г.

11. RU 2679970, 2019 г.

12. RU 2712414, 2019 г.

13. Bob Cordell, "Linear Systems LSJ689 Application Note", URL: http://www.linearsystems.com/lsdata/appnotes/LSJ689_P-Channel%20Dual%20JFETs.pdf

14. Bob Cordell, "LSK489 Application Note", URL: http://www.linearsystems.com/lsdata/others/LSK489_Application_Note.pdf.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С «ПЛАВАЮЩИМ» ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ КАСКАДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2741055C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770913C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2766864C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

Предлагаемое изобретение относится к области радиотехники и аналоговой микроэлектроники. Технический результат: создание радиационно-стойкого и низкотемпературного JFet операционного усилителя, который обеспечивает малый уровень систематической составляющей напряжения смещения нуля и повышенные значения коэффициента усиления по напряжению. Для этого в известный операционный усилитель на комплементарных полевых транзисторах между объединенными истоками первого (4) и третьего (6) входных полевых транзисторов и второй (14) шиной источника питания включен третий (16) токостабилизирующий двухполюсник на полевом транзисторе, между объединенными истоками второго (5) и четвертого (7) входных полевых транзисторов и первой (10) шиной источника питания включен четвертый (17) токостабилизирующий двухполюсник на полевом транзисторе, причем выходные статические токи первого (11), второго (15), третьего (16) и четвертого (17) токостабилизирующих двухполюсников одинаковы в широком диапазоне внешних воздействий и изменении напряжений питания. 5 з.п. ф-лы, 7 ил.

1. Операционный усилитель на комплементарных полевых транзисторах, содержащий первый (1) и второй (2) входы устройства, токовый выход (3) устройства, первый (4) и второй (5) входные полевые транзисторы, затворы которых соединены с первым (1) входом устройства, третий (6) и четвертый (7) входные полевые транзисторы, затворы которых подключены ко второму (2) входу устройства, первый (8) выходной полевой транзистор, затвор которого соединен с первым (9) источником напряжения смещения, сток связан с токовым выходом (3) устройства, а исток подключён к первой (10) шине источника питания через первый (11) токостабилизирующий двухполюсник и соединен со стоком третьего (6) входного полевого транзистора, второй (12) выходной полевой транзистор, затвор которого соединен со вторым (13) источником напряжения смещения, сток подключен к токовому выходу (3) устройства, а исток связан со второй (14) шиной источника питания через второй (15) токостабилизирующий двухполюсник и соединен со стоком четвертого (7) входного полевого транзистора, причем сток первого (4) входного полевого транзистора связан с первой (10) шиной источника питания, а сток второго (5) входного полевого транзистора связан со второй (14) шиной источника питания, отличающийся тем, что между объединенными истоками первого (4) и третьего (6) входных полевых транзисторов и второй (14) шиной источника питания включен третий (16) токостабилизирующий двухполюсник на полевом транзисторе, между объединенными истоками второго (5) и четвертого (7) входных полевых транзисторов и первой (10) шиной источника питания включен четвертый (17) токостабилизирующий двухполюсник на полевом транзисторе, причем выходные статические токи первого (11), второго (15), третьего (16) и четвертого (17) токостабилизирующих двухполюсников одинаковы в широком диапазоне внешних воздействий и изменении напряжений питания.

2. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что тип канала полевых транзисторов в структуре первого (11), второго (15), третьего (16) и четвертого (17) токостабилизирующих двухполюсников соответствует типу канала второго (5) и четвертого (7) входных полевых транзисторов, а также первого (8) выходного полевого транзистора.

3. Операционный усилитель на комплементарных полевых транзисторах по п. 2, отличающийся тем, что первый (11), второй (15), третий (16) и четвертый (17) токостабилизирующие двухполюсники выполнены по идентичным схемам, каждая из которых содержит первый (18) вспомогательный полевой транзистор, между затвором и истоком которого включен первый (19) вспомогательный резистор.

4. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что токовый выход устройства (3) связан со входом буферного усилителя (20), выход которого является потенциальным выходом устройства (21).

5. Операционный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что тип канала полевых транзисторов в структуре первого (11), второго (15), третьего (16) и четвертого (17) токостабилизирующих двухполюсников соответствует типу канала первого (4) и третьего (6) входных полевых транзисторов, а также второго (12) выходного полевого транзистора.

6. Операционный усилитель на комплементарных полевых транзисторах по п. 5, отличающийся тем, что первый (11), второй (15), третий (16) и четвертый (17) токостабилизирующие двухполюсники выполнены по идентичным схемам, каждая из которых содержит второй (25) вспомогательный полевой транзистор, между затвором и истоком которого включен второй (26) вспомогательный резистор.

| DIMITRI DANYUK "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf опубл | |||

| Токарный резец | 1924 |

|

SU2016A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412540C1 |

| US 5512857 A1, 30.04.1996. | |||

Авторы

Даты

2022-04-25—Публикация

2021-10-07—Подача