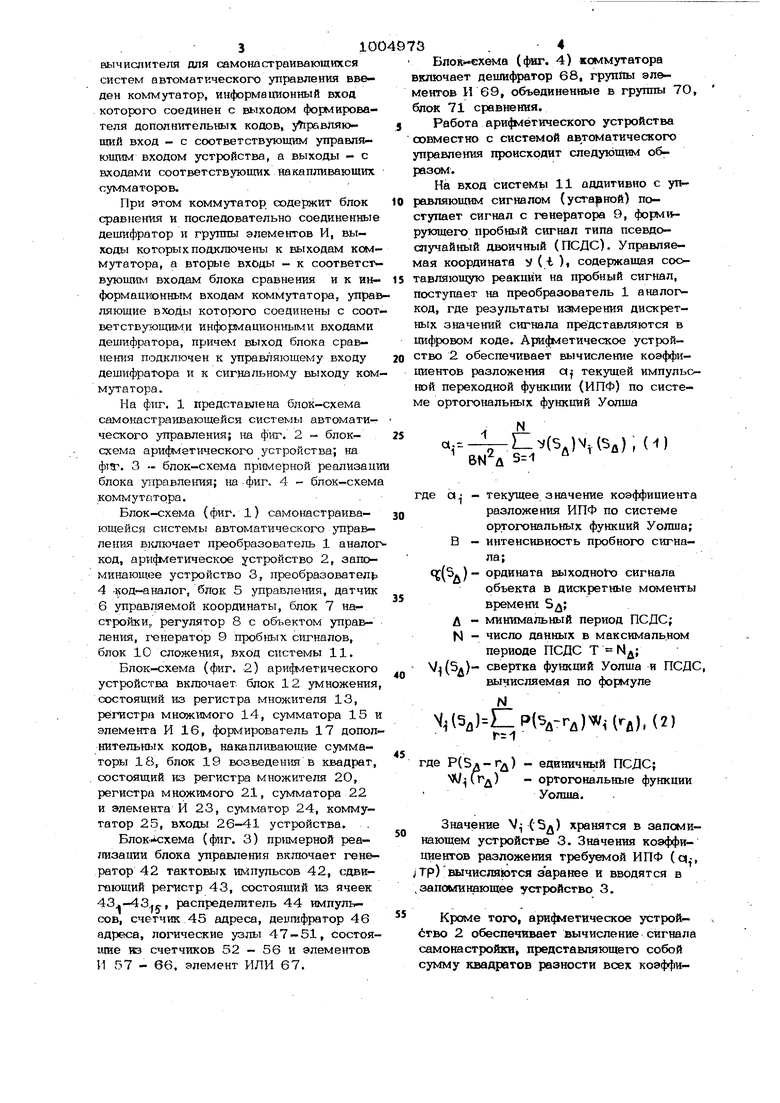

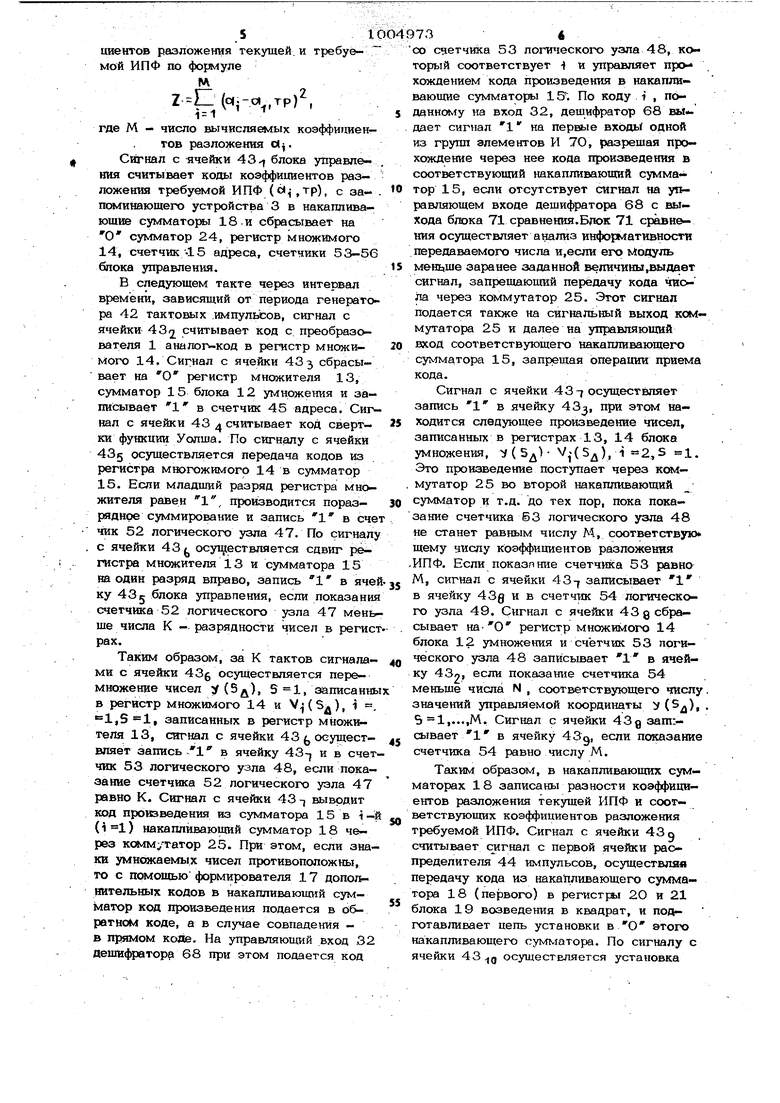

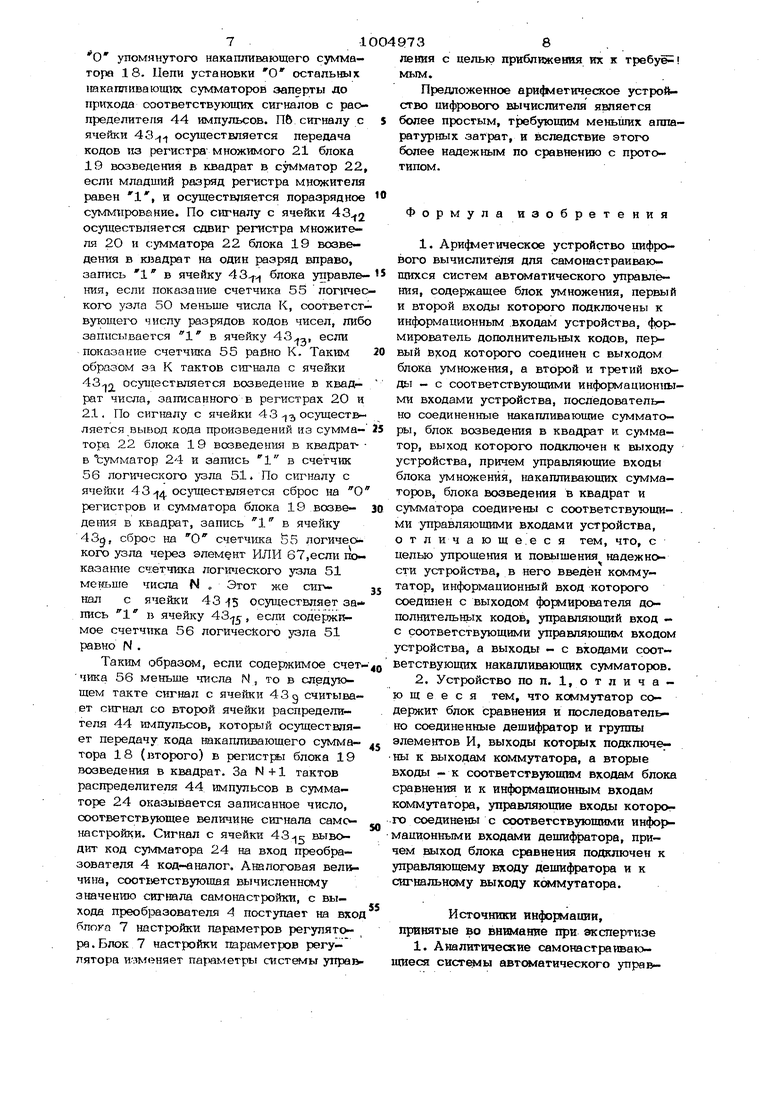

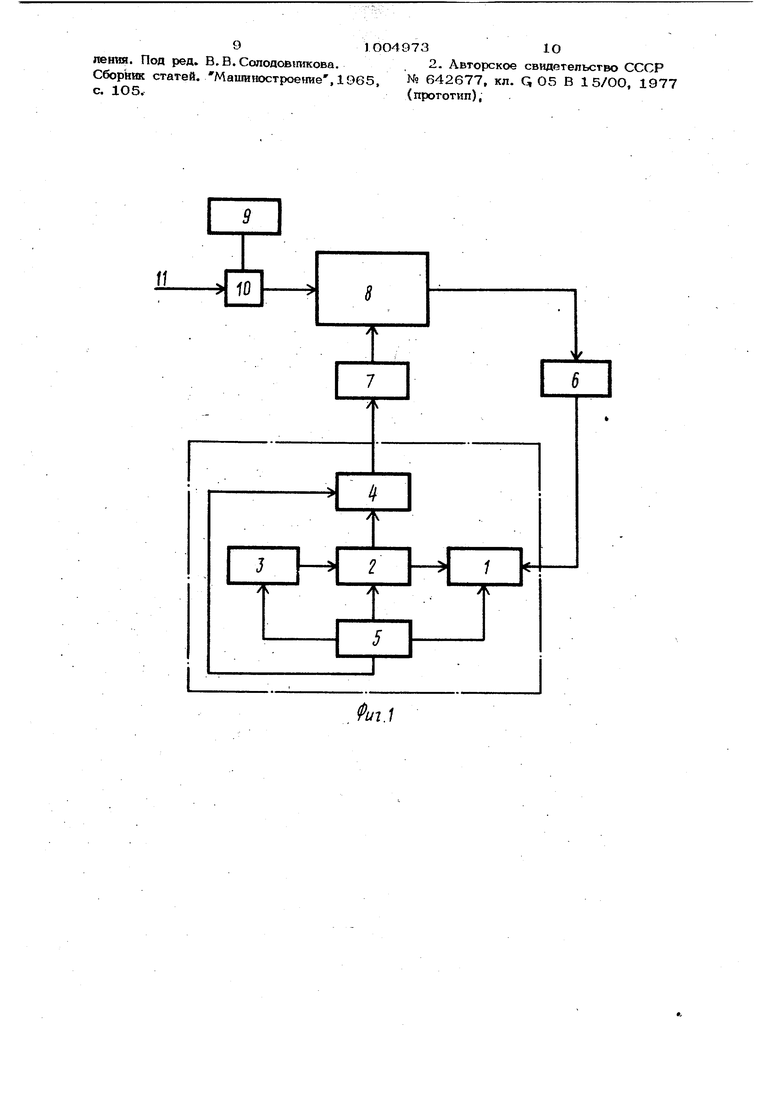

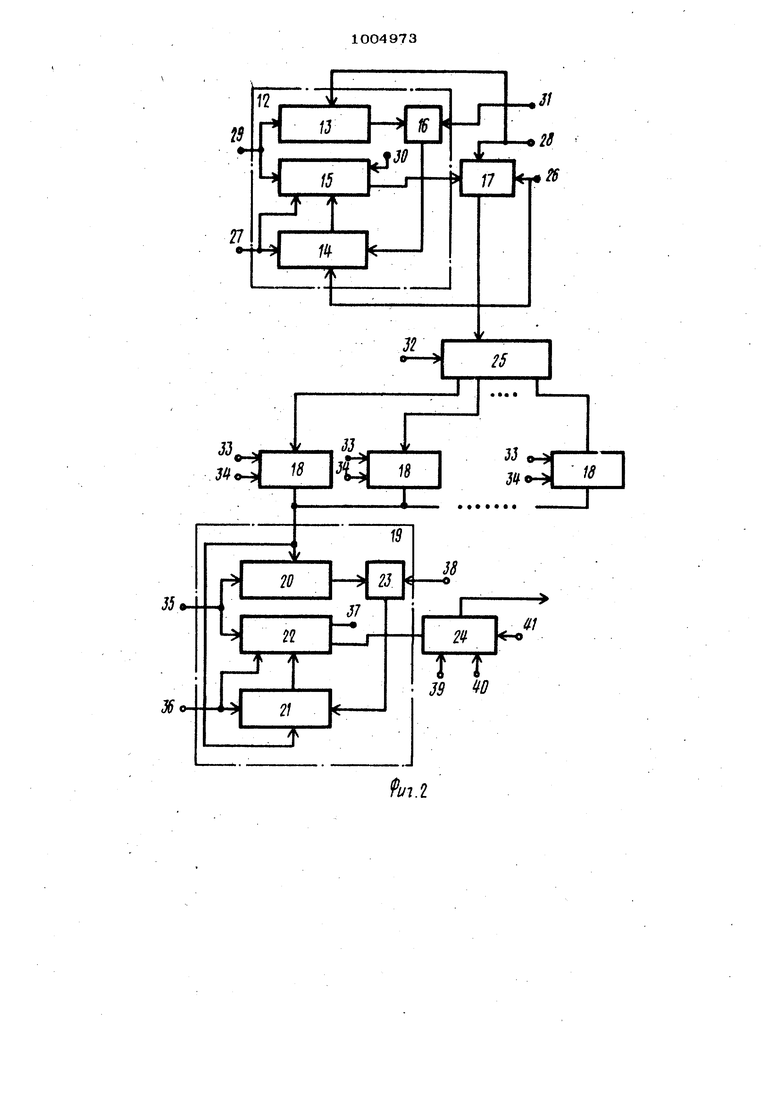

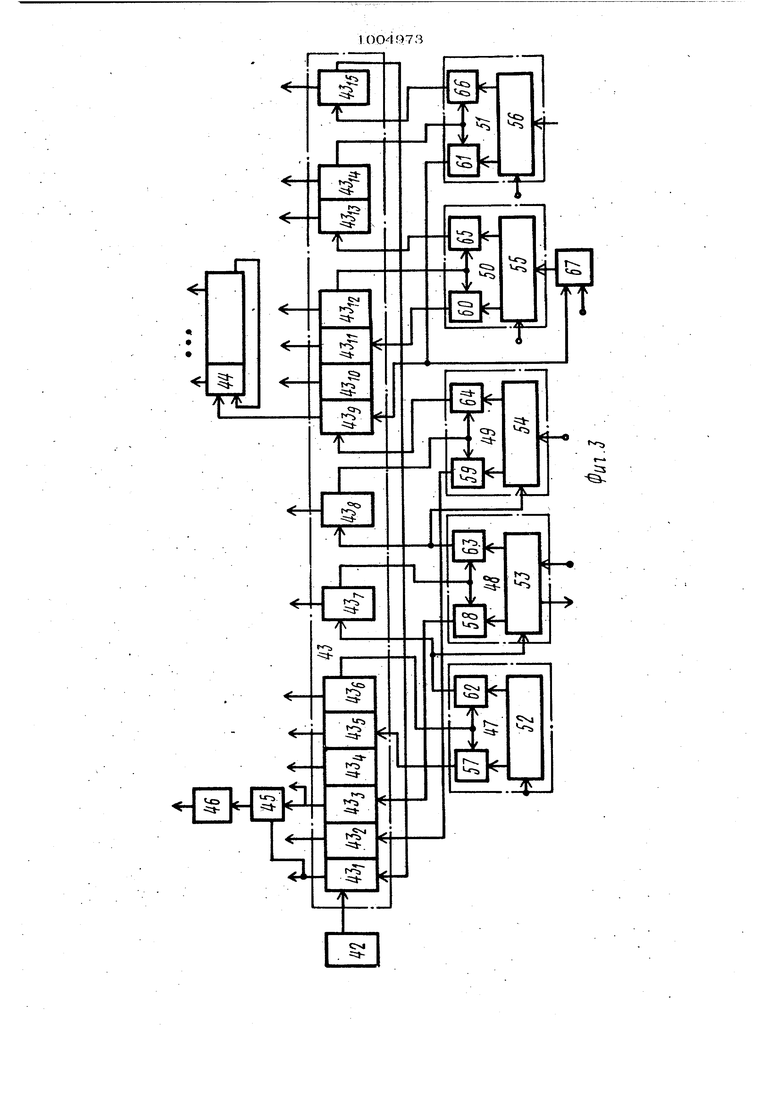

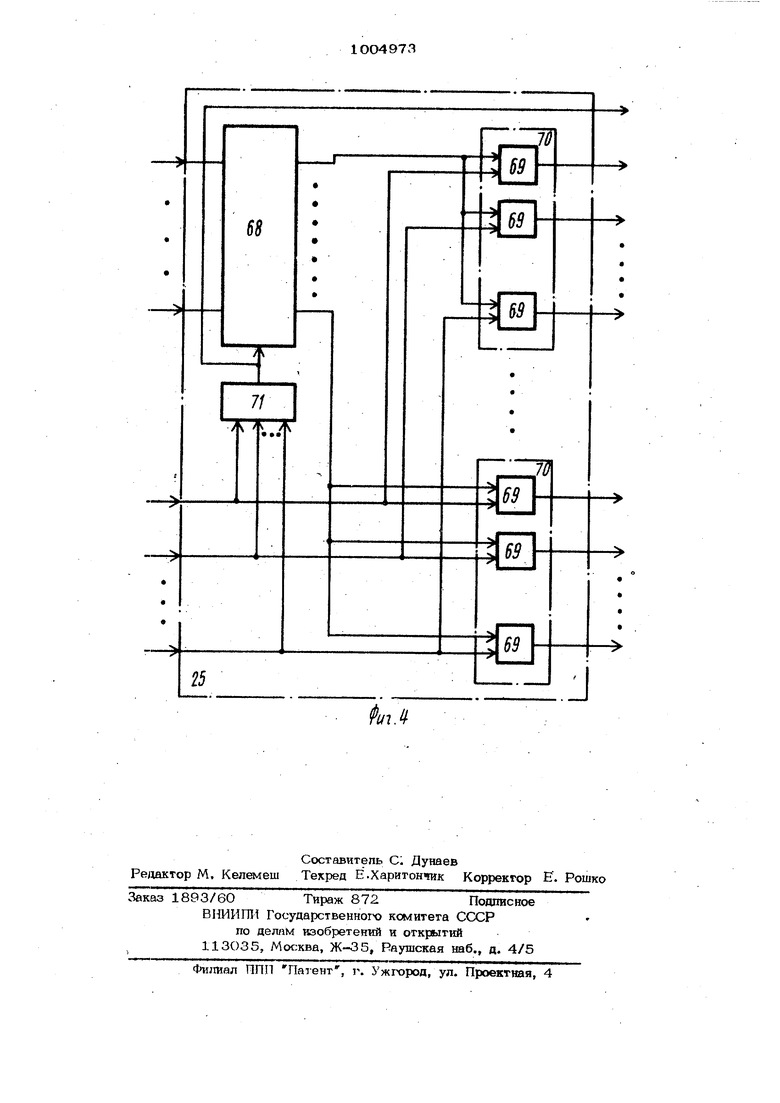

1. . Изобретение относится к автоматичеоксму управлению, в частности к вычислительным устройствам самонастраиваюишх- ся систем. Известно арифметическое устройство, содержащее блоки умножения, и применяется в составе системы, включающей пре образователь аналог-код, запоминающий блок, преобразователь код-аналог, управляюигае входы которых соединены с выходом блока управления, причем вход системы соединен с выходом датчика управляемой координаты системы, а выход подключен к блоку подстройки параметров регулятора. Алгоритм его работы осшвав на решении интегрального ypaj нения Вилера-Хопфа 13Недостатком указанного устройства является необходимость больших аппаратурных затрат для получения приемлемой точности, что обусловлено некорректность задач данного типа. Наиболее близким к изобретению по технической сущности является цифровое вычислительное устройство, содержащее блок умножения, первый и второй входы которого подключены к информационным входам устройства, формирователь дополнительных кодов, первый вход которого соединён с выходом блока умножения, а второй и третий входы - с cooTBeTCTsyKv. щими информационными входами устройства, и последовательно соединенные накапливающие сумматоры, блок возведёння в квадрат и сумматор, выход которого подключен к выходу устройства, причем управляющие входы блока умножения, накапливающих сумматоров, блока возведения в квадрат и сумматора соедисшны с соответствующими управляющими входами. устройства С 2 . Недостатками этого известноххэ устрой ства являются сложность и, следовательно, низкая надежность. ; Цель изобретения - упрощение устройства и повышение его надежности. Указанная цель достигается тем, что в арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления введен коммутатор, информационный вход которого соединен с выходом формирователя дополнительных кодов, у Г1равЛяющий вход - с соответствующим управляющим входом устройства, а выходы - с входами соответствующих накапливающих сумматоров. При этом коммутатор содержит блок сравнения и последовательно соединенные дешифратор и группы элементов И, выходы которых подключены к выходам коммутатора, а вторые входы - к соответст вующш 1 входам блока сравнения и к информашюнным входам коммутатора, управ ляющие входы которого соединены с соот ветству:юцшми ин4юрмацконными входами дешифратора, причем выход блока оравнения подключен к управляющему входу дешифра гора и к сигнальному выходу ком мутатора.. На фиг. 1 представлена блок-схема самонастраивающейся системы автоматического управления; на фиг. 2 блоксхема ари4метического устройства; на . 3 - блок-схема пр51мерной реализаци блока уиравле тя; на-фиг, 4 - блок-схема коммутатора. Блок-схема (фиг. 1) самонастраива- ющейся системы автоматического управления включает преобразователь 1 аналог код, арифметическое устройство 2, запоминающее устройство 3, преобразователе 4 - {од-аналог, блок 5 управления, датчик 6 управляемой координаты, блок 7 настройки, регулятор 8 с объектом управления, г енератор 9 пробных сигналов, блок 10 сложения, вход системы 11. Блок-схема (фиг. 2) арифметического устройства включает, блок 12 умножения состоящий из регистра множителя 13, регистра множимого 14, сумматора 15 и элемента И 16, формирователь 17 дополнительш 1х кодов, накапливающие сумматоры 18, блок 19 воз веде шш в квадрат, состоящий из регистра множителя 2О, регистра множимого 21, сумматора 22 и элемента И 23, сумматор 24, коммутатор 25, входы 26-41 устройства. Блок схема (фиг. 3) примерной реализации блока управления включает генератор 42 тактовых импульсов 42, сдвигающий регистр 43, состоящий из ячеек 43.-43..-., распределитель 44 импульсов, счетчик 45 адреса, деитфратор 46 адреса, логические узлы 47-51, состоящие вз счетчиков 52 - 56 и элементов И 57 - 66. элемент ИЛИ 67. 10 3 Блок-схема (фиг. 4) коммутатора включает дешифратор 68, групйы элементов И 69, объединенные в группы 70, блок 71 сравнения. Работа ари(}мётического устройства совместно с системой автоматического управления происходит следующим об.разом. На вход системы 11 аддитивно с управляющим сигналом (уставной) поступает сигнал с генератора 9, формирующего пробный сигнал типа псевдоспучайный двоичный (ПСДС). Управляемая координата гУ (i ), содержащая составляющую реакции на пробный сигнал, поступает на преобразователь 1 аналот код, где результаты иa epeния дискретных значений сигнала представляются в цифровом коде. Арис метическое устройство 2 обеспечивает вычисление коэффишсентов разложения с(| текущей импульсной переходной функции (ИПФ) по системе ортогональных функций Уолша (5д)П5д), (Я 3где а - текущее значение коэффициента разложения ИПФ по системе ортогональных функций Уолша; В - интенсивность пробного сигнала;(5д)- ордината выходно1го сигнала объекта в дискретные моменты времени А - минимальный период ПСДС; fsj - число данных в максимальном периоде ПСДС Т Мд; Mi (5д)- свертка функций Уолша и ПСДС, вычисляемая по формуле ) CP()W,.(r),(2) 1 где РСВд-Гд) - единичный ПСДС; i Д ортогональные функции Уолцш. Значение V CS) хранятся в запоминающем устройстве 3. Значения коэффициентов разложения требуемой ИПФ (, (Тр) вычиспнются заранее и вводятся в , запоьяитающее устройство 3. Кроме того, арифметическое устройбтво 2 обеспечивает вычисление сигнала самонастройки представляющего собой сумму квадратов разности всех коэффициентов разложения текущей, и требуе- мой ИПФ по фогжчуле. 2(«Г%.Р). где М - число вычисляемых коэффициентов разложения й. Сигнал с ячейки 43- блока управпе- ния считывает коды коэффициентов разложения требуемой ИПФ (,тр), с запоминающего устройства 3 в накапливающие сумматоры 18 и сбрасывает на О сумматор 24, регистр множимого 14,счетчик/-IS адреса, счетчики 53-56 блока управления. В следующем такте через интервал времени, зависящий от периода генератора 42 тактовых .импульсов, сигнал с ячейки 432 .считывает код с преобразователя 1 аналог-код в регистр множимого 14. Сигнал с ячейки 43 з сбрасывает на О регистр множителя 13, сумматор 15 блока 12 уг-1ножет1я и записывает в счетчик 45 адреса. Сиг нал с ячейки 43 4 считывает код свертки функции Уопша. По сигналу с ячейки 435 осзпдествляется передача кодов из регистра многожимого 14 в сумматор 15.Если младший разряд регистра множителя равен 1, производится поразрядное суммирование и запись 1 в сче чик 52 логического узла 47. По сигнал с ячейки 43/ осуи ествляется сдвиг регистра множителя 13 и сумматора 15 на один разряд вправо, запись в яче ку 435 ока управпенИя, если показани счетчика 52 логического узла 47 мень ще числа К - разрядности чисел в регис pax. Таким образом, за К тактов сигналами с ячейки 43б осуществляется перемножение чисел У (5д), 5 1, г писанны в регистр множюлого 14 и V(S), i ,, записанных в регистр множителя 13, сигнал с ячейки 43 (, осуздествпяет запись - в ячейку 43-j и в счет чик 53 логического узла 48, если показание счетчика 52 логического узла 47 равно К. Сигнал с ячейки 43 -, выводит код произведения из сумматора 15 в i() накапливающий сумматор 18 через комм;,татор 25. При этом, если зна ки умножаемых чисел противоположны, то с помощью формирователя 17 дополнительных кодов в накапливающий сумматор код произведения подается в обратном коде, а в случае совпадения в прямом коде. На управляющий вход 32 деши ймторэ 68 при этом подается код о сметчика 53 логического узла 48, который соответствует 1 и управляет про- хождением кода произведения в накапливающие сумматоры 15, По коду i , поданнок1у на вход 32, дешифратор 68 вы«. дает сигнал 1 на первые вхЬдь( одной из групп элементов И 7О, разрешая прохождение через нее кода произведения в соответствующий накапливающий сумматор 15, если отсутствует сигнал на yivравляющем входе дешифратора 68с выхода блока 71 сравнения.БЛОК 71 сравнения осуществляет анализ информативности передаваемого числа и,если его Модуль меньше заранее заданной величины,выдает сигнал, запрещающий передачу кода чиола через коммутатор 25. Этот сигнал подается также на сигнальный выход коммутатора 25 и далее на управляющий вход соответствующего накапливающего cyNTMaTopa 15, запрещая операции приема кода. Сигнал с ячейки 43т осуществляет запись в ячейку 43, при этом находится следующее произведение чисел, записанных в регистрах 13, 14 блока умножения, У(5д)- V-(S), i 2,S 1. Это произведение поступает через ком- мутатор 2 5 во второй накапливающий сумматор и т.д. до тех пор, пока показание счетчика 63 логического узла 48 не станет равным числу М, соответствую щему числу коэффициентов разложения ИПФ. Если показпние счетчика 53 равно сигнал с ячейки 43-, записывает в ячейку 43д и в счетчик 54 логического узла 49. Сигнал с ячейки 43 Q сбрасывает регистр множимого 14 блока 12 умножения и счетчик 53 погивеского узла 48 записывает в ячейку 432i если показание счетчика 54 меньше числа N, соответствующего числу, значений управляемой координаты у (5д), . ,...,М. Сигнал с ячейки 43д заш:сывает в ячейку 43д, если показание счетчика 54 равно числу М. Таким образом, в накапливающих сумматорах 1 8 записаны разности коэффициентов разложения текущей ИПФ и соот- ветствующих коэффициентов разложения требуемой ИПФ. Сигнал с ячейки 43 g считывает сигнал с первой ячейки распределителя 44 импульсов, осуществляя передачу кода из накайливающего сумматора 18 (первого) в регистры 20 и 21 блока 19 возведения в квадрат, и подготавливает цепь установки в О этого накапливающего сумматора. По сигналу с ячейки 43(j осуществляется установка о упомянутого накапливающего сумматора 18. Цепи установки О остальных накапливающих сумматоров заперты до прихода соответствующих сигналов с распределителя 44 импульсов. Пб сигналу с ячейки 43 осуществляется передача кодов из регистра множимого 21 блока 19 возведения в квадрат в сумматор 22 если младший разряд регистра множителя равен , и осуществляется поразрядное суммирование. По сигналу с ячейки осуществляется сдвиг регистра множителя 2О и сумматора 22 блока 19 возведения в юзадрат на один разряд вправо, запись в ячейку 43-j, блока управлеifflH, если показание счетчика 55 логичес кого узла 5О меньше числа К, соответст BjTomero числу разрядов кодов чисел, либ записывается 1 в ячейку , если показание счетчика 55 равно К. Таким образом за К тактов сигнала с ячейки осуществляется возведение в квадрат числа, записанного в регистрах 20 и 21. По скптлу с ячейки 43 - осуществляется вывоц кода произведений из суммато fa 22 блока 1 9 возведения в квадратв Ъумматор 24 и запись 1 в счетчик 56 логического узла 51. По сигналу с ячеШси 43( осуществляется сброс на О регистров и сумматора блока 19 возвеДания в квадрат, запись 1 в ячейку 43д, сброс на О счетчика В5 логичеакого узла через элемент ИЛИ 67,если шказакие св;етчика логетшского увла 51 ,ше числа N „ Этот же сигнал с ячейки 43 -fS осуществляет за пись 1 в ячейку 43, если содержимое счетчика 56 логического узла 51 равно N . Таким образом, если содержимое счет чика 56 меньше числа N , то в следующем такте сигнал с ячейки 43 g считывает сигнал со второй ячейки распределителя 44 импульсов, который осуществляет передачу кода накапливающего сумматора 18 (второго) в регистры блока 19 возведения в квадрат. За N+1 тактов распределителя 44 импульсов в сумматоре 24 оказывается записанное число, соответствующее величине сигнала самонастройки. Сигнал с ячейки выводит код cyiviMaTopa 24 на вход преобразователя 4 код-ашлог. Аналоговая величина, соот1ютствую11щя вычисленнсму значению сигнала самонастройки, с выхода преоб)эазователя 4 поступает на вхо блока 7 настройки параметров регулятора . Блок 7 настройки параметров регулятора изменяет параметры системы управ ления с целью приближения их к требуемым. предложенное арифметическое устройство цифрового вычиспителя является более простым, требующим меньших аппаратурных затрат, и Вследствие этого более надежным по сравнению с прототипом. Формула изобретения 1.Арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления, содержащее блок умножения, первый и второй входы которогчэ подключены к информационным входам устройства, формирователь дополнительных кодов, первый вход которого соединен с выходом блока умножения, а второй и третий входы - с соответствующими информационными входами устройства, последовательно соединенные накапливающие сумматоры, блок возведения в квадрат и сумматор, выход которого подключен к выходу устройства, причем управляющие входы блока умножения, накапливающих сумматоров, блока возведения в квадрат и сумматора соединены с соответствующи- . ми управляющими входами устройства, отличающе.еся тем, что, с целью упрощения и повышения надежности устройства, в него введён коммутатор, информационный вход которого соединен с выходом формирователя дополнительнзых кодов, управляющий вход - с соответствующими управляющим входом устройства, а выходы - с входами соответствующих накапливающих сумматоров. 2.Устройство по п. 1, отличающее с я тем, что коммутатор содержит блок сравнения и последовательно соединенные дешифратор и группы элементов И, выходы которых подключе ны к выходам коммутатора, а вторые входы - к соответствующим входам блока сравнения и к информационным входам коммутатора, управляющие входы которого соединены с соответствующими информационными входами дешифратора, причем выход блока сравнения подключен к управляющему входу дешифратора и к сигнальному выходу кслшутатора. Источники информации, принятые во внимание при экспертизе 1. Аналитические самонастра тающиеся систи 1ы автсжгатического управлента. Под ред. Сборник статей. с. 1О5. 91001973lO В.В.Солодовтпсова., 2. Авторское свидетельство СССР Маши юстроение, 1965, № 642677, кл. Q О5 В 1 5/ОО, 1977 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления | 1976 |

|

SU642677A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для обработки многотоновых изображений | 1988 |

|

SU1608698A1 |

| Устройство для умножения | 1986 |

|

SU1388852A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для умножения | 1979 |

|

SU920705A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

Авторы

Даты

1983-03-15—Публикация

1981-11-09—Подача