Изобретение относится к вычислительной технике и может быть применено в качестве спецпроцессора для вычисления функций у ех, у хт.

Цель изобретения - расширение функциональных возможностей за счет вычисления функции у In (1 + х).

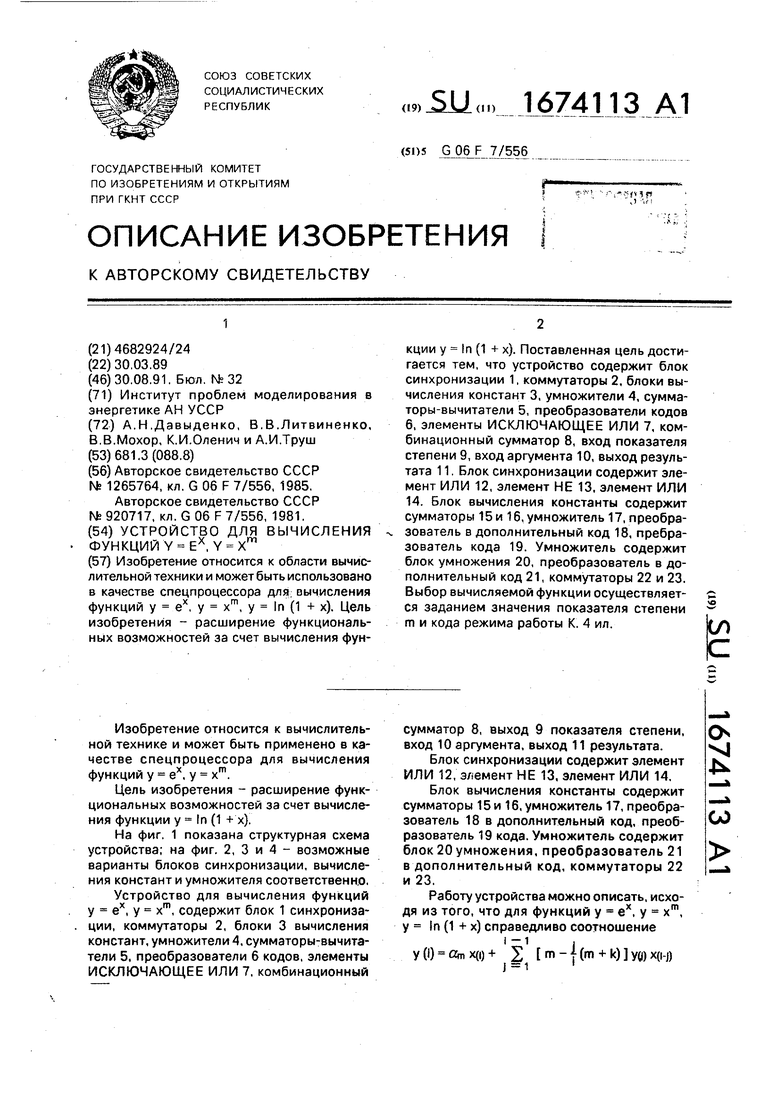

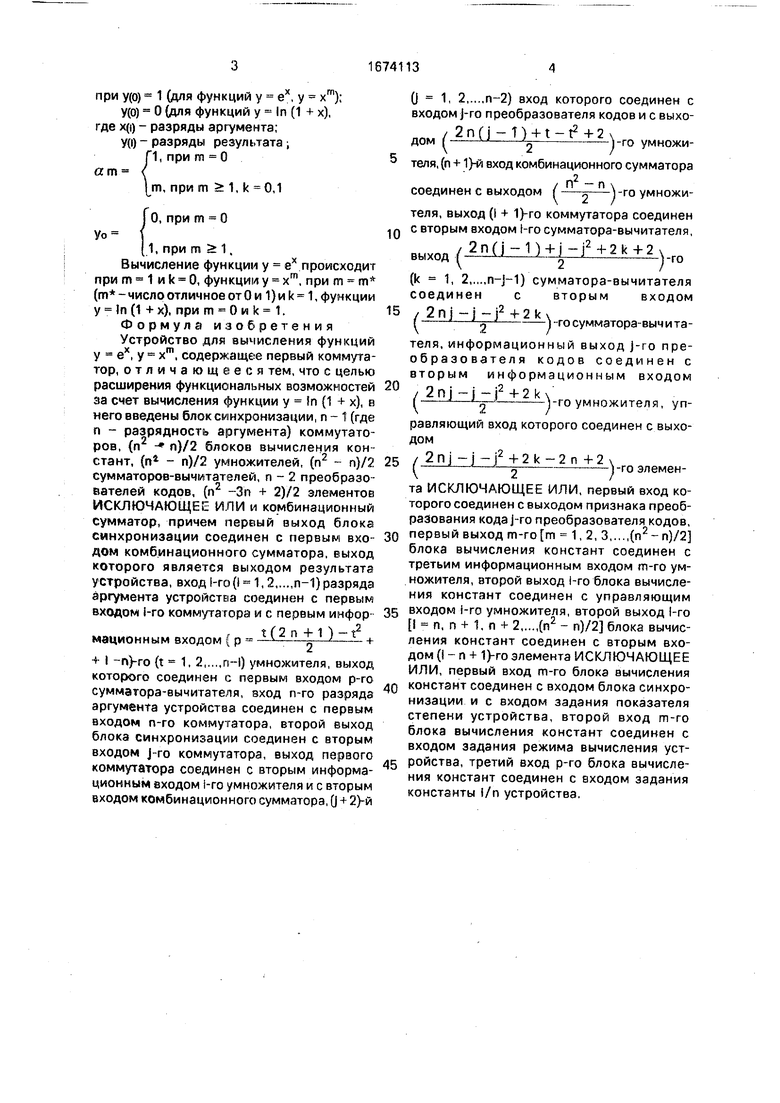

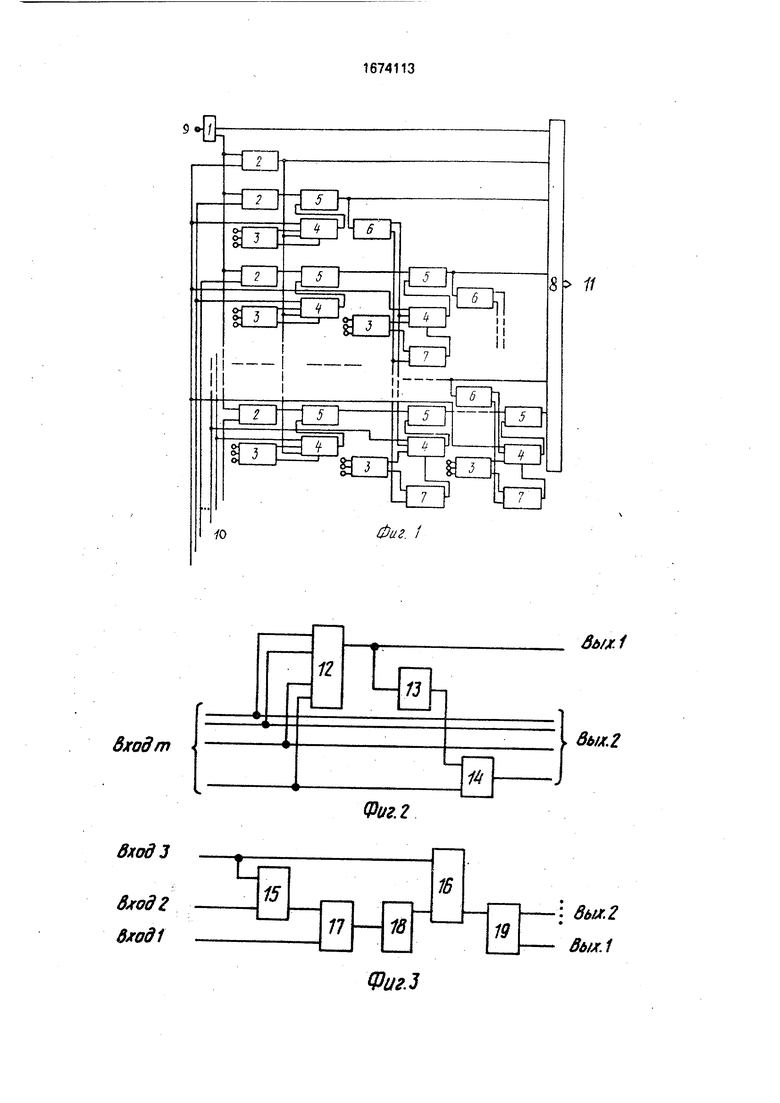

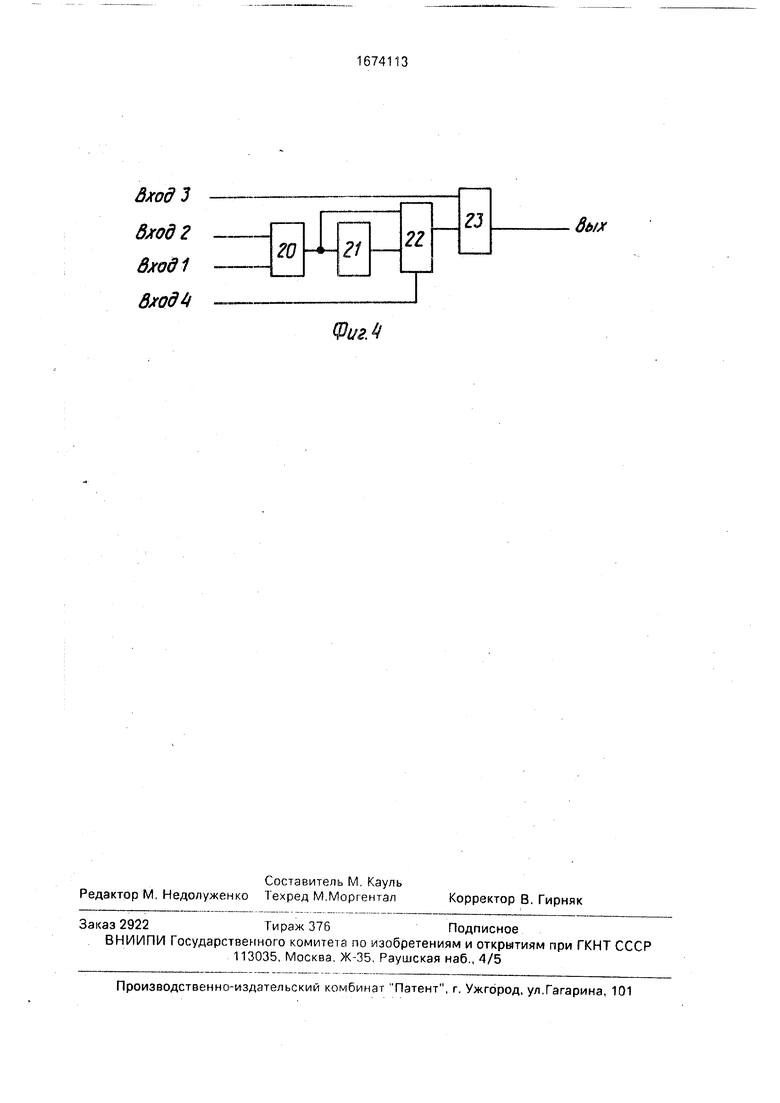

На фиг. 1 показана структурная схема устройства; на фиг. 2, 3 и 4 - возможные варианты блоков синхронизации, вычисления констант и умножителя соответственно.

Устройство для вычисления функций у ех, у хт, содержит блок 1 синхронизации, коммутаторы 2. блоки 3 вычисления констант, умножители 4, сумматоры-вычита- тели 5, преобразователи 6 кодов, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7. комбинационный

сумматор 8, выход 9 показателя степени, вход 10 аргумента, выход 11 результата.

Блок синхронизации содержит элемент ИЛИ 12, элемент НЕ 13, элемент ИЛИ 14.

Блок вычисления константы содержит сумматоры 15 и 16, умножитель 17, преобразователь 18 в дополнительный код, преобразователь 19 кода. Умножитель содержит блок 20 умножения, преобразователь 21 в дополнительный код, коммутаторы 22 и 23.

Работу устройства можно описать, исходя из того, что для функций у ех, у хт, у In (1 + х) справедливо соотношение

1-1,

у (I) От Х(|) + 2 t т | (т + k) J УФ) Х(Н)

о VI

CJ

J 1

при у(о) 1 (для функций у ех, у хт);

у(о) - 0 (для функций у In (1 + х), где x(i) - разряды аргумента; y(i) - разряды результата ,

Г1, при m - О ат

I т, при т 1. k 0,1

О, при т 0

Уо

1, при т 1.

Вычисление функции у ех происходит при m 1 и k 0, функции у хт, при т т (т - число отличное от 0 и 1) и k 1, функции у In (1 + х), при m 0 и k 1.

Формула изобретения Устройство для вычисления функций у ех, у - х, содержащее первый коммутатор, отличающееся тем, что с целью расширения функциональных возможностей за счет вычисления функции у In (1 + х), в него введены блок синхронизации, п - 1 (где п - разрядность аргумента) коммутаторов, (п2 - п)/2 блоков вычисления констант, (п - п)/2 умножителей, (п2 - п)/2 сумматоров-вычитателей, п - 2 преобразователей кодов, (п2 -Зп + 2)/2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и комбинационный сумматор, причем первый выход блока синхронизации соединен с первым входом комбинационного сумматора, выход которого является выходом результата

устройства, вход 1-го(I 1,2п-1) разряда

аргумента устройства соединен с первым входом 1-го коммутатора и с первым инфор, t ( 2 п + 1 ) -t2 , мационным входом ( р

+ I -n)-ro (t 1, 2n-l) умножителя, выход

которого соединен с первым входом р-го сумматора-вычитателя, вход n-го разряда аргумента устройства соединен с первым входом n-го коммутатора, второй выход блока синхронизации соединен с вторым входом J-ro коммутатора, выход первого коммутатора соединен с вторым информационным входом 1-го умножителя и с вторым входом комбинационного сумматора, (j + 2}-й

и

0 1, 2п-2) вход которого соединен с

входом J-ro преобразователя кодов и с выхо/ 2nQ-T) + t-t2-l-24 дом { w )го умножителя, (п + 1)-й вход комбинационного сумматора

/ п2 - п

соединен с выходом ( - -1-го умножителя, выход (I + 1)-го коммутатора соединен с вторым входом 1-го сумматора-вычитателя,

/ 2n(j - 1 ) -fj-j2+2k+24 выход Г VJ1-Ј-JWo

(k 1, 2,...,n-j-1) сумматора-вычитателя соединен с вторым входом

15

20

/ 2nj-j-J+2kx

/1-t- i-i-го сумматора-вычитателя, информационный выход j-ro преобразователя кодов соединен с вторым информационным входом

Wo умножителя, управляющий вход которого соединен с выходом

2 П j - j - j2 + 2 k

25

2nj-j-j2+2k-2 n +2

-го элемен0

5

0

5

та ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом признака преобразования кода j-ro преобразователя кодов,

первый выход 1, 2, 3(n2-n)/2

блока вычисления констант соединен с третьим информационным входом m-го умножителя, второй выход 1-го блока вычисления констант соединен с управляющим входом 1-го умножителя, второй выход 1-го I п, п + 1, п + 2(п2 - п)/2 блока вычисления констант соединен с вторым входом (I - п + 1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход m-го блока вычисления констант соединен с входом блока синхронизации и с входом задания показателя степени устройства, второй вход m-ro блока вычисления констант соединен с входом задания режима вычисления устройства, третий вход р-го блока вычисления констант соединен с входом задания константы l/n устройства.

S 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

| Устройство для вычисления функций синуса и косинуса | 1991 |

|

SU1827673A1 |

| Устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1012249A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU877526A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298764A1 |

| Устройство для вычисления логарифмов | 1988 |

|

SU1564618A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве спецпроцессора для вычисления функций Y = EX, Y = XM, Y = LN(1 + X). Цель изобретения - расширение функциональных возможностей за счет вычисления функции Y = LN(1 + X). Поставленная цель достигается тем, что устройство содержит блок синхронизации 1, коммутаторы 2, блоки вычисления констант 3, умножители 4, сумматоры-вычитатели 5, преобразователи кодов 6, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7, комбинационный сумматор 8, вход показателя степени 9, вход аргумента 10, выход результата 11. Блок синхронизации содержит элемент ИЛИ 12, элемент НЕ 13, элемент ИЛИ 14. Блок вычисления константы содержит сумматоры 15 и 16, умножитель 17, преобразователь в дополнительный код 18, преобразователь кода 19. Умножитель содержит блок умножения 20, преобразователь в дополнительный код 21, коммутаторы 22 и 23. Выбор вычисляемой функции осуществляется заданием значения показателя степени M и кода режима работы К. 4 ил.

12

бходт «

входЗ

вход1

66/JT.1

к выл. г

Фиг. 2

: вы.2 дш.1

Фиг.З

дходЗ

Вход 2 вход1 вход

Фиг. Ч

вь/х

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления показательно-степенной функции | 1980 |

|

SU920717A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-03-30—Подача