1 11

Изобретение относится к электронной технике и может быть использовано при построении микромощных интегральных схем запоминающих устройств на дополняющих . МДПтранзисторах.

Цель изобретения - снижение потребляемой мощности устройства.

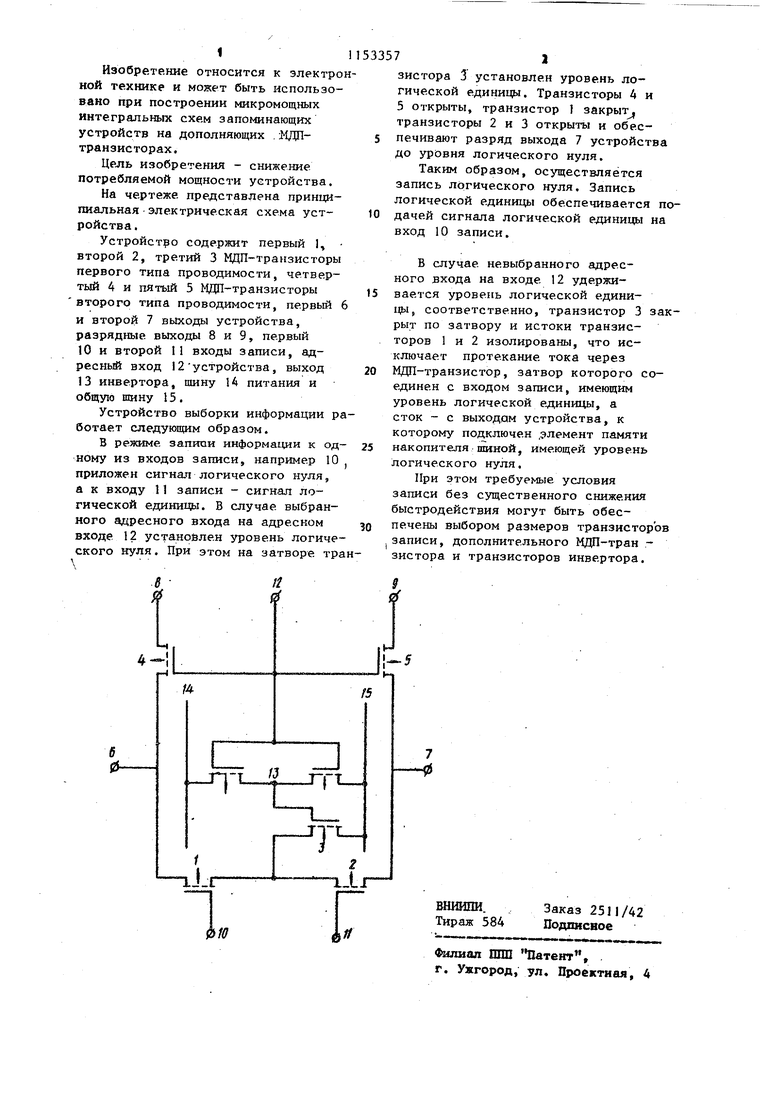

На чертеже представлена принципиальная электрическая схема устройства.

Устройство содержит первый 1, второй 2, третий 3 МДП-транзисторы первого типа проводимости, четвертый 4 и пятый 5 МДП-транзисторы второго типа проводимости, первый 6 и второй 7 выходы устройства, разрядные выходы 8 и 9, первый 10 и второй 1 входы записи, адресный вход 12устройства, выход 13 инвертора, шину 14 питания и общую шину 15.

Устройство выборки информации работает следующим образом.

В режиме заттаи информа1щи к одному из входов записи, например 10 , приложен сигнал логического нуля, а к входу 11 записи - сигнал логической единицы. В случае выбранного адресного входа на адресном входе 12 установлен уровень логического нуля. При этом на затворе тран

33571

зистора 3 установлен уровень логической единицы. Транзисторы 4 и 5 открыты, транзистор 1 закрыт, транзисторы 2 и 3 открыты и обеспечивают разряд выхода 7 устройства до уровня логического нуля.

Таким образом, осуществляется запись логического нуля. Запись логической единицы обе.спечивается подачей сигнала логической единицы на вход 10 записи.

В случае, невыбранного адресного входа на входе 12 удерживается уровень логической единицы, соответственно, транзистор 3 закрыт по затвору и истоки транзисторов 1 и 2 изолированы, что исключает протекание тока через

0 МДИ-транзистор, затвор которого соединен с входом записи, имеющим уровень логической единицы, а сток - с выходам устройства, к которому подключен ,злемент памяти

5 накопителя пмной, имеющей уровень Логического нуля.

При этом требуемые условия записи без существенного снижения быстродействия могут быть обес0 печены выбором размеров транзисторов I записи, дополнительного МДП-тран зистора и транзисторов инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выборки информации | 1981 |

|

SU1014029A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Триггер на дополняющих МДП-транзисторах | 1987 |

|

SU1465939A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

УСТРОЙСТВО ДПЯ ВЫБОРКИ ИНФОРМАЦИИ ИЗ БЛОКОВ ПАМЯТИi содержащее ключевые элементы на ЩЩ-транзисторах, причем стоки первого и второго транзисторов первого типа проводимости соединены с истоками соответственно третьего и четвертого транзисторов дополняющего типа проводимости и являются первыми и вторыми выходами устройства, стоки третьего и четвертого транзисторов являются разрядными выходами устройства, затворы третьего и четвертого транзисторов объединены и являются адресным входом устройства, затворы первого и второго транзисторов являются первым и вторым входами записи устройства, а истоки первогс и второго транзисторов объединены, отличающееся тем, что, с целью снижения потребляемой мощности, в устро.йство введены инвертор на дополняющих МДП-транзисторах, включенных между общей шиной и шиной питания, затворы которых подключены к адресном входу устройства, и дополнительный ключевой эле(Л мент на МДП-транзисторе, исток которого подключен к общей шинеу затвор - к объединенным стокам дополнякпцих МДП-транзисторов, а стокк объединенным истокам первого и второго транзисторов.

| Патент США 4191951, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство для выборки информации | 1981 |

|

SU1014029A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-04-30—Публикация

1984-02-09—Подача