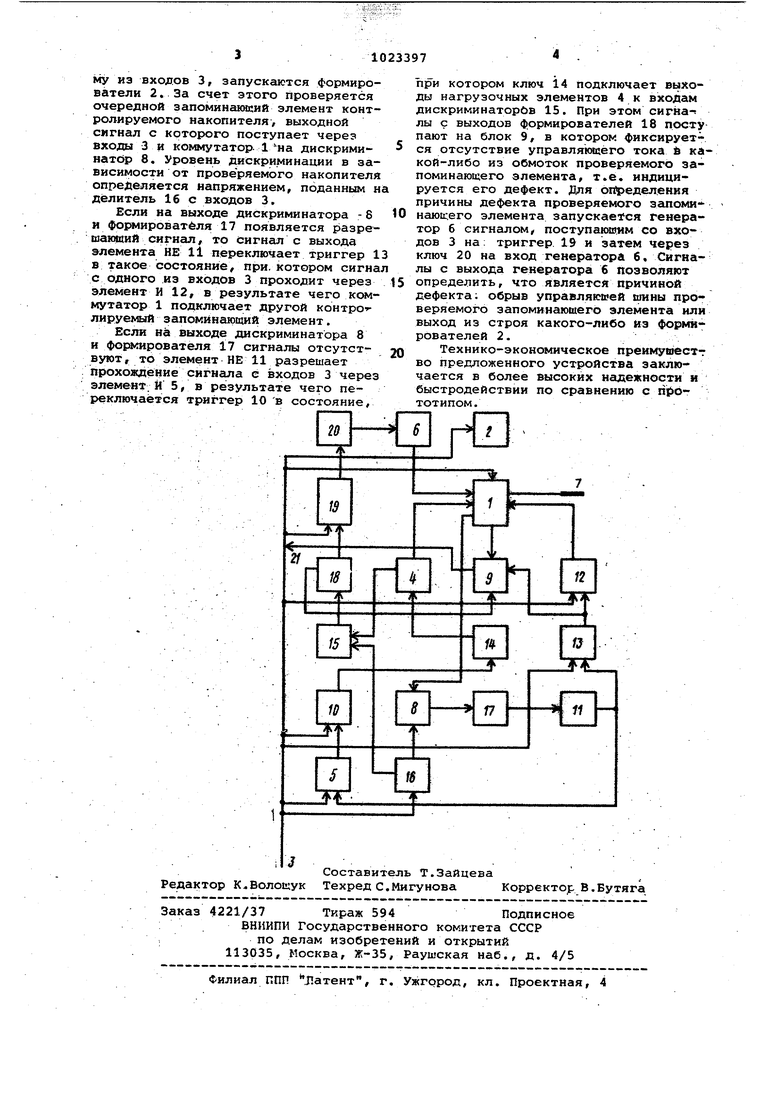

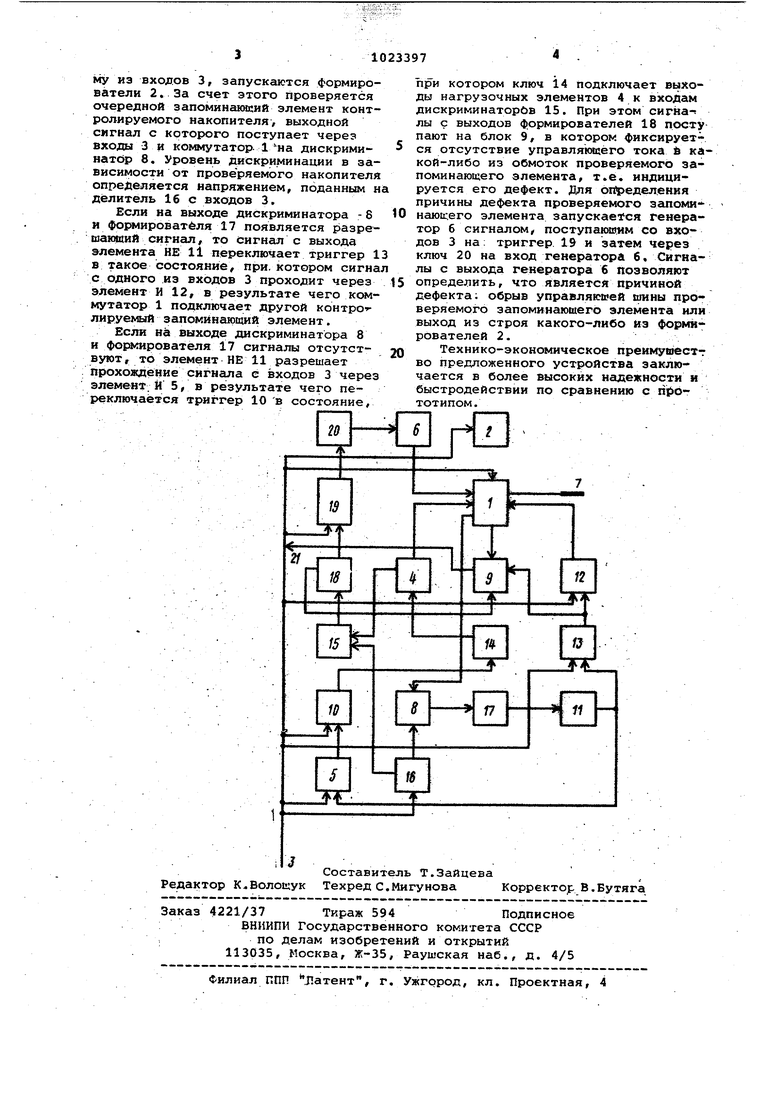

Изобретение относится к вычислительной технике и может.- быть использовано для контроля и испытаний накопителей запоминающих устройств 13УГ. Известно устройство для контроля памяти содержащее триггер, элемент блок сравнения регистр числа, блок пуска-останова, блок управления, которые связаны меяшу собой кодовой шиной ij , Недостатками этого устройства являются низкие быстродействие и на дежность . Наиболее близким к предлагаемому является устройство для контроля па мяти, содержащее регистр } числа, сх му сравнения, счетчик адресов, пуль управления, блок управления, соединенный с блоком формирования тестовых сигналов, амплитудный дискриминатор, блоки анализа сигналов 1 и О, элементы И.и триггеры Г2. Недостатками известного устройст ва являются низкие надежность и быс родействие, так как в нем не предус мотрен оперативный анализ причин сбоя, который может возникнуть из-за отказа формирователей адресных или разрядных токов, а также из-за обры ва адресных или разрядных шин, и ана лиз причин сбоя необходимо проводить с помощью дополнительных исследований. Цель изобретения - повышение надежности и быстродействия устройства.. Поставленная цель достигается тем что в устройство для контроля памяти, содержащее формирователи адресных и разрядных токов, коммутатор, нагрузочные элементы, дискриминатор блок индикации, первый элемент И, первый триггер и формирователь управляющих сигналов, причем первый вход коммутатора подключен к выходам формирователей адресных и разрядных токов, входал которых, второй вход KON iyTaTopa и первые входа) первого триггера и первого элемента И являются одними из входов устройства, а первый выход коммутатора и выход блока индикации являются выходами устройства, третий вход и второй и третий выходы коммутатора подключены соответственно к одному из выходов нагрузочных элементов, к первому входу дискриминатора и к первому входу блока индикации, выход дискриминатора соединен с входом фОрмирователя управляюп их сигналов, выход первого элемента И подключен к второму входу первого триггера, введены генератор контрольных сигналов, второй и третий триггеры, группа дискриминаторов, делитель напряжения, ключи, второй элемент И, элемент НЕ и группа формирователей управляющих сигналов, входы которых соединены с выходами дискриминаторов группы, входел которых подключены соответственно к другим выходам нагрузочных элементов и к одним .из выходов делителя напряжения, другой 13ЫХОД которого соединен с вторым входом дискриминатора, вход и выход первого ключа соединены соответственно с выходом первого триггера и с входом нагрузочных элементов, вход элемента НЕ подключен к выходу формирователя управляющих сигналов, а выход - к .второму входу первого элемента и и первому входу второго триггера, выход которого соединен с первым входом второго элемента И и вторым входом блока индикации,третий вход которого подключен к одним из выходов формирователей управляющих сигналов группы, другие выходы которых соединены с первым входом третьего триггера, выход которого подключен к входу второго ключа, выход которого соединен с входом генератора контрольных сигналов, выход которого подключен к четвертому входу коммутатора, пятый вход которого соединен с выходом вторюго элемейта И, второй вход которого, вторые входы второго и третьего триггеров и вход делителя напряжения являются другими входами устройства, На чертеже представлена функциональная схема предложенного устройства. . Устройство содержит коммутатор 1, формирователи 2 адресных и разрядных токов (на чертеже обозначены входы 3 устройства), нагрузочные элементы 4, первый элемент И 5, генератор б контрольных сигналов (7 - первый выход коммутатора), дискриминатор 6, блок 9 индикации, первый триггер 10, элемент НЕ 11, второй элемент И 12, второй триггер 13, первый ключ 14, группу дискриминаторов 15, делитель 16 напряжения, формирователь 17 управляющих сигналов, группу фор1лирователей 18 управляющих сигналов, третий триггер 19 и второй ключ 20 (21 - другой выход:устройства). Устройство работает след;лсщим образом. При контроле или испытании накопителей запоминающих устройств в режиме считывания по входам 3 поступает управлякяций сигнал на вход элемента И 5, на другой вход которого проход;ит разрешающий сигнал с элеМ€нта НЕ 11. Выходной сигнал с элемента И 5 поступает на вход тригге- . ра 10, который устанавливается в То состояние, при котором через ключ 14 подключаются нагрузочные элементы 4 к коммутатору 1. Одновременно по сигналу, поступившему по одному из входов 3, запускаются формирователи 2. За счет этого проверяется очередной запоминающий элемент контролируемого накопителя, выходной сигнал с которого поступает через входы 3 и коммутатор дискриминатор 8. Уровень дискриминации в зависимости от проверяемого накопителя определяется напряжением, поданным н делитель 16 с входов 3.

Если на выходе дискриминатора -8 и формирователя 17 появляется разрешающий сигнал , то сигнал с выхода элемента НЕ 11 переключает триггер 1 в такое состояние, при. котором сигна с одного из входов 3 проходит через элемент И 12, в результате чего KC Iмутатор 1 подключает другой контро лируемый запоминающий элемент.

Если на выходе дискриминатора 8 и формирователя 17 сигналы отсутствуют, то элемент НЕ 11 разрешает прохождение сигнгша с входов 3 через элемент. И 5, в результате чего переключается триггер 10 в состояние.

при котором ключ 14 подключает выходы нагрузочных элементов 4 к входам дискриминаторйв 15. При этом сигналы с выходов формирователей 18 посту пают на блок 9, в котором фикСирует-. ся отсутствие управлякяцёго тока 6 какой-либо из обмоток проверяемого запоминающего элемента, т.е. индицируется его дефект. Для определения причины дефекта проверяемого запоминаю11;его элемента запускаемся генератор б сигналом, поступающим со входов 3 на: триггер 19 и затем через ключ 20 на вход генератора б. Сигналы с выхода генератора 6 позволяют определить, что является причиной дефекта; обрыв управлявшей шины проверяемого запоминающего элемента или выход из строя какого-либо Из формирователей 2.

Технико-экономическое преимувУестг во предложенного уст ройства заключается в более высоких надежности и быстродействии по сравнению с rijpoтотипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

УСТР9ЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ содержащее формирователи адресных и разрядных токов, коммутатор, нагрузочные элементы, дискриминатор, блок индикации, первый элемент И, первый триггер и формирователь управляющих сигналов, причем первый вход коммутатора подключен к выходам формирователей адресных и разрядных токов, входы которых, второй вход коммутатора и первые входы первого триггера и первого элемента И являются одними из входов устройства, а первый выход коммутатора и выход блока индикации являются выходами устройства, третий вход и второй и третий выходы коммутатора подключены соответственно к одному из выходов нагрузочных элементов, к первому входу дискриминатора и к первому входу блока индикации, выход дискриминатора соединен с входом формирователя управлякшдах сигналов, выход первого элемента И подключен к второму входу первого триггера, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены генератор контрольных сигналов, второй и третий триггеры, группа дискриминаторов, делитель напряжения, ключи, второй элемент И, элемент НЕ и группа формирователей управляияцих сигналов, входы которых соединены с выходами дискриминаторов группы, входы которых подключены соответственно к другим выходам нагрузочных элементов и к одним из выходов делителя напряжения, другой выход которого соединен с вторым входом дискриминатора, вход и выход первого ключа соединены соответственно с выходом первого триггера и с входом нагрузочных элементов, вход j элемента НЕ подключен к выходу формирователя управляющих сигналов, а выход - к второму входу первого элемента И и первому, входу второго триггера, выход которого соединен с первым входом второго элемента И и вторит входом блока индикации, третий вход которого подключен к одним из выходов формирователей управляющих сигналов группы, другие выходы которых соединены с первым входом третьего триггера, выход которого подключен к входу второго ключа, выход ко-торого соединен с входом генераР тора контрольных сигна}1ов, выход которого подключен к четвертому входу коммутатора, пятый вход которого соединен с выходом второго элемента И, второй вход которого, вторые входы второго и третьего триггеров и вход делителя напряжения являются другими входами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU744736A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU744734A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-06-15—Публикация

1982-01-04—Подача