Изобретение относится к цифровой вычислительной технике и предназнамено для использования в специализированных мини-ЭВИ.

Известно устройство для вычисления квадратного корня из суммы квад.ратов двух чисел, содержащее счетчики, схемы сравнения, делители частоты, блоки утроения, элементы И и НЕ и блок управления СО-

Однако.такое устройство обладает низкой точностью.

Наиболее близким к изобретению по технической сущности является устройство ДЛЯ вычисления квадратйого корня из суммы квадратов двух чисел, содержащее схему сравнения, блок умножения, блок вычисления коэффициентов, суммирующий и вычитающий счетчики 2.

Однако известное устройство также обладает низкой точностью, что связано с нецелесообразным выбором вида вспомогательной функции, значения которой хранятся в блоке вычисяе ния коэффициентов.

Целью изобретения ние точности.

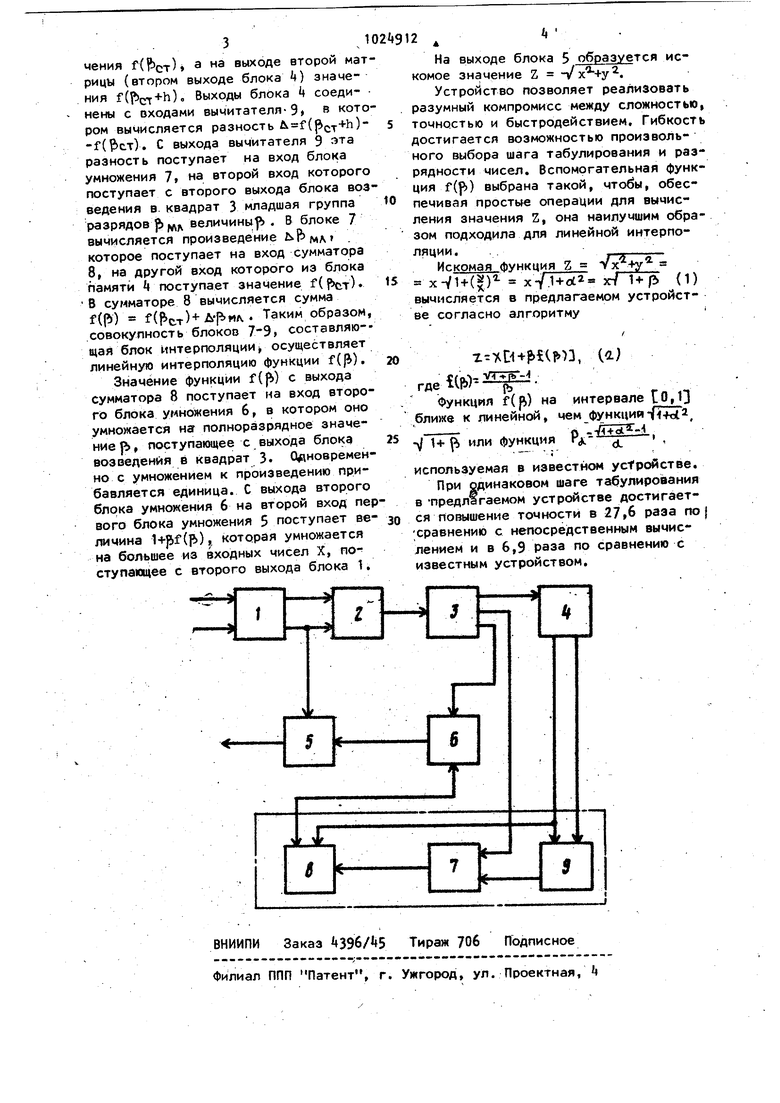

Поставленная цель что в устройство для ции Z , содержащее блок выборки меньшего числа, блок деления, блок памяти и три блока умножения, причем первый и второй входы блока выборки меньшего числа соединены с входами соот.ветственно первого и второго аргументов устройства, первый .выход блока выборки меньшего числа соединен с первым входом блока деления, второй вход которого соединен с вторым выходом блока выборки меньшего числа и первым входом первого блока умножения, второй вход и выход которого соединены соответственно с выходом второго блока умножения и выходом устройства, дополнительно введены блок возведения в, квадрат, сумматор и вычитатель, первый и второй входы которого соединены соответственно с первым и вторым выходами блока памяти, вход которог о соединен с выходом старших разрядов блока возведения в квадрат, вход которого соединен с выходом блока деления, выход вычитателя соединен с пер вым входом третьего блока умножения, второй вход и выход которого соединены соответственно с выходом младших разрядов блока возведения в квад первым входом сумматора, вто рой вход и выход которого соединены соответственно с первым выходом блока памяти и первым входом второго блока умножения, второй вход которого соединен с выходом всех разрядов блока возведения в квадрат. На чертеже представлена блоксхема устройства.

Устройство для вычисления функции Z содержит блок 1 выборки меньшего числа, блок 2 деления, блок 3 возведения в квадрат, блок i памяти, блоки умножения, сумматор 8 и вычитатель 9.

Блок памяти k содержит дешифратор и две запоминающие матрицы.

Устройство работает следующим образом.

Числа X и у поступают на входы блока выборки меньшего числа 1, который сравнивает их и коммутирует на выходы так. Чтобы на первом выходе блока 1 всегда оказывалось меньшее число (будем считать, что это Y), а на втором выходе большее {Х). Оба числа поступают на входы блока деления 2, в котором вычисляется частное X Р частное поступает на входблока возведения в квадрат 3, в котором вычисляется величина % . Одновременно в блоке 3 двоичный код величины разбивается на две группы разрядов - старшую Р) и младшую

Число разрядов старшей группы п. определяет шаг , с которым в запоминающих,матрицах блока памяти k хранятся значения вспомогательной

/TTF-i .

i(ib)

функции Р

Остальная часть устройства работает аналогично известному. Старшая группа разрядов поступаетна вход дешифратора блока памяти k Выходы . дешифратора, чисдо которых равно , соединены с- соответствующими строками запоминающих матриц. В первой матрице хранятся значения функции f(p), а во второй матрице - значения f(h), соответствующие сдвигу аргумента на шаг h. Появление определенной кодовой комбинации входе, дешифратора приводит к выборке соответствующих строк запоминающих матриц и появлению на выходе первой матрицы (первом выходе блока ) зна31чения Г(Ьст), а на выходе второй мат рицы (втором выходе блока 4) значения f(p)CT+h), Выходы блока 4 соединены с входами вычитателя-9 в кото ром вычисляется разность Д.Г() -f()cT). С выхода вычитателя 9 та разность поступает на вход блока умножения 7 на второй вход которого поступает с второго выхода блока воз ведения в. квадрат 3 младшая группа разрядов величины . В блоке 7 вычисляется произведение ь., которое поступает на вход сумматора 8, на другой вход которого из блока памяти Ц поступает значение f(f. В сумматоре 8 вычисляется сумма f((b) Г(ет)+ Л-р-ил . Таким образом, совокупность блоков 7-9, составляю-щаЯ блок интерполяцииj осуществляет линейную интерполяцию функции f(|i). Значение функции f( с выхода сумматора 8 поступает на вход второго блока умножения 6, в котором оно умножается на полноразрядное значение р, поступающее с выхода блока возведения в квадрат 3. Ойновременно с умножением к произведению прибавляется единица. С выхода второго блока умножения 6 на второй вход пер вого блока умножения 5 поступает величина l-fjSf (р),, которая умножается на большее из входных чисел X, поступающее с второго выхода блока 1. 2 На выходе блока 5 образуется искомое значение Z . Устройство позволяет реализовать разумный компромисс между сложностью, точностью и быстродействием. Гибкость достигается возможностью произвольного выбора шага табулирования и разрядности чисел. Вспомогательная функция f(p) выбрана такой, чтобы, обеспечивая простые операции для вычисления значения Z, она наилучшим образом подходила для линейной интерполяции. . V25E V Искомая Функция Z x-yi + () x-/.H-ot2 Х-/ r+fb (1) x-TVfft j - л-т.1-ЮС вычисляется в предлагаемом устройстве согласно алгоритму Zt D-i-H |b)3, -.vcre:d Функция f(f) на интервале tjMl ближе к линейной, чем функций-ff, -п у 1+ или функция г,--- , используемая в известном ycfpoAcTBe. При одинаковом шаге табулирования в -предлагаемом устройстве достигается повышение точности в 27,6 раза поj сравнению с непосредственным вычислением и в 6,9 раза по сравнению с известным устройством.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1277082A1 |

| Устройство для определения параметров распределения случайных величин | 1981 |

|

SU1084811A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для логарифмированияМАССиВОВ дВОичНыХ чиСЕл | 1979 |

|

SU847319A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Матричное устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1120346A1 |

IT

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР tr , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1975 |

|

SU656055A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-23—Публикация

1982-01-06—Подача