и является третьим выходим блока управления, входы элемента И-ИЛИ

являются первым, седьмым, девятым и десятым входами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1101889A1 |

1. БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопители, информационные выходы которых являются информационным выходами уст ройства, информационные входы накопителей подключены к одним из выходов информационного регистра, входы которого являются одними из информационных входов устройства, о т личаюв1ееся тем, что, с целью повышения надежности устройств ва, оно содержит блоки управления, регистр состояния, элемент ИЛИ, блоки приоритета и дешифратор, входы которого являются другими информационными входами устройства, выходы дешифратора подключены к первым входам блоков управления, первые выходы блоков управления подключены ко входам первого блока приоритета, выходы которого подключены к первым управляющим входам соответствующих накопителей, вторые управлянвдие входы накопителей под- ключены ко вторым управляющим выходам соответствующих блоков управления, третьи выходы которых подключены ко входам первой группы регистра -состояния, первые управляющие выходы накопителей подключены ко вторым входам соответствующих блоков управления н ко входам второй группы регистра состояния, вторые управляющие выходы накопителей подключены ко входам третьей группы регистра состояния, выходы первой группы которых подключены к третьим входам соответствующих блоков управления и ко входам элемента ИЛИ, выходы у второй группы регистра состояния подключены к четвертым входам соответствующих блоков управления, пятые и шестые входы которых об едииены и являются соответственно первым и вторым управляющими входами устройства, выходы третьей группы регистра состояния подключены к вхо-. дам второго блока приоритета, выходы которого, подключены к седьмым входам соответствующих блоков управления, восьмые входы, блоков управления подключены.к другим выходам информационного регистра и являются (Л другими-информационными входами устройства, восьмые входы блоков управления объединены и являются третьим управляющим входом устройства, десятые входы блоков управления подключены к выходу элемента ИЛИ. 1 2. Устройство по п. 1, отличающееся темг что блок управления содержит элементы И, блок сравнения, элемент И-ИЛИ-и реUi гистр, информационный вход которого подключен к первому входу блока сравнения и является седьмым входом блока управления, выход регистра подключен к второму входу блока сравнения, выход которого подключен к первым входам первого и второго элементов И, второй и третий входы первого элемента И являются соответственно первым и шестым входами блока управления, второй и третий входы второго элемента И являются соответственно третьим и пятым входами блока управления, выходы первого и второго элементов И являются соответственно вторым и первым выходами блока управления, выход элемента И-ИЛИ подключен к первому управляющему входу регистра.

1

Изобретение относится к вычислительной технике и может быть использовано при построении систем буферной памяти многоканальных изкюрительных комплексов.

Известно буферное запоминающее устройство, содержащее накопители и блоки управления записью и чтением по числу накопителей, которое позволяет обеспечить согласование входного потока с пропускной способностькт многомодульного ядра обработки 1 .

Однако это устройство обладает ограниченной пропускной способность из-за возможности потерь измерений, особенно при девиации частоты следования входной информации.

Наиболее близким по технической сущности к изобретению является запоминающее устройство, содержащее входной регистр, шифратор, дешифратор и блоки буферной памяти, обращение к которым осуществляется по код номера источника информации 23.

Однако известное устройство не позволяетперераспределить поток входных данных между блоками буферной памяти и переключаться с одного блока на другой, что приводит к потерям данных как при переполнении блока буферной памяти,.так и при ег отказе. Все это снижает надежность. и пропускную способность устройства

Целью изобретения является повьгшение надежности устройства.

Поставленная цель достигается тем, что в буферное запоминаквдее устройство, содержащее накопители, информационные входал которых являются информационным выходами устройства, информационные входы накопителей подключены к одним из выходов информационного регистра, входы которого являются одними из информационных входов устройства, .дополнительно введены блоки управления, регистр состояния, элемен ИЛИ, блоки приоритета и дешифр атор, входы которого являются другими.информационными входами устройства, выходы дешифратора подключены к первым входам блоков управления, первые выходы блоков управления подключены ко входам первого блока йриоритета, выходы которого подключены к первым управляющим входам

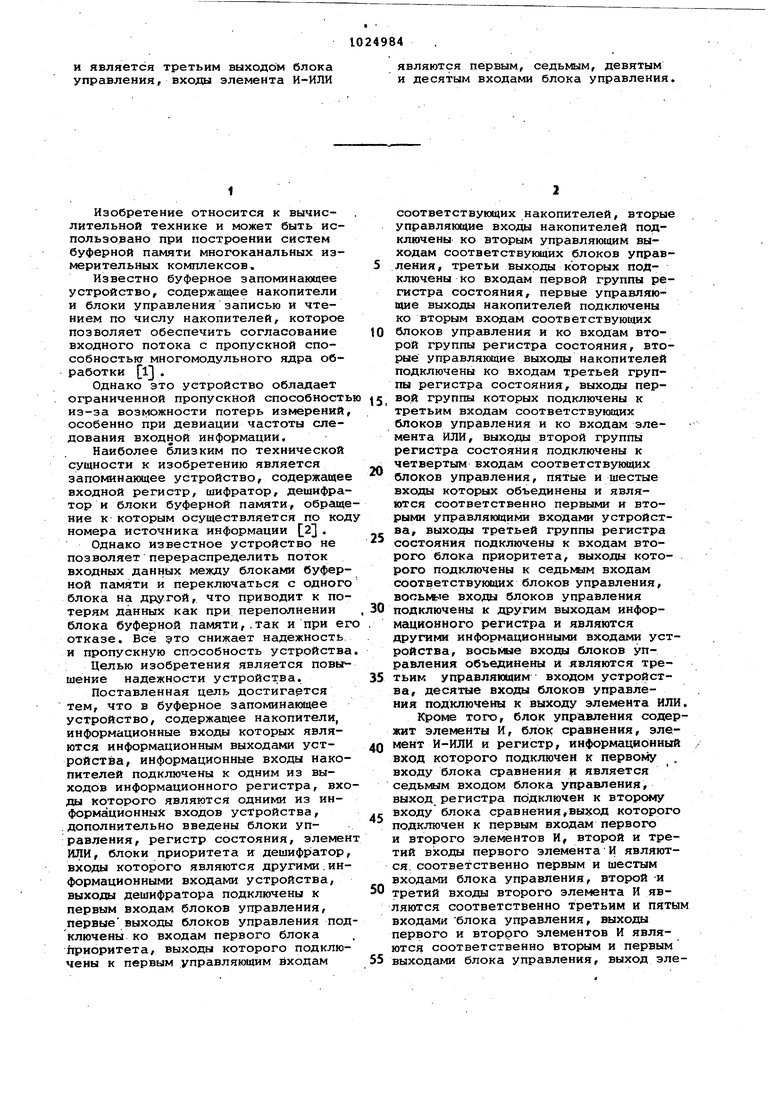

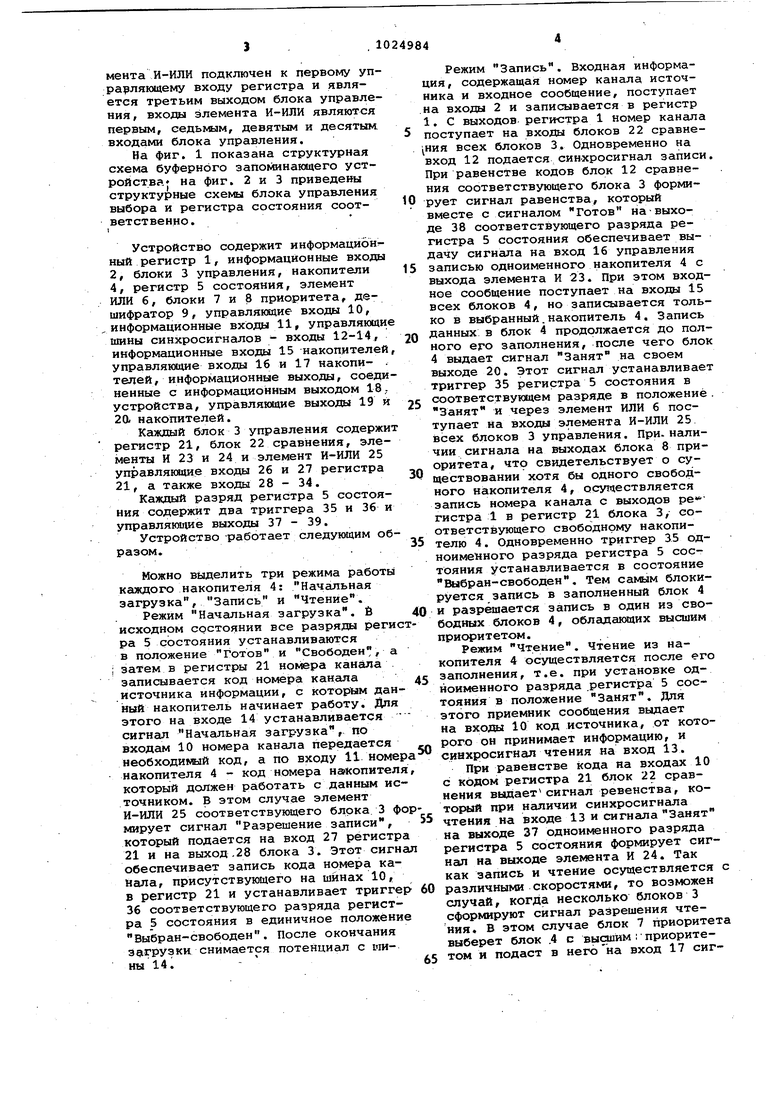

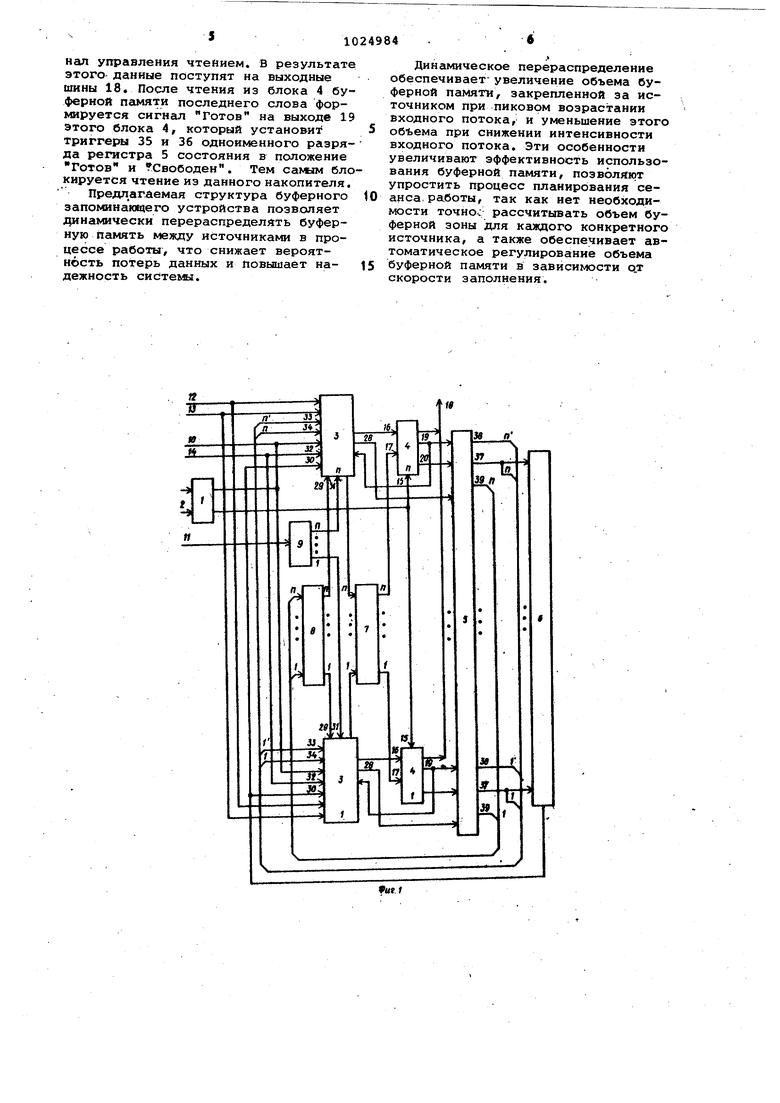

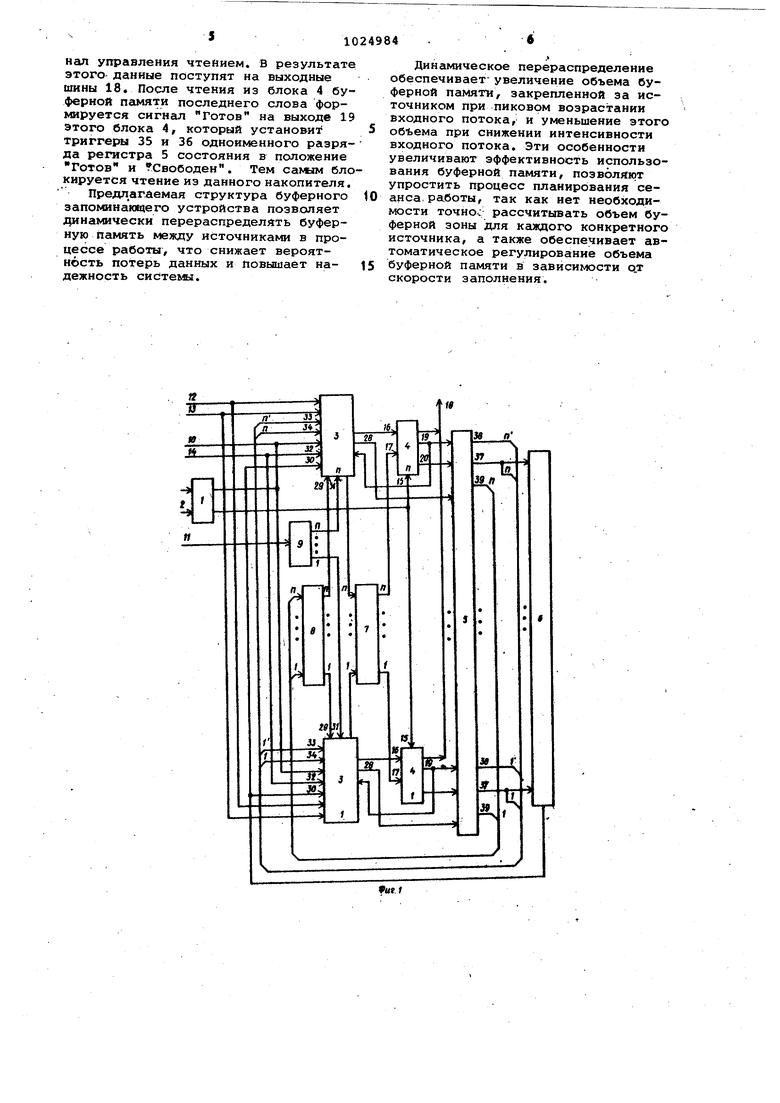

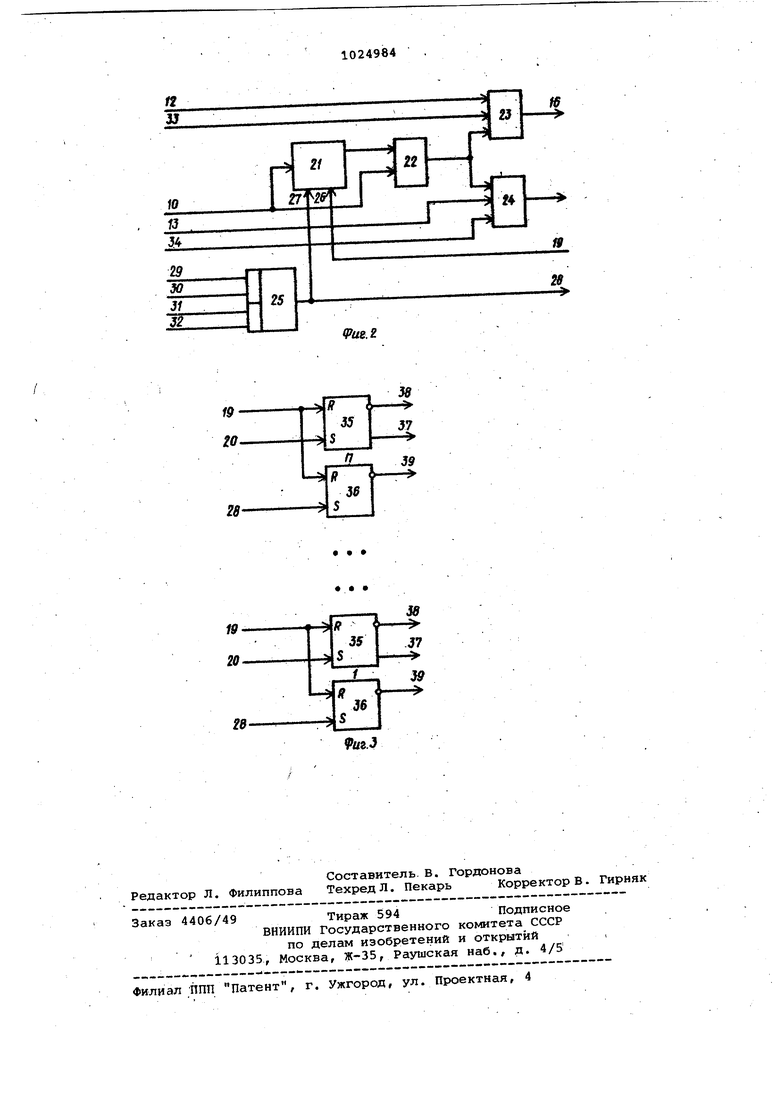

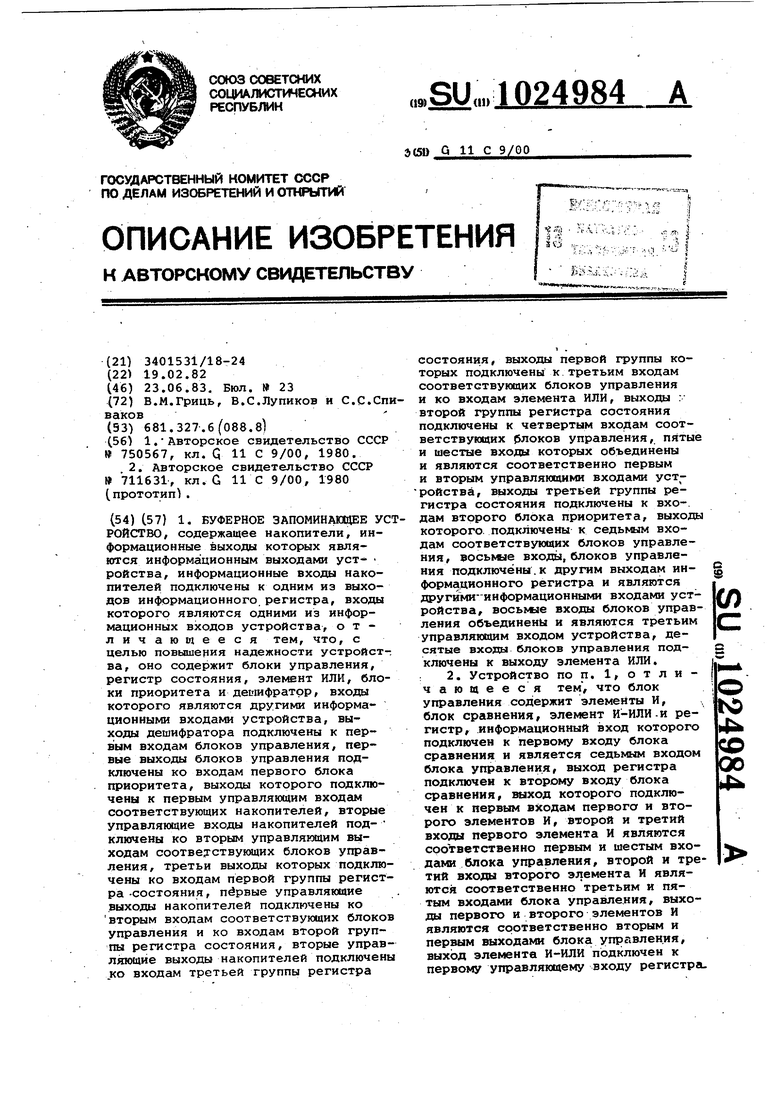

соответствукяцих накопителей, вторые управляющие входы накопителей подключены ко вторым управляющим выходам соответствующих блоков управления, третьи выходы которых подключены ко входам первой группы регистра состояния, первые управляющие выходы накопителей подключены ко вторым входам соответствующих блоков управления и ко входам второй группы регистра состояния, вторые управляющие выходы накопителей подключены ко входам третьей группы регистра состояния, выходы первой группы которых подключены к третьим входам соответствукяцих блоков управления и ко входам элемента ИЛИ, выходы второй группы регистра состояния подключены к четвертым входам соответствующих блоков управления, пятые и шестые входы которых объединены и являются соответственно первыми и вторыми управляющими входами устройства, выходы третьей группы регистра состояния подключены к входам второго блока приоритета, выходы которого подключены к седьмым входам соответствующих блоков управления, вооьмьте входы блоков управления подключены к другим выходам информационного регистра и являются другими информационными входами устройства, восьмые входы блоков управления объединены и являются третьим управляющим входом устройства, десятые входы блоков управления подключены к выходу элемента ИЛИ Кроме того, блок управления содержит элементы И, блок сравнения, элемент И-ИЛИ и регистр, информационный вход которого подключен к первому , входу блока сравнения и является седьмым входом блока управления, выход регистра подключен к второму входу блока сравнения,выход которого подключен к первым входам первого и второго элементов И, второй и третий входы первого элемента И являются, соответственно первым и шестым входами блока управления, второй и третий входы второго элемента И являются соответственно третьим и пяты входами блока управления, выходы первого и второго элементов И являются соответственно вторым и первым выходами блока управления, выход элемента И-ИЛИ подключен к перво упрарляющему входу регистра и является третьим выходом блока управления, входы элемента И-ИЛИ являются первым, седьмым, девятым и десятым входами блока управления. На фиг. 1 показана структурная схема буферного запоминакяцего устройства на фиг. 2 и 3 приведены структурные схемы блока управления выбора и регистра состояния соответственно. Устройство содержит информацибнтный регистр 1, информационные входы 2, блоки 3 управления, накопители 4, регистр 5 состояния, элемент ИЛИ б, блоки 7 и 8 приоритета, дешифратор 9, управлякхцие входы 10, , информационные входы 11, управляющи шины синхросигнсшов - входы 12-14, информационные входы 15 накопителей управляющие входы 16 и 17 накопителей, информационные выходы, соеди ненные с информационным выходом 18, устройства, управлякхцие выходы 19 и 20- накопителей. Каждый блок 3 управления содержи регистр 21, блок 22 сравнения, элементы И 23 и 24 и элемент И-ИЛИ 25 управлянядие входы 26 и 27 регистра 21, а также входы 28-34. Каждый разряд регистра 5 состояния содержит два триггера 35 и 36 и управлякшдае выходы 37 - 39. Устройство -работает следующим об разом.. Можно выделить три режима работы каждого накопителя 4: Начальная загрузка, Запись и Чтение. Режим Начальная загрузка. И исходном состоянии все разряды реги ра 5 состояния устанавливаются в положение Готов и Свободен), а ; затем в регистры 21 номера канала записывается код номера канала источника информации, с которым дан ный накопитель начинает работу. Для этого на входе 14 устанавливается сигнал Начальная загрузка, по входам 10 номера канала Передается необходимый код, а по входу 11 номе накопителя 4 - код номера накопител который должен работать с данным ис точником. В этом случае элемент И-ИЛИ 25 соответствующего блока. 3 ф мирует сигнал Разрешение записи, который подаётся на вход 27 регистр 21 и на выход,28 блока 3. Этот сигн обеспечивает запись кода номера каНапа, присутствующего на шинах 10, в регистр 21 и устанавливает тригге 36 соответствующего разряда регистра 5 состояния в единичное положени Выбран-свободен. После окончания загрузки снимается потенциал с шины 14. Режим Запись. Входная информация, содержащая номер канала источника и входное сообщение, поступает на входы 2 и записывается в регистр 1. С выходов регистра 1 номер канала поступает на входы блоков 22 сравнения всех блоков 3. Одновременно на вход 12 подается синхросигнал записи. При равенстве кодов блок 12 сравнения соответствующего блока 3 формирует сигнал равенства, который вместе с сигналом Готов на-выходе 38 соответствующего разряда регистра 5 состояния обеспечивает выдачу сигнала на вход 16 управления записью одноименного накопителя 4 с выхода элемента И 23. При этом входное сообщение поступает на входы 15 всех блоков 4, но записывается только в выбранный.накопитель 4. Запись данных в блок 4 продолжается до полного его заполнения, после чего блок 4 выдает сигнал Занят на своем выходе 20. Этот сигнал устанавливает триггер 35 регистра 5 состояния в соответствующем разряде в положение . Занят и через элемент ИЛИ 6 поступает на входы элемента И-ИЛИ 25 всех блоков 3 управления. При- наличии сигнала на выходах блока 8 приоритета, что свидетельствует о существовании хотя бы одного свободного накопителя 4, осуществляется запись номера канала с выходов гистра 1 в регистр 21 блока 3/ соответствующего свободному накопителю 4. Одновременно триггер 35 одноимеиного разряда регистра 5 состояния устанавливается в состояние Выбран-свободен. Тем самым блокируется запись в заполненный блок 4 и разрешается запись в один из свободных блоков 4, обладающих высшим приоритетом. Режим Чтение. Чтение из накопителя 4 осуществляется после его заполнения, т.е. при установке одноименного разряда регистра 5 состояния в положение Занят. Для этого приемник сообщения выдает на входы 10 код источника, от которого он принимает информацию, и синхросигнал чтения на вход 13. При равенстве кода на входах 10 с кодом регистра 21 блок 22 сравнения выдает сигнал ревенства, которалй при наличии синхросигнала чтения на входе 13 и сигнала Занят на выходе 37 одноименного разряда регистра 5 состояния формирует сигнал на выходе элемента И 24. Так как запись и чтение осуществляется с различными скоростями, то возможен случай, когда несколько блоков 3 сформируют сигнал разрешения чтения. В этом случае блок 7 приоритета выберет блок .4 с высшим : приоритетом и подаст в негона вход 17 тейием. в результате поступят на выходные шины 18. После чтения из блока 4 буферной памяти последнего слова форм руется сигнал Готов на выходе 19 этого блока 4, который установи триггеры 35 и 36 одноименного разря го состояния в положение - Свободен. Тем caNHM бло данного накопителя. Предлагаемая структура буферного запоминающего устройства позволяет динамически перераспределять буферную память между источниками в процессе работы, что снижает вероятность потерь данных и повышает надежность си стелы. 1 84 перераспределение Обеспечивает увеличение объема буферной памяти, закрепленной за исвхопноГ Р« ««°soM возрастании входного потока, и уменьшение этого вхопмпг. снижении интенсивности входного потока. Эти особенности увеличивают эффективность использования буферной памяти, позволяют ан Гработ ° «анса,работы, так как нет необходимости точно;- рассчитывать объем буферной зоны для каждого конкретного источника, а также обеспечивает автоматическое регулирование объема буферной памяти в зависимости от скорости заполнения.

39 -

57 -

39

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1977 |

|

SU711631A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-06-23—Публикация

1982-02-19—Подача