1

Изобретение относится к вьиисли- тельной технике, в частности к средствам автоматизированного контроля цифровых объектов, и может быть ис- пользовано для проверки цифровых схем построенных с использованием методов структурного проектирования.

Цель изобретения - повьшение достоверности контроля.

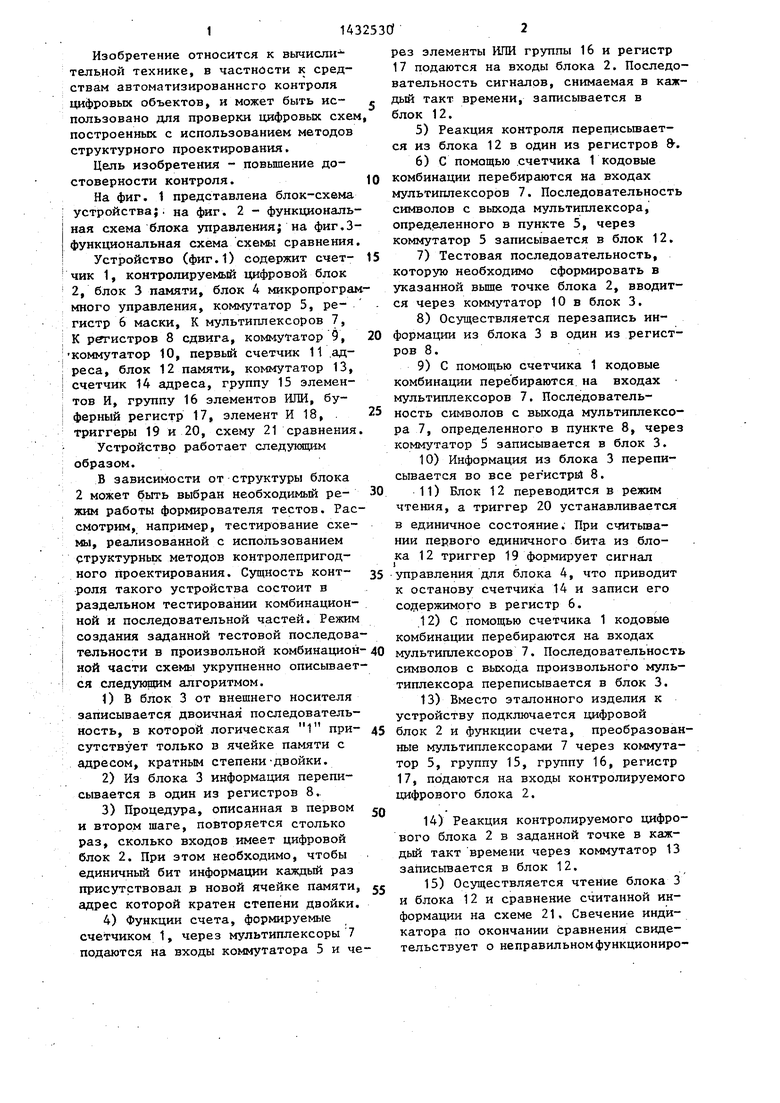

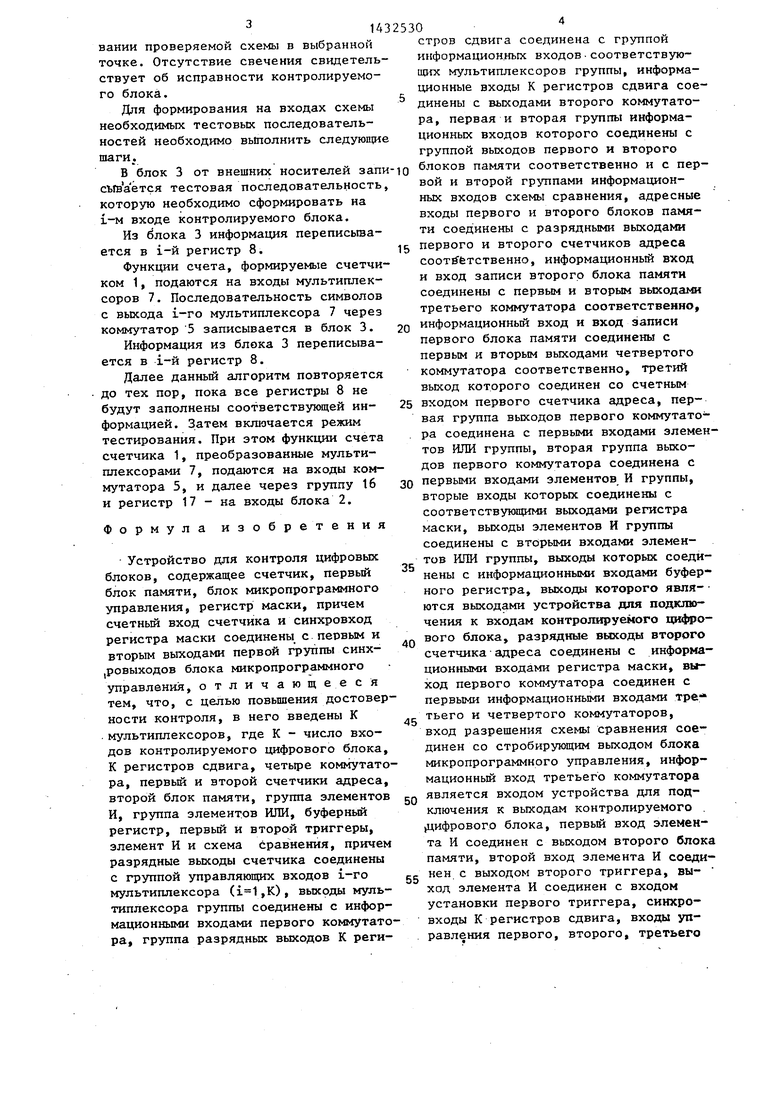

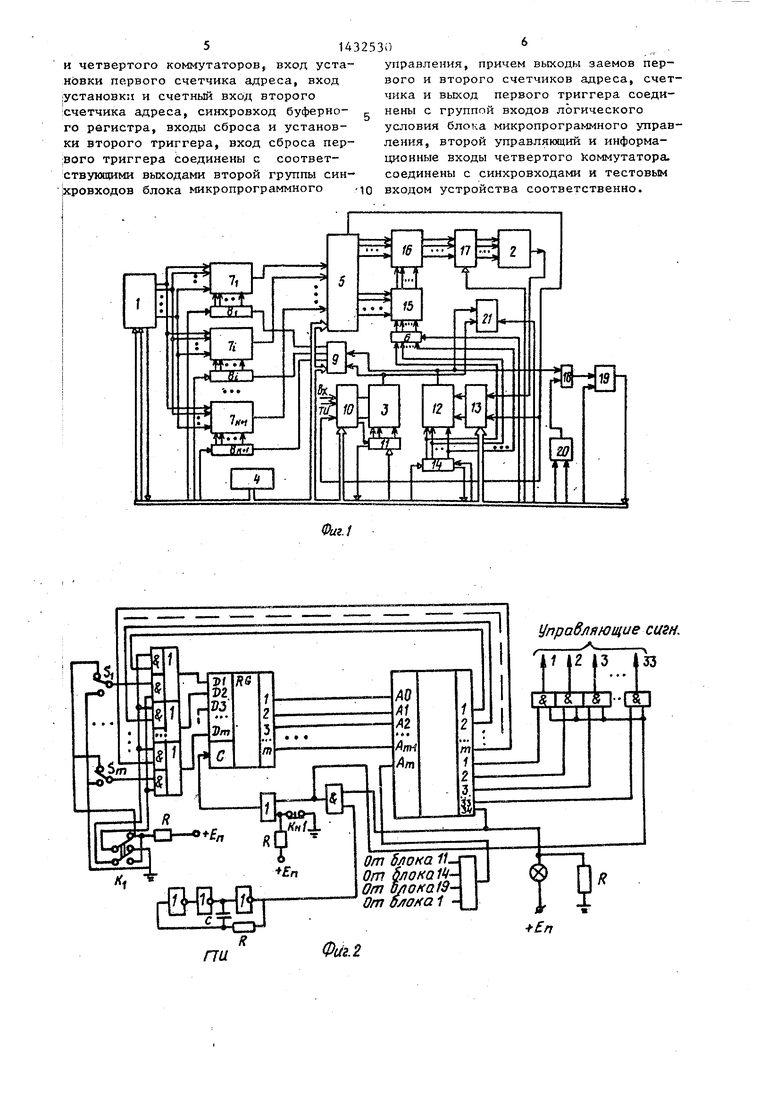

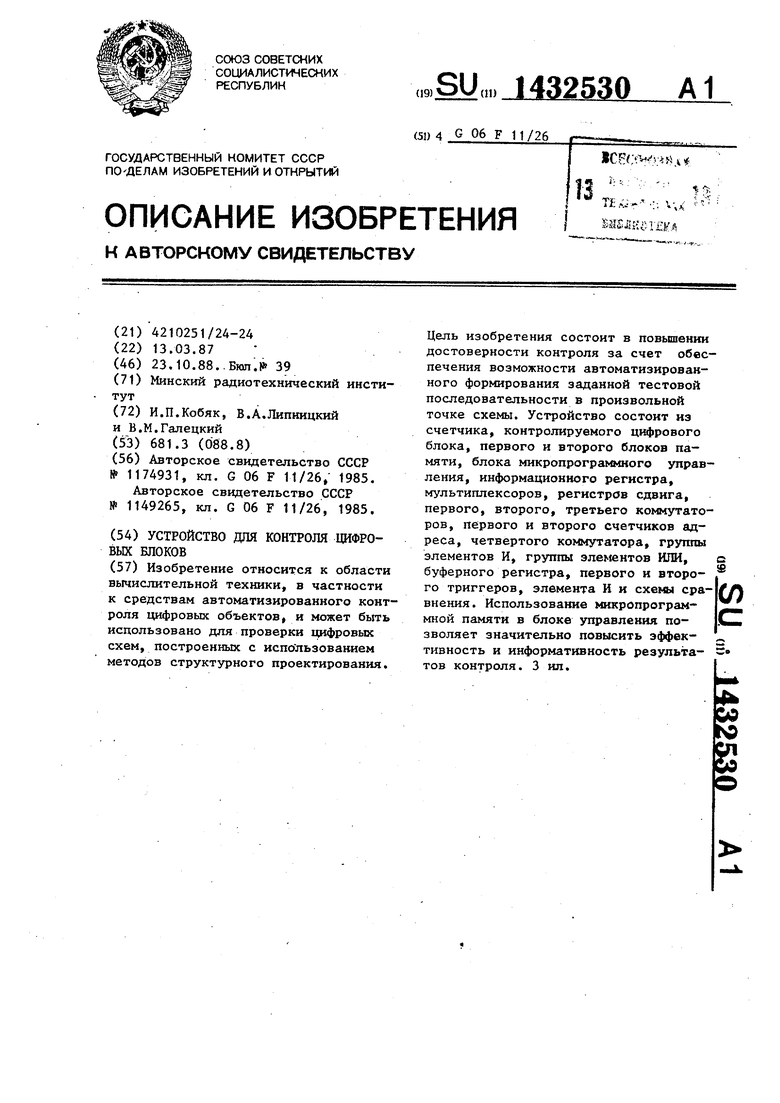

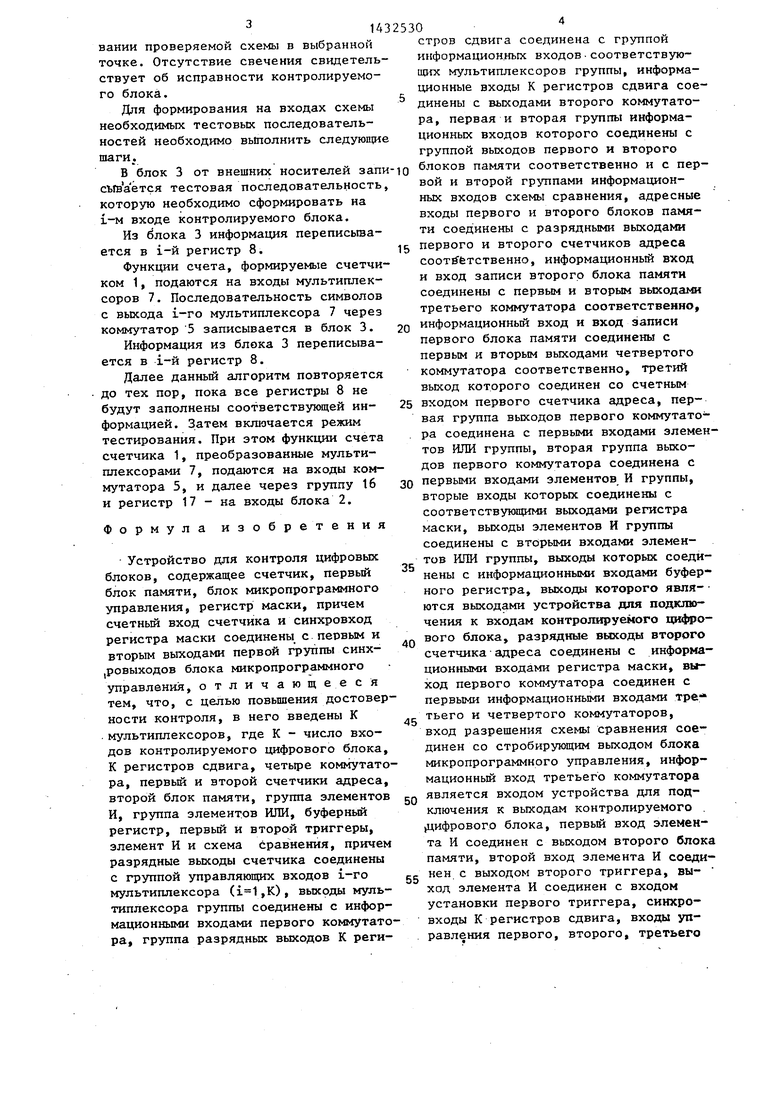

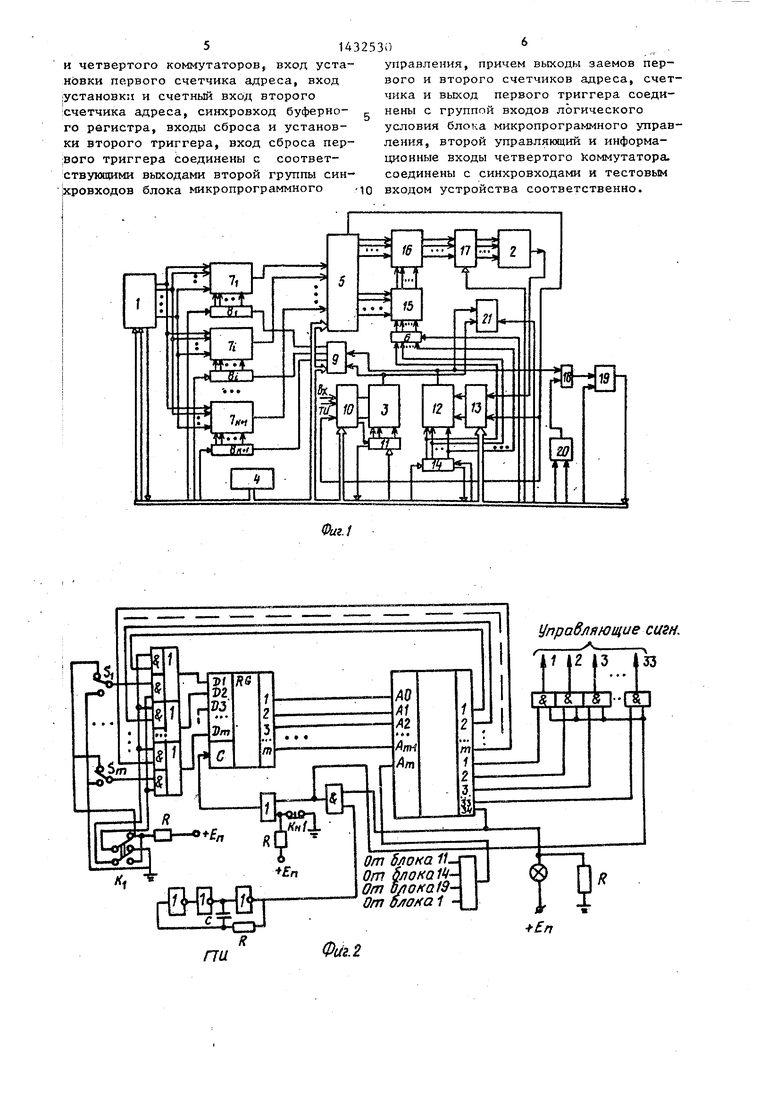

На фиг. 1 представлена блок-схема устройства;. на фиг. 2 - функциональная схема блока управленияj на фиг.З- функциональная схема схемы сравнения

Устройство (фиг.1) содержит счет- чик 1, контролируемый цифровой блок 2, блок 3 памяти, блок 4 микропрограммного управления, коммутатор 5, регистр 6 маски, К мультиплексоров 7, К регистров 8 сдвига, коммутатор 9, коммутатор 10, первый счетчик И .адреса, блок 12 памятн, коммутатор 13, счетчик 14 адреса, группу 15 элементов И, группу 16 элементов ИЛИ, буферный регистр 17, элемент И 18, . триггеры 19 и 20, схему 21 сравнения

Устройство работает следукяцим образом.

В зависимости от структуры блока 2 может быть выбран необходимый режим работы формирователя тестов. Рассмотрим, например, тестирование схемы, реализованной с использованием структурных методов контролепригод- ного проектирования. Сущность контроля такого устройства состоит в раздельном тестировании комбинационной и последовательной частей. Режим создания заданной тестовой последова14

.12) С помощью счетчика 1 кодовые комбинации перебираются на входах

тельности в произвольной комбинацион-40 мультиплексоров 7. Последовательность ной части схемы укрупненно описывается следующим алгоритмом.

символов с выхода произвольного мультиплексора переписывается в блок 3. 13) Вместо эталонного изделия к устройству подключается цифровой

1) В блок 3 от внешнего носителя записывается двоичная последовательсимволов с выхода произвольного мультиплексора переписывается в блок 3. 13) Вместо эталонного изделия к устройству подключается цифровой

ность, в которой логическая 1 при- 45 блок 2 и функции счета, преобразовансутствует только з ячейке памяти с адресом, кратным степени-двойки.

2)Из блока 3 информация переписывается в один из регистров 8..

3)Процедура, описанная в первом и втором шаге, повторяется столько раз, сколько входов имеет цифровой блок 2. При этом необходимо, чтобы единичный бит информации каждый раз присутствовал в новой ячейке памяти, адрес которой кратен степени двойки.

4)Функции счета, формируемые счетчиком 1, через мультиплексоры 7 подаются на входы коммутатора 5 и че50

55

ные мультиплексорами 7 через коммутатор 5, группу 15, группу 16, регистр 17, подаются на входы контролируемого цифрового блока 2.

14)Реакция контролируемого цифрового блока 2 в заданной точке в каждый такт времени через коммутатор 13 записьгаается в блок 12.

15)Осуществляется чтение блока 3 и блока 12 и сравнение считанной информации на схеме 21. Свечение индикатора по окончании сравнения свидетельствует о неправильномфункциониро10

е,

15

25302

рез элементы ИЛИ группы 16 и регистр

17 подаются на входы блока 2. Последовательность сигналов, снимаемая в каждый такт времени, записывается в блок 12.

5)Реакция контроля переписьшает- ся из блока 12 в один из регистров &.

6)С помощью счетчика 1 кодовые комбинации перебираются на входах мультиплексоров 7. Последовательность символов с выхода мультиплексора, опред(вленного в пункте 5, через коммутатор 5 записывается в блок 12.

7)Тестовая последовательность, которую необходимо сформировать в указанной выще точке блока 2, вводится через коммутатор 10 в блок 3.

8)Осуществляется перезапись информации из блока 3 в один из регистров 8.

9)С помощью счетчика 1 кодовые комбинации перебираются на входах мультиплексоров 7. Последовательность символов с выхода мультиплексора 7, определенного в пункте 8, через коммутатор 5 записывается в блок 3.

10)Информация из блока 3 переписывается во все рег истрй 8.

11)Блок 12 переводится в режим чтения, а триггер 20 устанавливается в единичное состояние. При считьша- нии первого единичного бита из блока 12 триггер 19 формирует сигнал управления для блока 4, что приводит к останову счетчика 14 и записи его содержимого в регистр 6.

.12) С помощью счетчика 1 кодовые комбинации перебираются на входах

20

25

30

35

40 мультиплексоров 7. Последовательность мультиплексоров 7. Последовательность

символов с выхода произвольного мультиплексора переписывается в блок 3. 13) Вместо эталонного изделия к устройству подключается цифровой

блок 2 и функции счета, преобразован0

5

ные мультиплексорами 7 через коммутатор 5, группу 15, группу 16, регистр 17, подаются на входы контролируемого цифрового блока 2.

14)Реакция контролируемого цифрового блока 2 в заданной точке в каждый такт времени через коммутатор 13 записьгаается в блок 12.

15)Осуществляется чтение блока 3 и блока 12 и сравнение считанной информации на схеме 21. Свечение индикатора по окончании сравнения свидетельствует о неправильномфункциониро

вании проверяемой схемы в выбранной точке. Отсутствие свечения свидетельствует об исправности контролируемого блока.

Для формирования на входах схемы необходимых тестовых последовательностей необходимо выполнить следуюп1и шаги.

В блок 3 от внешних носителей зап съгв а ется тестовая последовательность которую необходимо сформировать на i-M входе контролируемого блока.

Из блока 3 информация переписьгаа- ется в i-й регистр 8.

Функции счета, формируемые счетчиком 1, подаются на входы мультиплексоров 7. Последовательность символов с выхода i-ro мультиплексора 7 через коммутатор 5 записывается в блок 3.

Информация из блока 3 переписывается в i-й регистр 8.

Далее данный алгоритм повторяется до тех пор, пока все регистры 8 не будут заполнены соответствующей информацией. Затем включается режим тестирования. При этом функции счета счетчика 1, преобразованные мультиплексорами 7, подаются на входы коммутатора 5, и далее через группу 16 и регистр 17 - на входы блока 2.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее счетчик, первый блок памяти, блок микропрограммного управления, регистр маски, причем счетный вход счетчика и синхровход регистра маски соединены с первым и вторым выходами первой группы синх- |ровыходов блока микропрограммного управления, отличающееся тем, что, с целью повьш1ения достоверности контроля, в него введены К . мультиплексоров, где К - число входов контролируемого цифрового блока, К регистров сдвига, четыре коммутатора, первый и второй счетчики адреса, второй блок памяти, группа элементов И, группа элементов ИЛИ, буферный регистр, первый и второй триггеры, элемент И и схема сравнения, причем разрядные выходы счетчика соединены с группой управляющих входов i-ro мультиплексора (,К), выходы мультиплексора группы соединены с информационными входами первого коммутато- ра, группа разрядных выходов К реги5

0

5

стров сдвига соединена с группой информацион.ных входов соответствую- Щ1ГХ мультиплексоров группы, информационные входы К регистров сдвига соединены с выходами второго коммутатора, первая и вторая группы информационных входов которого соединены с группой выходов первого и второго блоков памяти соответственно и с первой и второй группами информационных входов схемы сравнения, адресные входы первого и второго блоков памяти соединены с разрядными выходами первого и второго счетчиков адреса cooTtffeTCTBeHHo, информационный вход и вход записи второго блока памяти соединены с первым и вторым выходами третьего коммутатора соответственно, информационный вход и вход записи первого блока памяти соединены с первым и вторым выходами четвертого коммутатора соответственно, третий выход которого соединен со счетным входом первого счетчика адреса, первая группа выходов первого коммутато- . ра соединена с первьми входами элементов ИЛИ группы, вторая группа выходов первого коммутатора соединена с 0 первыми входами элементов И группы, вторые входы которых соединены с соответствующими выходами регистра маски, выходы элементов И группы соединены с вторыми входами элементов ИЛИ группы, выходы которых соединены с информационными входами буферного регистра, выхода которого явля- ются выходами устройства для подключения к входам контролируемого цифрового блока, разрядные выходы второго счетчика адреса соединены с информационными входами регистра маски, выход первого коммутатора соединен с первыми информационными входами тре- тьего и четвертого коммутаторов, вход разрешения схемы сравнения сое динен со стробирующим выходом блока микропрограммного управления, информационный вход третьего коммутатора является входом устройства для подключения к выходам контролируемого цифрового блока, первый вход элемента И соединен с выходом второго блока памяти, второй вход элемента И соединен с выходом второго триггера, вы- ход элемента И соединен с входом установки первого триггера, синхро входы К регистров сдвига, входы управления первого, второго, третьего

5

0

5

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

Изобретение относится к области вычислительной техники, в частности к средствам автоматизированного контроля цифровых объектов, и может быть использовано для проверки цифровых схем, построенных с испо:пьзованием методов структурного проектирования. Цель изобретения состоит в повышении достоверности контроля за счет обеспечения возможности автоматизированного формирования заданной тестовой последовательности в произвольной точке схемы. Устройство состоит из счетчика, контролируемого цифрового блока, первого и второго блоков памяти, блока микропрограммного управления, информационного регистра, мультиплексоров, регистров сдвига, первого, второго, третьего коммутаторов, первого и второго счетчиков адреса, четвертого коммутатора, группы элементов И, группы элементов ИЛИ, с буферного регистра, первого и второ го триггеров, элемента И и схемы сравнения. Использование микропрограммной памяти в блоке управления позволяет значительно повысить эффективность и информативность результатов контроля. 3 ил. Sfi (Л С

па

Фаг. 2

Управляющие CUSH.

От блока -ГП

От йлока ЧА J От олона19- От 6/fOf(ct 1 -|

Еп

От SJIOKU S

9m SjtoKu /2

a

l-ТШп

52

От блока

Фи1.3

| Авторское свидетельство СССР 1174931, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-03-13—Подача