оо ел

оь о

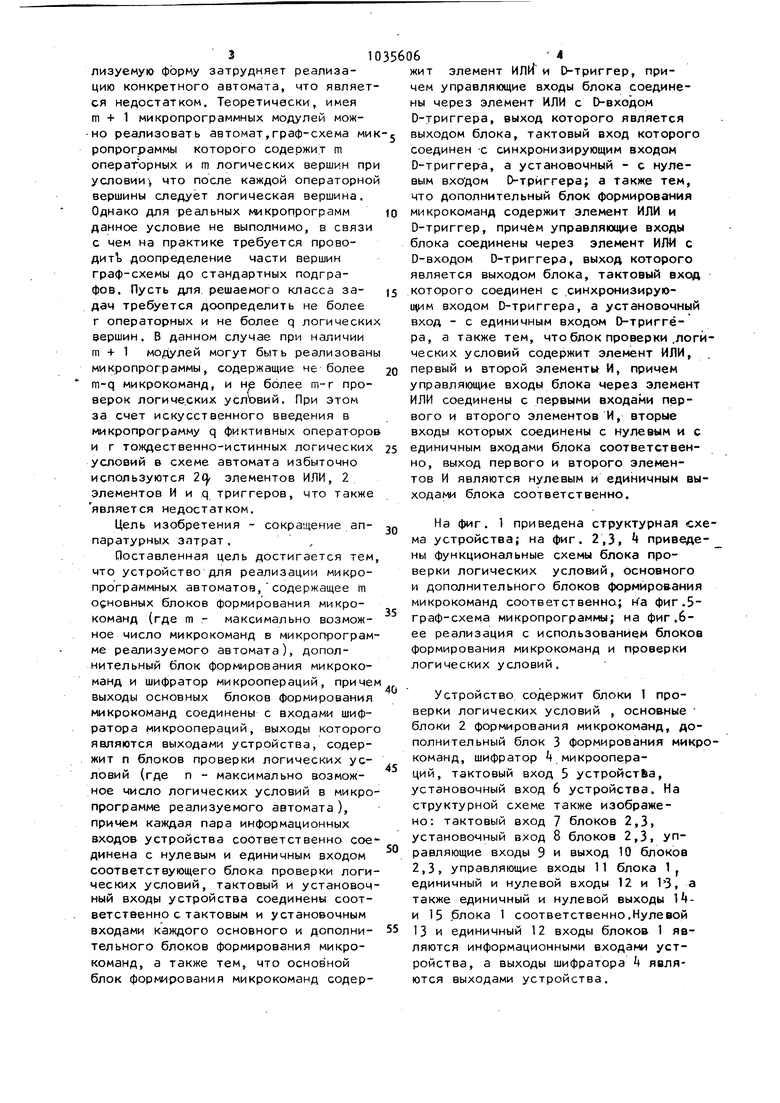

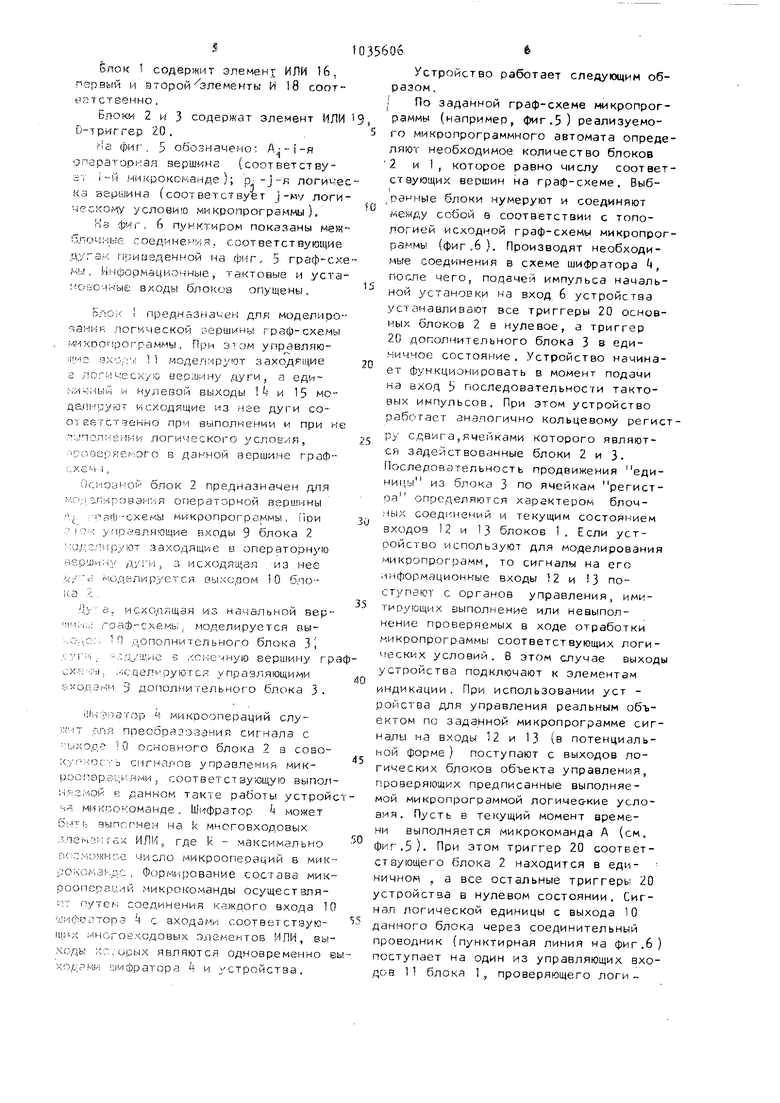

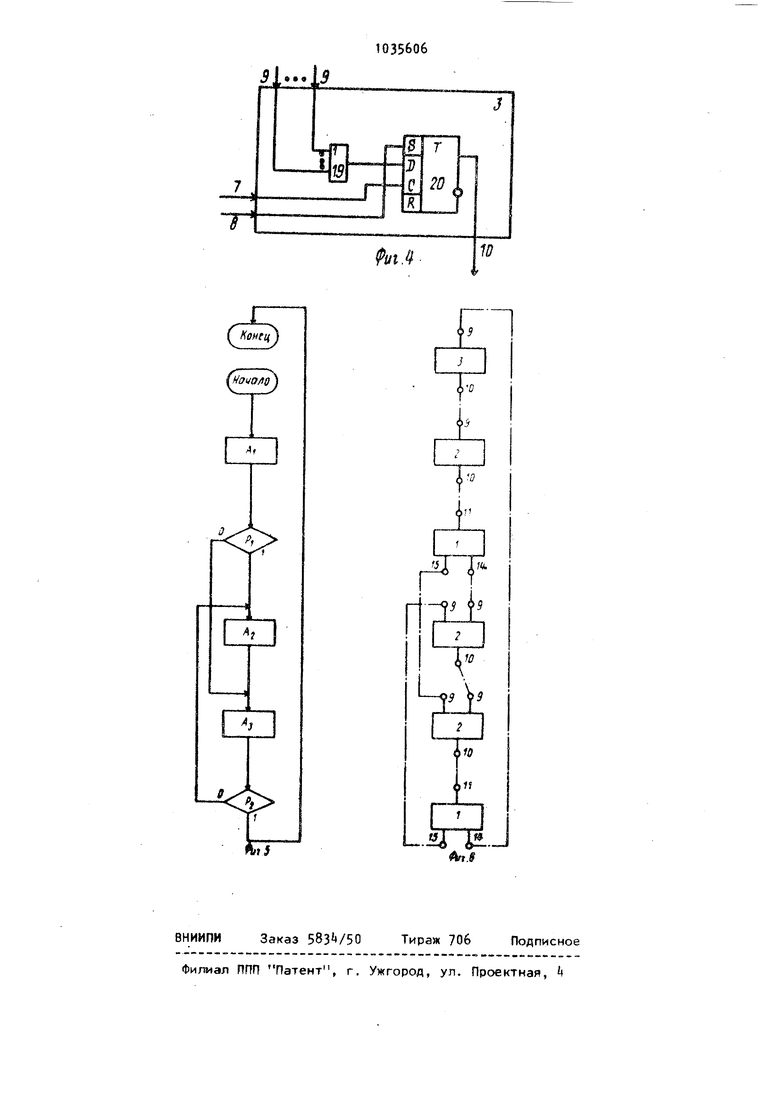

О5 2. Устройство по п. 1, о т л и чающееся тем, что основной блок формирования микрокоманд содержит элемент ИЛИ и О-триггер, при чем управляющие входы блока соедине ны через элемент ИЛИ с D-входом D-триггера,. выход которого является выходом блока, тактовый вход которо го соединен с синхронизирующим входом D-триггера, а установочный - с нулевым эходом D-триггера, 3 Устройство по п, 1, отличающееся тем, что дополнительный блок ров а ни я микропрограмм содержит элемент ИЛИ и О-триггер, причем управляющие входы блока соединены через элемент ИЛИ с 8ходом D-триггера, выход которого 6 является выходом блока, тактовый вход которого соединен с синхронизирующим входом D-триггера, а установочный аход - с единичным входом D-триггера. Ц. Устройство по п. 1, отличающееся тем, что блок проверки логических условий содержит элемент ИЛИ первый и второй элементы И, причем управляющие аходы блока через элемент ИЛИ соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с нулевым и с единичным входами блока соответственно, выходы первого и второго элементов И являются нулевым и единичным выходами блока соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1151962A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1278845A1 |

1. УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ МИКРОПРОГРАММНЫХ АВТОМАТОВ, содержащее m основных блоков формирования микрокоманд (где m - максимально возможное число микрокоманд в микропрогpdMMe реализуемого автомата), дополнительный блок формирования микрокоманд и шифратор микроопераций, причем выходы основных блоков формирования микрокоманд соединены с входами шифратора микроопераций, выходы которого являются выходами устройс-тва, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит п блоков проверки логических условий (где п - максимально возможное число логических условий в микропрограмме реализуемого автомата), причем каждая пара информационных входов устройства соот-, ветственно соединена с нулевым и единичным входом соответствующего блока проверки логических условий, тактовый и установочный входы устройства соединены соответственно с так(Л товым и установочным входами каждого основного и дополнительного- блоков формирования микрокоманд. 1

Изобретение относится к автомати,е и вычислительной технике , в мает ности к устройствам управления и кон роля,, и может быть использовано как ,цля моделирования микропрограмм, опи сывающих процесс функционирования уп равляющих автоматов, так и для управ ления исполнительными устройствами объектов управления по заданной микропрограмме , Известно устройство для реализации конечных автоматов на вмчислительной среде, содержащее вычислительную сре ду автомат настройки, дешифраторы, триггерЫр элементы . Недостатками этого устройства являются сложность схемы и большой объ ем оборудования. Наиболее близким техническим решением к изобретению является микропрограммный автомат, содержащий груп пу микропрограммных модулей, выходы которых через шифратор микроопераций соединены с выходами автомата. Настройку автомата на заданную микропрограмму осуществляют путем соответстзующей коммутации входов -л аыходов микропрограммных модулей. Для зтого выполняют следующее: зыдеЛйют нз граф-схеме реализуемой микропрограммы стандартные подграфы, предс зляющие собой последовательное соединение операторной и логической вершины; доопределяют до стандартного подграфа оставшиеся операторные вершины (кроме начальной ) введением тождественно-истинных логических вершин; доопределяют до стандартного подграфа оставшиеся логические вершины введением фиктивных операторных вершин; сопоставляют с каждым стандартным подграфом соответствующий микропрограммный модуль; сопоставляют с каждым стандартным подграфом соответствующие информационные аходы автомата ,, а для подграфов ,содержащих тождественно-истинные логические вершины, предусматривают специальный вход для нейтрализации неиспользуемого нулевого выхода соответствующего микропрограммного модуля; сопоставляют с каждым стандартным подграфом уставоночные входы соответствующего микропрограммного моIдуля, указав для них номера тех микропрограм ых модулей, выходные сигналы которых должны быть использованы для возвращения данного микропрограммного модуля 8 исходное состояние; производят соединение входов и выходов используемых микропрограммных модулей в соответствии с топологией полученной структурно-реализуемой граф-схемой микропрограммы , Необходимость преобразования исходной граф-схемы в структурно-реализуемую форму затрудняет реализацию конкретного автомата, что является недостатком. Теоретически, имея m + 1 микропрограммных модулей можно реализовать автомат,граф-схема микропрограммы которого содержит m операторных и m логических вершин пр условии- что после каждой операторно вершины следует логическая вершина. Однако для реальных микропрограмм данное условие не выполнимо, в связи с чем на практике требуется проводи тТэ доопределение части вершин граф-схемы до стандартных подграфов. Пусть для. решаемого класса задач требуется доопределить не более г операторных и не более q логически вершин. В данном случае при наличии m + 1 модулей могут быть реализован микропрограммы, содержащие не более m-q микрокоманд, и не более т-г проверок логиче.ских условий. При этом за счет искусственного введения в wiKponporpaMMy q фиктивных операторо и г тождественно-истинных логических условий в схеме автомата избыточно используются 2С элементов ИЛИ, 2 элементов И и q триггеров, что также является недостатком. Цель изобретения - сокращение аппаратурных затрат. , Роставленная цель достигается тем что устройство для реализации микропрограммных автоматов,содержащее m основных блоков формирования микрокоманд (где m - максимально возможное число микрокоманд в микропрограм ме реализуемого автомата), дополнительный блок формирования микрокоманд и шифратор микроопераций, приче выходы основных блоков формирования микрокоманд соединены с входами шифратора микроопераций, выходы которог являются выходами устройства, содержит п блоков проверки логических условий (где п - максимально возможное число логических условий в микро программе реализуемого автомата ), причем каждая пара информационных входов устройства соответственно сое динена с нулевым и единичным входом соответствующего блока проверки логи ческих условий, тактовый и установоч ный входы устройства соединены соответственно с тактовым и установочным входами каждого основного и дополнительного блоков формирования микрокоманд, а также тем, что основной блок формирования микрокоманд содер1035606

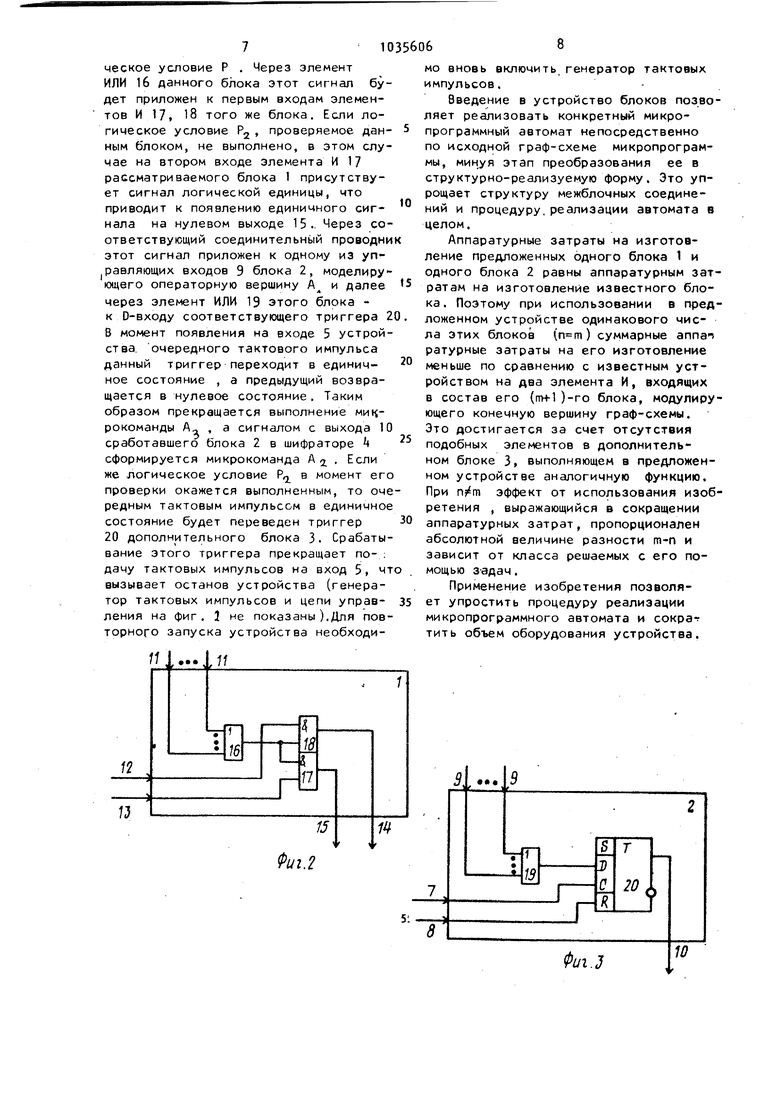

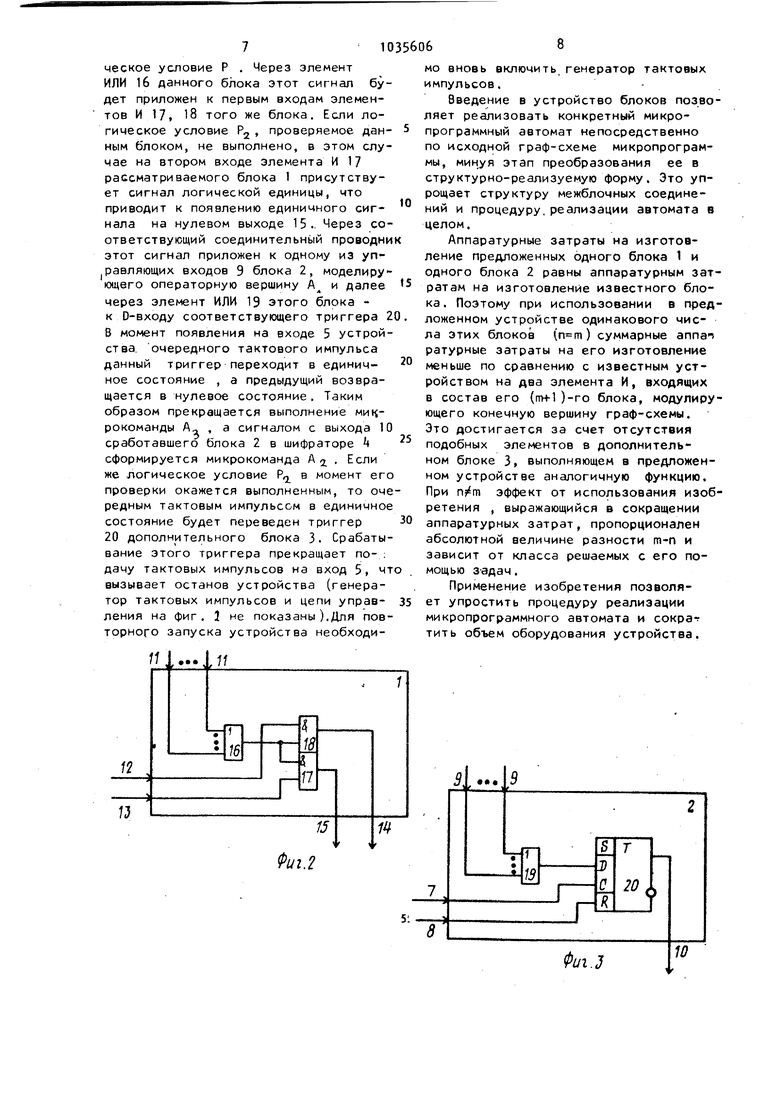

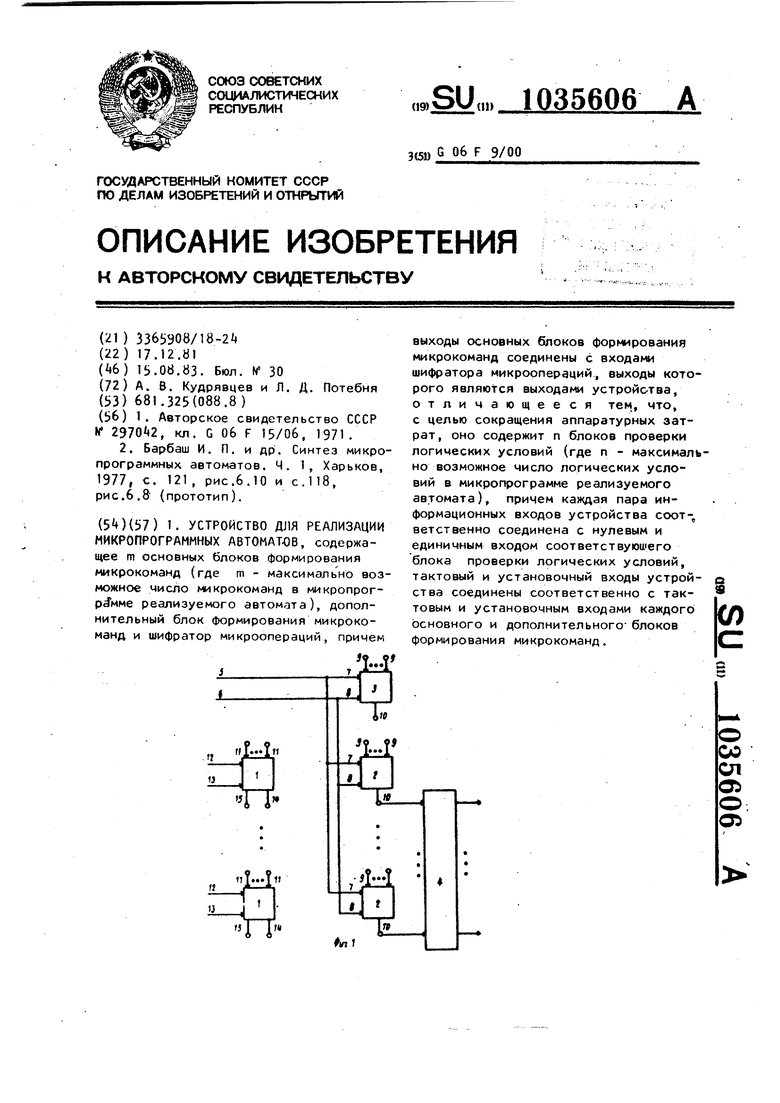

жит элемент ИЛИ и D-триггер, причем управляющие входы блока соединены через элемент ИЛИ с Ьвходом D-триггера, выход которого является выходом блока, тактовый вход которого соединен -с синхронизирующим входом D-триггер-а, а установочный - с нулевым входом D-трйггера; а также тем, что дополнительный блок формирования микрокоманд содержит элемент ИЛИ и D-триггер, причём управляющие входы блока соединены через элемент ИЛИ с D-входом О-триггера, выход которого является выходом блока, тактовый вход которого соединен с .синхрс 1изиру10щим входом D-триггера, а установочный вход - с единичным входом D-триггёра, а также тем, что блок проверки .логических условий содержит элемент ИЛИ, первый и второй элементы И, причем управляющие входы блока через элемент ИЛИ соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с нулевым и с единичным входами блока соответственно, выход первого и второго элементов И являются нулевым и единичным выходами блока соответственно. На фиг. 1 приведена структурная схема устройства; на фиг. 2,3, приваде- ны функциональные схемы блока проверки логических условий, основного и дополнительного блоков формиро&ания микрокоманд соответственна; на фиг.5граф-схема микропрограммы; на фиг .6ее реализация с использованием блоков формирования микрокоманд и проверки логических условий. Устройство содержит блоки 1 проверки логических условий , основные блоки 2 формирования микрокоманд, дополнительный блок 3 формирования микрокоманд, шифратор i микроопераций, тактовый вход 5 устройстЬа, установочный вход 6 устройства. На структурной схеме также изображено: тактовый вход 7 блоков 2,3, установочный вход 8 блоков 2,3, управляющие входы 9 и выход 10 блоков 2,3, управляющие входы 11 блока 1, единичный и нулевой входы 12 и , а также единичный и нулевой выходы 15 блока 1 соответственно.Нуле вой 13 и единичный 12 входы блоков 1 являются информационными входами устройства, а выходы шифратора являются выходами устройства. Блок 1 содержит элемен| ИЛИ 16, первьгй и агорой элементы И 18 соот еатственно. Блоки 2 и 3 содержат элемент ИЛ )-триггер 20 . На фиг, 5 обозначено: операторная, вершина (соответст ву ат (и мирсрококанде); Р.-к логиче ка вершина (соответствует j-му логи ческому условию микропрограммы), п8 фиг,, 6 Пунктиром ПОКЗЗаНЫ MSJ 5яоь;;-;|;1е соединения, соответствующие приведенной на фиг.. 5 граф-с формационные, тактовые и уст входы блоков опущены. Бло: 1 предназна1-.:ен для моделиро :чзния логической 1- 2ршины граф-схемы j-iiiKDOnporpaMMbi, При упрэвляюзцие гахо/;я 1 1 риоделируют 3 логицескуй вершину дуги, а ед ;-;иЧ|-1ЫЙ и нулевой выходы 1 и 15 моделнруат исходящие из .нее дуги соОт еетст зенно при выполнении и при н /упо.ппеыии логи1- еского условия, |рооеряег|Ого в данной вершине графсхе .ii , Ос нозной блок 2 предназначен для мг;; -щирпвану я огюрбторной вершины /: ..хемь микропрограмм.ы, :1ри : io.v управляющие входы 9 блока 2 :a;,:Cji 1руют заходящие в операторную вершч:1у 3 исходящая из нее bj.; моделируется 0ь хсдом 10 блоj ( , исходящая из начальной верм ч;-и:,; граф-схемы; моделируется вы,о,,о:; О дополни тел ьного блока 3i :.цу:1:ие в ,снечную вершину гр ;сцел|--руются упразляющими 9 дополии1ельного блока 3 | 1;тфпатор ч микрооперации для преобраэозэния сигнала с .ходг ; О основного блока 2 в СОБО-; :-;ость С11гналов управления мик}опарзциями. соответствующую выпо/ ;-(Язмой в данном такте работы устрой ;- )МИгсрокоманде, Шифратор может зыпсгнен на k многовходовых .лемэ:-; rax ИЛИ, где k - максимально пг:.У о:-кное число микроопераций в мик рокскзь.дс , Формирование состава мик роопсраи1Й микрокоманды осущесталяi-r: пз/тем соединения кзждого входа 1 о.;ифсотора 4 с входами соответстзуюiij.i-ix чногогэходовых элементов ИЛИ, вы ходы ;.о;орых являются одновременно ходрми шифратора ч и устройства. Устройство работает следующим образом . I По заданной граф-схеме микропрограммы (например, фиг.5) реализуемого микропрограммного автомата определяют необходимое количество блоков 2 и , которое равно числу соответствующих вершин на граф-схеме. Выб рамные блоки нумеруют и соединяют мемду собой а соответствии с топологией исходной граф-схемы микропрограммы (фиг.6), Производят необходимые соединения в шифратора , поапе чего, подачей импульса начальной j/становки на вход 6 устройства устанавливают все триггеры 20 основных блоков 2 в нулевое, а триггер 20 дополнительного блока 3 в единичное состояние . Устройство начинает функционировать в момент подачи на вход 5 последовательности тактовых импульсов. При этом устройство работает аналогично кольцевому регистру сдвига,ячейками которого являются задействованные блоки 2 и 3Последовательность продвижения единицы из блока 3 по ячейкам регистра определяются характером блочных соединений и текущим состоянием входов 12 и 13 блоков 1. Если устройство используют для моделирования микропрограмм, то сигналы на его информационные входы 2 и 13 поступают с органов управления, имитирующих выполнение или невыполнение проверяемых в ходе отработки микропрограммы соответствующих логических условий. В этом случае выходы устройства подключают к элементам индикации. При использовании уст ройства для управления реальным объектом по заданной микропрограмме сигналы на входы 12 и 13 (в потенциальной форме ) поступают с выходов логических блоков объекта управления, проверяющих предписанные выполняемой микропрограммой логичео-кие условия. Пусть в текущий момент времени выполняется микрокоманда А (см. фиг.5). При этом триггер 20 соответстаующего блока 2 находится в единичном , а все остальные триггеры 20 устройства в нулевом состоянии. Сигнал логической единицы с выхода 10 данного блока через соединительный проводник (пунктирная линия на фиг.6) поступает на один из управляющих входов 11 блока 1, проверяющего логическое условие Р . Через элемент ИЛИ 16 данного блока этот сигнал будет приложен к первым входам элементов И 17, 18 того же блока. Если логическое условие Pj , проверяемое данным блоком, не выполнено, в этом случае на втором входе элемента И 17 рассматриваемого блока 1 присутствует сигнал логической единицы, что приводит к появлению единичного сигнала на нулевом выходе 15.. Через соответствующий соединительный проводни этот сигнал приложен к одному из управляющих входов 9 блока 2, моделирующего операторную вершину А и далее через элемент ИЛИ 19 этого блока к D-входу соответствующего триггера 2 В момент появления на входе 5 устройства, очередного тактового импульса данный триггер переходит в единичное состояние , а предыдущий возвращается в нулевое состояние. Таким образом прекращается выполнение мич рокоманды А., , а сигналом с выхода 10 сработавшего блока 2 в шифраторе 4 сформируется микрокоманда А Если же логическое условие Р в момент его проверки окажется выполненным, то оче редным тактовым импульсом в единичное состояние будет переведен триггер 20 дополнительного блока 3. Срабатывание этого триггера прекращает по- : дачу тактовых импульсов на вход 5, чт вызывает останов устройства (генератор тактовых импульсов и цепи управления на фиг, J не показаны ),Для пов торного запуска устройства необходиМО вновь включить, генератор тактовых импульсов. Введение в устройство блоков позволяет реализовать конкретный микропрограммный автомат непосредственно по исходной граф-схеме микропрограммы, минуя этап преобразования ее в структурно-реализуемую форму. Это упрощает структуру межблочных соединений и процедуру,реализации автомата в целом. Аппаратурные затраты на изготовление предложенных одного блока 1 и одного блока 2 равны аппаратурным затратам на изготовление известного блока. Поэтому при использовании в предложенном устройстве одинакового числа этих блоков () суммарные annan ратурные затраты на его изготовление меньше по сравнению с известным устройством на два элемента И, входящих в состав его (пН-1 )-го блока, модулирующего конечную вершину граф-схемы. Это достигается за счет отсутствия подобных элементов в дополнительном блоке 3, выполняющем в предложенном устройстве аналогичную функцию. При эффект от использования изобретения , выражающийся в сокращении аппаратурных затрат, пропорционален абсолютной величине разности m-n и зависит от класса решаемых с его помощью з-адач. Применение изобретения позволяет упростить процедуру реализации микропрограммного автомата и сокра- тить объем оборудования устройства.

Фи2.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР К , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Барбаш И | |||

| П | |||

| и др | |||

| Синтез микропрограммных автоматов | |||

| Ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ребристый каток | 1922 |

|

SU121A1 |

Авторы

Даты

1983-08-15—Публикация

1981-12-17—Подача