ел

4

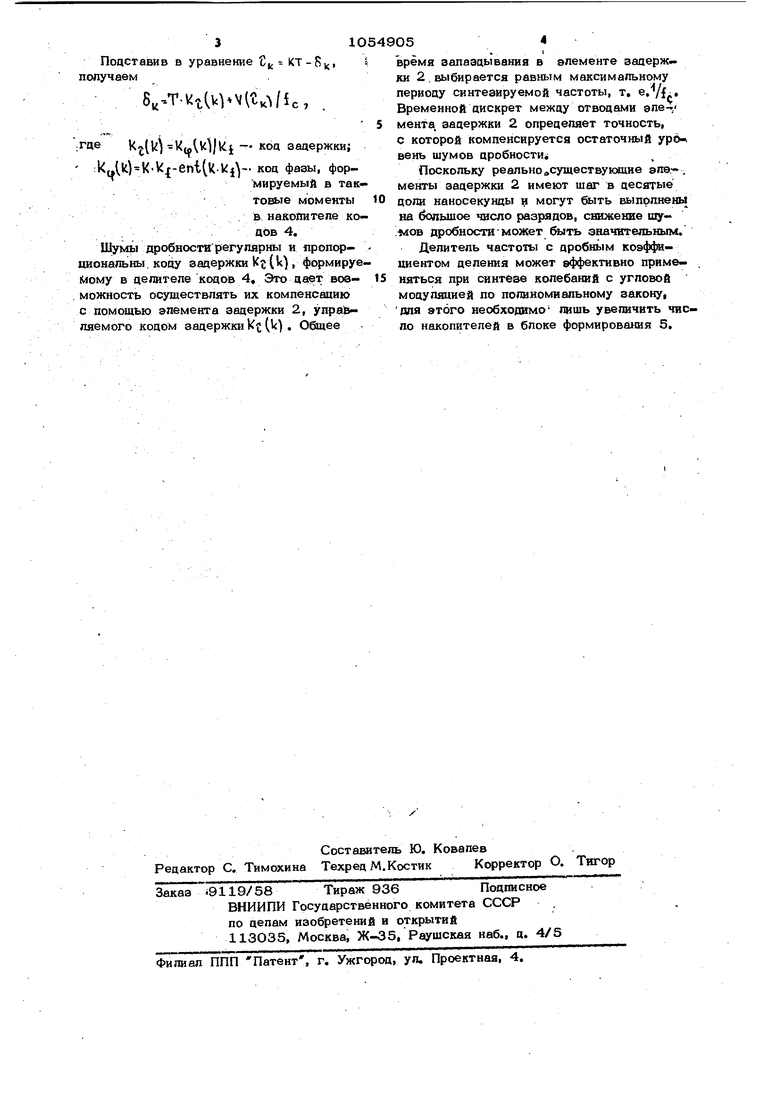

;о Изобретение относится к радиотехнике и может использоваться в иамернтепь.ной аппаратуре и в системах связи при синтезе сигналов с фиксированной и меня ющейся частотой. Известен делитель частоты с дробным коэффициентом деления, оодержаншй последовательно соединенные программируемый делитель и устройство коррекции ijpe менного псжожения импульсов, а также последовательно соединенные блок управления и анализатор временного положения выходных импульсов, первый .выход которого соединен с управляющим входом программируемого делителя, а первый и второй входы анализатора временного положешя импульсов соединены соответс веннэ со входом программируемого делителя ij ., Недостатки известного делителя частоты с дробным коэффициентом деления высокий уровень шумов дробности и мала скорость.перестройки. Наиболее близким по технической сущ- ности к предлагаемому является делитель частоты с Дробным коэффициентом, делени содержащий последовательно соединенные программируемый делитель частоты и элемент задержки, а таюке делитель код и накопитель кодов, выход переполнения которого подключен к первому входу прог-раммируемого делителя частоты 2 . В этом делителе частоты с дробным коэффициентом деления код управлеьгая запаздывания в элементе задерлжи формируется в накопителе кодов, с конечной точностью и поэтому код управления временем запаздывания определяется с ошибкой, что прнвоант к повышению уровня шумов дробности в выходном сигнале делителя. Цель изобретения уменьшение нерав номерности следования выходных импульсов при одновременном повышении быстродействия. Поставленная цель достигается тем, что в делитель частоты, с дробным коэффициентом деления, содержащем последовательно соединенные программируемый делитель частоты и элемент задержки, а также делитель кодов и накопитель кодов, выход переполнения которого подключен к первому входу программируемого депитепя частоты, введен блок формирования кода частоты, кодовые выходы которого соединен) с управпякхцими входами программируемого делителя частоты, пер.вой группой входов делителя кодов и кодовыми входами накопителя кодов, пораз- рядные выходы которого соединены со второй группой входов делителя кодов, при этом тактовые входы накопителя ко дов и блока формирования Kofcia частоты объединены и подключены к выходу прог «раммируемого делителя частоты, а выходы делителя кодов соединены с управляющими входами элемента задержки, На чертеже представлена структурная электрическая схема делителя частоты с дробным коэффициентом деления. Делитель частоты с дробным коэффициентом деления содержит программируемыйделитель частоты 1,элемент задержки 2,делитель кодов 3, накопитель кодов 4, и блок формирования 5 кода текущей чистоты. Делитель частоты с дробным коэффициентом деления работает следующим образом. На вход программируемтэго делителя частоты 1 поступает импульсная последовательность фаза которых меняется по закону eltbZftic-b -MlM, где IP - входная частота; V(t)- фааовай ошибка. Блок формирования 5 при этом обеспечивает формирование постоянного на требуемом временном интервале кода K синтезируемой частоты ( . Целая часть этого коца задает коэффициент деления программируемого делителя частоты 1, а дробная-поступает на накопитель кодов 4, по каждому из импульсов переполнения которого программируемый делитель частоты 1 исключает один импульс из входной последовательности. В результате этого на выход программируемого делителя частоты 1 проходят импульсы с номерами 3) ent (kK.) , гдееп1(и) -оператор, выделяющий .целую часть числа Xf ; K.j-ij.T - код синтезируемой частоты; . К - номер импульса на выходе программируемого делителя частоты 1. Из-за дробности числа f импульсы на выходе программируемого делителя частоты 1 неравномерны даже ). Моменты )4 появления импульсов на выходе программируемого делителя частоты 1 находятся ИЗ уравнения i,iv.-Vii K)/2iV Отличие (отКТ приводит к появленикумов дробности. Подставив в уравнение €j, KT-Su, получаем .(k itкWic, . КjlkbK( - код задержки; )K-k|-enl((. код фазы, формируемый в так товые моменты в накоПитепе ко .дов 4. Шумь дробности регулярны и лропор ционапьны коду задержки t(} , формируе мому в делителе кодов 4, Это даэт возможность осушествпять их компенсацию с помощью элемента задержки 2, управляемого кодом задержки K (V() . Общее 1 О5 время запаздывания в элементе задержки 2 . выбирается равным максимальному периоду синтезируемой частоты, т, e.Vf . Временной дискрет между отводами эле.. мента, задержки 2 определяет точность, с которой компенсируется остаточный ур6- вень шумов дробности Поскольку реально существующие э1та. , менты задержки 2 имеют шаг в десятые доли наносекунды 1я могут быть выполнены на большое число разрядов, снвженве шу.дов дробности может быть значительным. Делитель частоты с дробнь1м коэффициентом деления может эффективно применяться при синтезе колебаний с угловой модуляцией по полиномиальному закону, для этого необходимо лишь увеличить число накопителей в блоке формирования 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Управляемый делитель частоты | 1981 |

|

SU982200A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Датчик сигнала ошибки | 1984 |

|

SU1210201A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОЫ, НЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий поспецовательно соединенны е программируемый целитель частоты и элемент задержки, в также целитель кодов и. накопитель кодов, выход переполне- : НИИКоторого поцкпючен к первому входу программируемого делителя частоты, отличающийся тем, что, с целью уменьшения неравномерности следования выходных импульсов при одновременном повыше ши быстродейртвия, введен блок формирования кода частоты, кодовые выходы которого соединены с управляющими входами программируемого делителя частоты, первой группой входов делителя кодов и кодовыми входами накопителя кодов, поразрядные выходы которого соединены со второй группой входов делителя кодов, при этом тактовые входы накопителя кодов и блока формирования лода частоты объединены и подключены к выС ,XGuf программируемого делителя частоты, а выходы де лителя кодов соединены с (Л управляющими входами элемента задерхс- ки. с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Синтезатор частот | 1976 |

|

SU629632A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3976945, кп | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-15—Публикация

1981-07-14—Подача