(54) ИНТЕГРО-ДИФФЕРЕНЦИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для моделирования и управления динамическими объектами в различных отраслях промышленности.

Известны точные цифровые интегродифференциальные устройства типа дифференциальных анализаторов, которые содержат ряд цифровых интеграторов, коммутируемых между собой согласно заданному интегро-дифференциальному преобразователю l.

Недостатками таких интегро-диффереициальных устройств являются низкое быстродействие и сложность реализации.

Наиболее близким к данному техническому решению является интегродифференциальный вычислитель, содержа1дий четыре регистра, первый суммаiop, два блока формирований дополнительного кода, блок знака, блок синхронизации, восемь элементов И, три элемента Р1ЛИ и элемент задержки, причем первая входная шина устройства соединена с первым входом блока знака, первый .выход которого соединен с первой выходной шиной устройства, выход первого сумматора соединен с входом первого perticTpa и

вторым входом блока знака, второй выход которого соединен с первыми входами первого и второго блоков формирования дополнительного кода, блик синхронизации соединен первым выходом с третьим входом блока знака, вторым выходом - с первыми входами первого, второго и третьего триггеров, третьим выходом - с вторым

10 входом первого триггера и четвертым выходом - с вторым входом второго триггера, выход первого регистра соединен с входом элемента задержки и с первым входом первого элемента

15 И, выход и второй вход которого соединены соответственно с первым входом первого элемента ИЛИ и с прямым выходом первого триггера, выход элемента задержки соединен с вторым

20 входом первого блока Формирования дополнительного кода и с первым вхо-дом второго элемента И, второй вход и выход которого соединены соответственно с инверсным выходом первого

25 триггера и с вторым входом первого элемента ИЛИ, выход которого подключен к первому входу первого сумматора, второй триггер -соединен прямым выходом с первыми входами

30 третьего и четвертого элементов И

и инверсным выходом - с первыми входами пятого и aiecToro элементов И и с третьими входами первого и второго элементов И, выход первого блока формирования дополнительного кода соединен с второй выходной шиной устройства и с вторым входом третьего элемента И, выход которого подключен к первому входу второго элемета ИЛИ, второй вход и выход которого соединены соответственно с выходом пятого элемента И и с входом второго регистра, второй вход и выход четвертого элемента И соединены соответственно с второй входной шиной устройс ва и с первым входом третьего элемента ИЛИ, второй вход и выход шестого элемента И соединены соответственно с выходом второго регистра и с вторы входом третьего элемента ИЛИ, выход которого соединен с входом третьего регистра, который подключен выходом к второму входу пятого элемента И, выход четвертого регистра соединен с первым входом седьмого элемента Иу выход и второй вход которого соедине ны соответственно с вторым входом второго блока формирования дополнительного кода и с выходом третьего триггера, второй вход которого подключен к выходу восьмого элемента И, который соединен первым и вторым входами соответственно с выходом второго элемента ИЛИ и с пятым выходом блока синхронизации 2.

Однако известное устройство имеет относительно низкое быстродействие и недостаточную точность при заданном шаге вычислений.

Целью изобретения является повышение быстродействия устройства и точности вычислений.

Поставленная цель достигается тем, что в интегро-дифференциальныЯ вычислитель, содержащий первый, второй, третий и четвертый регистры сдвига, первый сумматор, блок знака, блок синхронизации, первый и второй блоки формирования дополнительного кода, первый, второй и третий триггеры, элемент задержки, первый, второй, трети{С, четвертый, пятый, шеетой, седьмой и восьмой элементы И, первый, второй и третий элементы ИЩ, причем вход первого регистра сдвига соединен с выходом первого сумматора, первый вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй - с выходом второго элемента И, первый вход первого элемента И соединен с выходом первого регистра сдвига и входом элемента задержки, второй вход первого элемента И соединен с прямым выходом первого триггера, первый вход второго элемента И

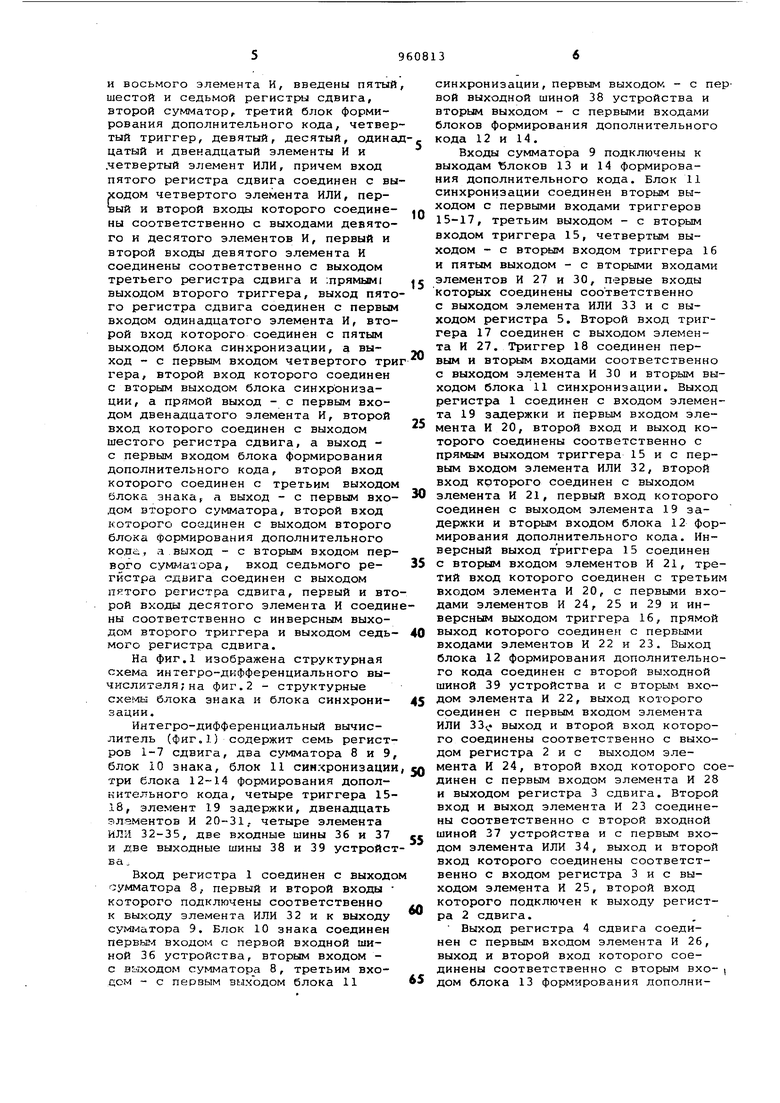

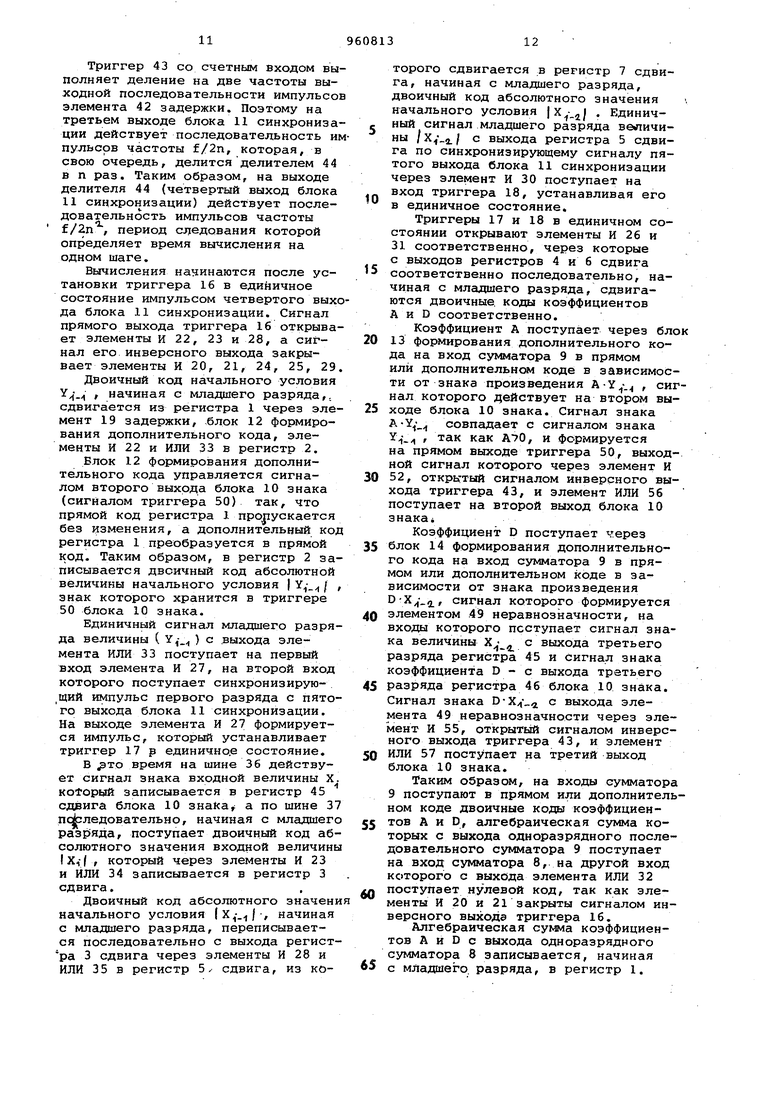

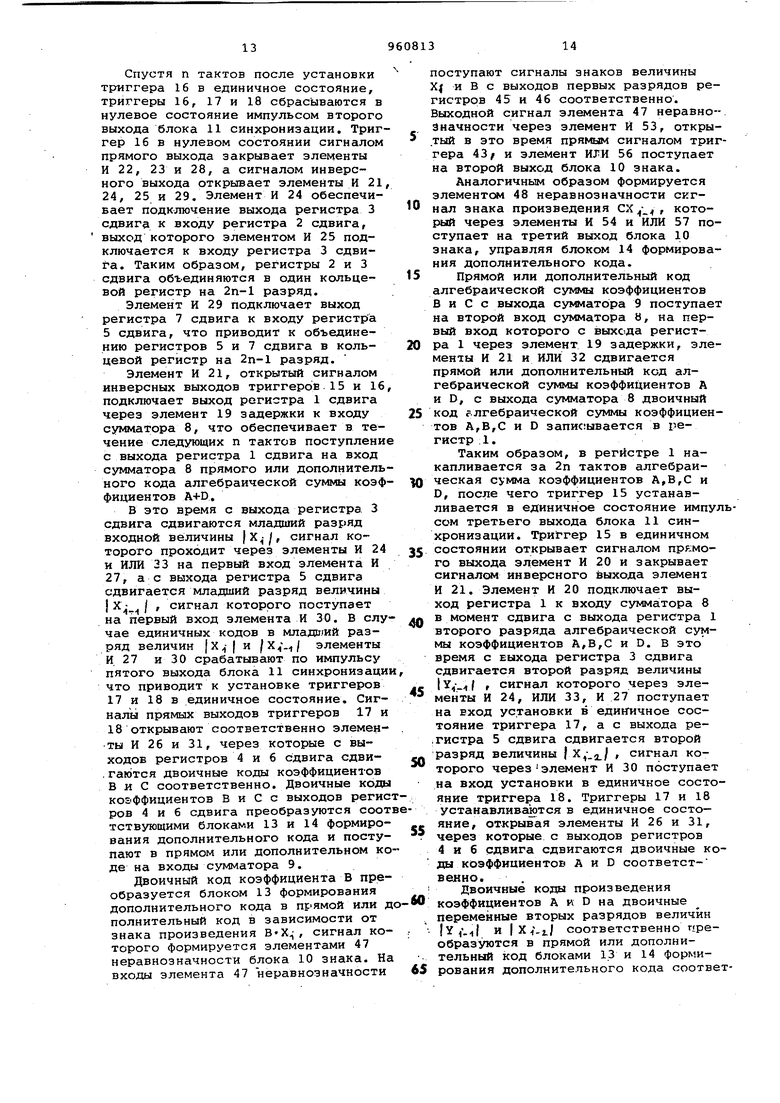

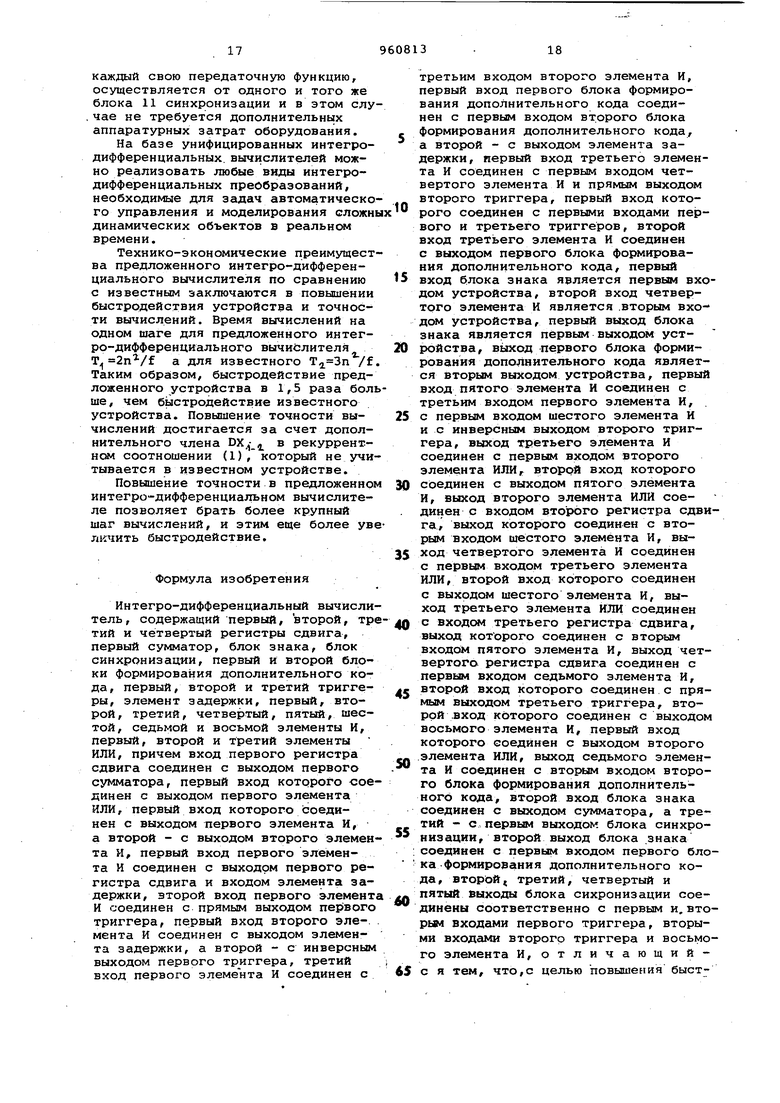

соединен с выходом элемента задержки, а второй - с инверсным выходом первого триггера, третий вход первого элемента И соединен с третьим входом второго элемента И, первый вход первого блока формирования дополнительного кода соединен с первым входом второго блока формирования дополнительного кода, а второй - с выходом элемента задержки., первый вход третьего элемента И соединен с первым входом четвертого элемента И и пряг-йом выходом второго триггера, первый вход которого соединен с первыми входами первого и третьего триггеров, второй вход третьего элемента И соединен с выходом первого блока формирования дополнительного кода, первый вход блока знака является первым входом устройства, второй вход четвертого элемента И является вторым входом устройства, первый выход блока знака является певым выходом устройства, выход первого блока формирования дополнительного кода является вторьом выходом устройства, первый вход пятого элемента И соединен с третьим входом первого элемента И, с первым входом шестого элемента И и с инверсньда выходом второго триггера, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход нторого элемента ИЛИ соединен с входом второго регистра сдвига, выход которого соединен с вторым входом шестого элемента И, выход четвертого элемента И соединен с- первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход третьего элемента ИЛИ соединен с входом третьего регистра сдвига, выход которого соединен с вторым входом пятого элемента И, выход четвертого регистра сдвига соединен с первым входом седьмого элемента И, второй вход которого соединен с прямым выходом третьего триггера, второй вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, выход седьмого элемента И соединен с вторым входом второго блока формирования дополнительного кода, второй вхо блока знака соединен с выходом сумматора, а третий - с первым выходом блока синхронизации, второй выход блока знака соединен с первым входом первого блока формирования дополнительного кода,второй, третий, четвертый и пятый выходы блока синхронязации соединены соответственно с первым и вторым входами первого триггера, вторыми входами второго триггера и восьмого элемента И, введены пятый шестой и седьмой регистры сдвига, второй сумматор, третий блок формироваиия дополнительного кода, четвер тый триггер, девятый, десятый, одниа цатый и двенадцатый элементы И и .четвертый элемент ИЛИ, причем вход пятого регистра сдвига соединен с вы ходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами девятого и десятого элементов И, первый и второй входы девятого элемента И соединены соответственно с выходом третьего регистра сдвига и ;прямым| выходом второго триггера, выход пято го регистра сдвига соединен с первым входом одинадцатого элемента И, второй вход которого соединен с пятым выходом блока синхронизации, а выход - с первым входом четвертого три гера, второй вход которого соединен с вторым выходом блока синхронизации, а прямой выход - с первым входом двенадцатого элемента И, второй вход которого соединен с выходом шестого регистра сдвига, а выход с первым входом блока формирования дополнительного кода, второй вход которого соединен с третьим выходом блока знака, а выход - с первым входом второго сумматора, второй вход которого соединен с выходом второго блока формирования дополнительного кода, а выход - с вторым входом пер вого сумматора, вход седьмого регистра сдвига соединен с выходом пятого регистра сдвига, первый и вт рой входы десятого элемента И соеди ны соответственно с инверсным выходом второго триггера и выходом седь мого регистра сдвига. На фиг.1 изображена структурная схема интегро-дифференциального вычислиталя;на фиг.2 - структурные cxerv i блока знака и блока синхронизации. Интегро-дифференциальный вычислитель (фиг,1) содержит семь регист ров 1-7 сдвига, два сумматора 8 и 9 блок 10 знака, блок 11 синхронизации три блока 12-14 формирования дополнительного кода, четыре триггера 15 .18, элемент 19 задержки, двенадцать элементов И 20-31.. четыре элемента ИЛИ 32-35, две входные шины 36 и 37 и две выходные шины 38 и 39 устройс ва , Вход регистра 1 соединен с выход сумматора 8,, первый и второй входы которого подключены соответственно к выходу элемента ИЛИ 32 и к выходу сум1 атора 9. Блок 10 знака соединен первым входом с первой входной шиной 36 устройства, вторым входом с выходом сумматора 8, третьим входом - с первым выхЪдом блока 11 синхронизации, первым выходом - с первой выходной шиной 38 устройства и вторым выходом - с первыми входами блоков формирования дополнительного кода 12 и 14. Входы сумматора 9 подключены к выходам Ълоков 13 и 14 формирования дополнительного кода. Блок 11 синхронизации соединен вторым выходом с первыми входами триггеров 15-17, третьим выходом - с вторым входом триггера 15, четвертым выходом - с вторым входом триггера 16 и пятым выходом - с вторыми входами элементов И 27 и 30, первые входы которых соединены соответственно с выходом элемента ИЛИ 33 и с выходом регистра 5. Второй вход триггера 17 соединен с выходом элемента И 27. Триггер 18 соединен первым и вторым входами соответственно с выходом элемента И 30 и вторым выходом блока 11 синхронизации. Выход регистра 1 соединен с входом элемента 19 задержки и первым входом элемента И 20, второй вход и выход которого соединены соответственно с прямым выходом триггера 15 и с первым входом элемента ИЛИ 32, второй вход которого соединен с выходом элемента И 21, первый вход которого соединен с выходом элемента 19 задержки и вторым входом блока 12 формирования дополнительного кода. Инверсный выход триггера 15 соединен с вторым входом элементов И 21, третий вход которого соединен с третьим входом элемента И 20, с первыми входами элементов И 24, 25 и 29 и инверсным выходом триггера 16, прямой выход которого соединен с первыми входами элементов И 22 и 23. Выход блока 12 формирования дополнительного кода соединен с второй выходной шиной 39 устройства и с вторым входом элемента И 22, выход которого соединен с первым входом элемента ИЛИ 33 выход и второй вход которого соединены соответственно с выходом регистра 2 и с выходом элемента И 24, второй вход которого соединен с первым входом элемента И 28 и выходом регистра 3 сдвига. Второй вход и выход элемента И 23 соединены соответственно с второй входной шиной 37 устройства и с первым входом элемента ИЛИ 34, выход и второй вход которого соединены соответственно с входом регистра 3 и с выходом элемента И 25, второй вход которого подключен к выходу регистра 2 сдвига. Выход регистра 4 сдвига соединен с первым входом элемента И 26, выход и второй вход которого соединены соответственно с вторым вхо-i дом блока 13 формирования дополнительного кода и с выходом триггера 17. Выход триггера 18 соединен с пер вым входом элемента И 31, второй вход и выход которого соединены соответственно с выходом регистра б сдвига и с первым входом блока 14 формирования дополнительного кода, второй вход которого подключен к третьему выходу блока 10 знака.

Второй вход и выход элемента И 28 соединены соответственно с прямым выходом триггера 16 и с первым входом элемента ИЛИ 35, второй вход и выход которого соединены соответственно с выходом элемента И 29 и с входом регистра 5 сдвига, выход которого соединен с входом регистра 7 сдвига, выход которого подключен к второму входу элемента И 29.

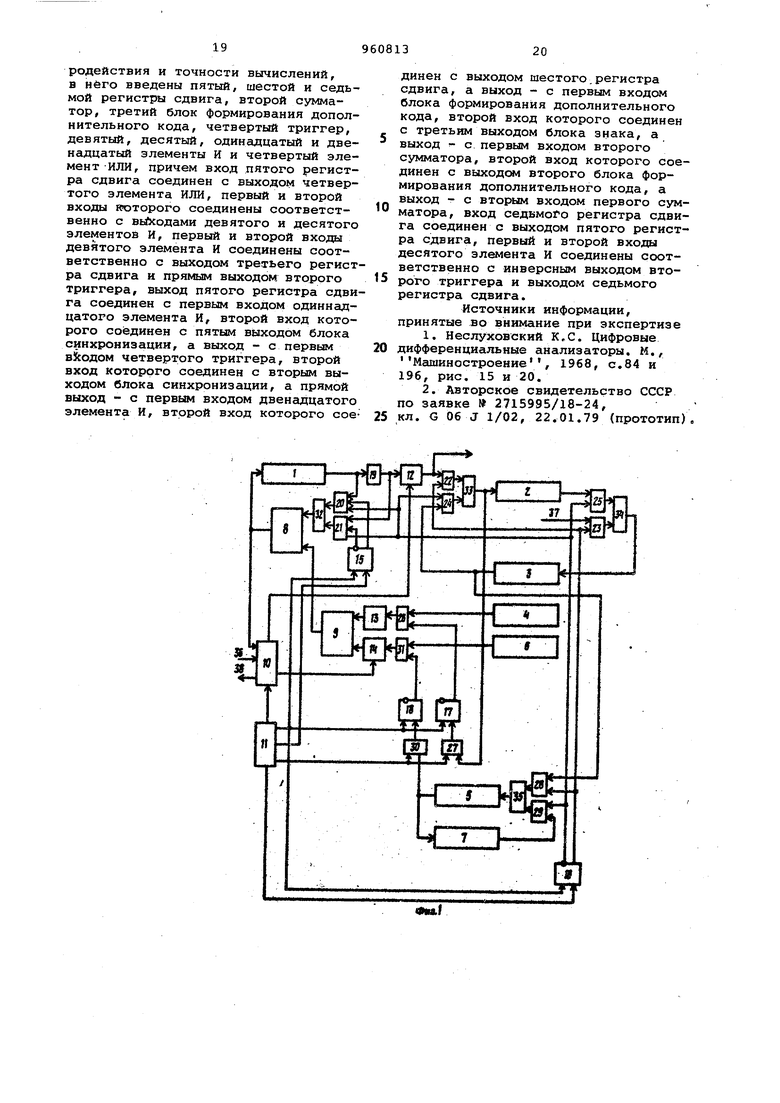

Блок 11 синхронизации (фиг.2) содержит генератор 40 тактовых сигналов, делитель 41, элемент 42 задержки, триггер 43 со счетным входом и делитель 44. Блок 10 знака (фиг.2) содержит трехразрядный регистр 45 сдвига, трехразрядный регистр 46, три элемента 47-49 неравнозначности, триггер 50, пять элементов И 51-55, два элемента ИЛИ 56 и 57, две входные шины 36 и 58, три выходные шины 38, 59 и 60. Блок 11 синхро низацик имеет выходные шины 61-64.

Выход генератора 40 тактовых сигналов соединен с входом :5елителя 41 выход которого соединен с выходной шиной 61 и с входом элемента 42 задержкИг выход которого подключен к выходной шине 62 и к счетному входу триггера 43, выход которого соединен с выходной шиной 63 и с входом делителя 44; выход которого соединен с выходной шиной 64, с шиной сдвига регистра 45 и с первым входом элемента И 51, второй вход и выход которог соединены соответственно с входной шиной 58 и с входом триггера 50, выход которого соединен с выходной шиной 38 н с первым входом элемента И 52, выход которого соединен с первы, входом элемента ИЛИ 56, выход котррого подключен к выходной шине .

Входная шина 36 соединена с информационнЕлм входом регистра 45 сдвиr i, три выхода которого подключены соответственно к первьзм входам элементов 47-49 неравнозначности, вторые входы которых соединены с соответствующими выходами регистра 46.

Выходы элементов 47-49 неравнозначности соединены соответственно с первыми входами элементов И 53-55. Вторые входы элементов И 53-54 соединены с прямым выходом триггера 43, инверсный выход которого соединен с вторыми входами элементов И 52 и 55, Второй вход элемента ЛИ 56 соединен с выходом элемента И 53. Выходы элементов И 54 и 55 Соединены с входами элемента ИЛИ 57, выход которого подключен к выходной шине 60.

Первым и вторым входами блока 10 знака являются шины 36 и 58 соответственно. Первым, вторым и третьим выходами блокаЮ знака являются шины 38, 59 и 60 соответственно. Вторым, третьим, четвертым и пятым выходами блока 11 синхронизации являются шины 61, 63, 64 и 62 соответственно.

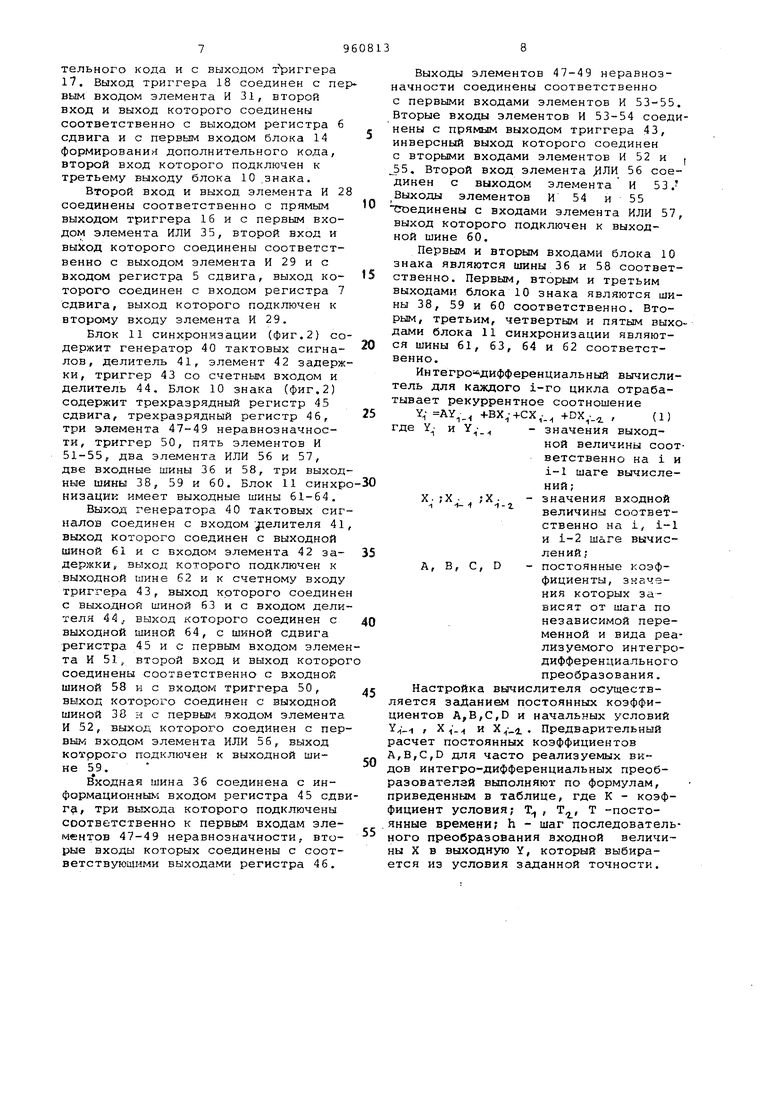

Интегро дифференциальный вычислитель для каждого i-ro цикла отрабатывает рекуррентное соотношение

Y,. ,-., +DX..,; , (1) где и . - значения выходной величины соответственно на i и i-1 шаге вычислений;

Х.;Х- ;Х. - значения входной величины соответственно на i, 1-1 и i-2 шаге вычислений ;

А, В, С, D - постоянные коэффициенты, значения которых зависят от шага по независимой переменной и вида реализуемого интегродифференциальногопреобразования.

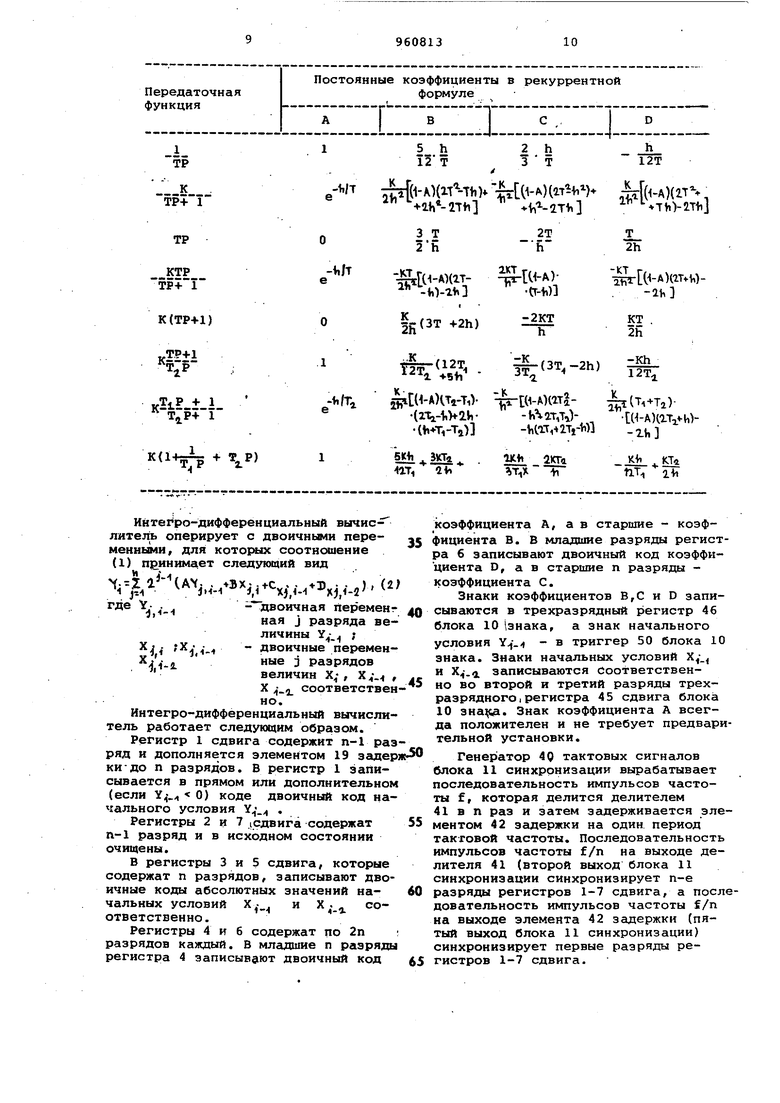

Настройка вычислителя осуществляется заданием постоянных коэффициентов A,B,C,D и начальных условий , . и . Предварительный расчет постоянных коэффициентов A,B,C,D для часто реализуемых видов интегро-дифференциальных преобразователай выполняют по формулам, приведенным в таблице, где К - коэффициент условия; Т , Т, Т -посто.янные времени; h - шаг последовательного преобразования входной величины X в выходную Y, который выбирается из условия заданной точности. Интегро-дифференциальный вычислитель оперирует с двоичными переменньши, для кото1 х соотношение (1) п инимает следующий вид |..,,MJ « - двоичная переменг ная j разряда величины У - двоичные переменные j разрядов величин Х , KV. , X соответствен но. Интегро-дифференциальный вычислитель работает следующим образом. Регистр 1 сдвига содержит п-1 раз ряд и дополняется элементом 19 задер ки-до п разрядов. В регистр 1 записывается в прямом или дополнительном (если 0) коде двоичный код начального условия . Регистры 2 и 7 Сдвига содержат п-1 разряд и в исходном состоянии очищены. В регистры 3 и 5 сдвига, которые содержат п разрядов, записывают двоичные коды абсолютных значений начальиых условий ответственно. Регистры 4 и б содержат по 2п разрядов каждый. В младшие п разряды регистра 4 записывают двоичный код коэффициента А, а в старшие - коэффициента В. В младшие разряды регистра 6 записывают двоичный код коэффициента D, а в старшие п разряды коэффициента С. Знаки коэффициентов В,С и D записываются в трехразрядный регистр 46 блока 10 1знака, а знак начального условия . - в триггер 50 блока 10 знака. Знаки начальных условий Х. и .а записываются соответственно во второй и третий разряды трехразрядного j регистра 45 сдвига блока 10 зиа. Знак коэффициента А всегда положителен и не требует предварительной установки. Генератор 4Q тактовых сигналов блока 11 синхронизации вырабатывает последовательность импульсов частоты f, которая делится делителем 41 в п раз и затем задерживается элементом 42 задержки на один период тактовой частоты. Последовательность импульсов частоты f/n на выходе делителя 41 (второй выход блока 11 синхронизации синхронизирует п-е разряды регистров 1-7 сдвига, а последовательность импульсов частоты f/n на выходе элемента 42 задержки (пятый выход блока 11 синхронизации) синхронизирует первые разряды регистров 1-7 сдвига.

Триггер 43 со счетным входом выполняет деление на две частоты выходной последовательности импульсов элемента 42 задержки. Поэтому на третьем выходе блока 11 синхронизации действует последовательность импульсов частоты f/2n, которая, в свою очередь, делится делителем 44 в п раз. Таким образом, на выходе делителя 44 (четвертый выход блока 11 синхронизации) действует последовательность импульсов частоты f/2n% период следования которой определяет время вычисления на одном шаге.

Вычисления начинаются после установки триггера 16 в единичное состояние импульсом четвертого выхода блока 11 синхронизации. Сигнал прямого выхода триггера 16 открывает элементы и 22, 23 и 28, а сигнал его инверсного выхода закрывает элементы И 20, 21, 24, 25, 29.

Двоичный код начального условия начиная с младшего разряда,, сдвигается иэ регистра 1 через элемент 19 задержки, блок 12 формирования дополнительного кода, элементы И 22 и ИЛИ 33 в регистр 2.

Блок 12 формирования дополнительного кода управляется сигналом второго выхода блока 10 знака (сигналом триггера 50) так, что прямой код регистра 1 про 1ускается без изменения, а дополнительный код регистра 1 преобразуется в прямой код. Таким образом, в регистр 2 записывается двоичный код абсолютной величины начального условия | / знак которого хранится в триггере 50 блока 10 знака.

Единичный сигнал младшего разряда величины ( Y,- ) с выхода элемента ИЛИ 33 поступает на первый вход элемента И 27, на второй вход которого поступает синхронизирую щий импульс первого разряда с пятого выхода блока 11 синхронизации. На выходе элемента И 27 формируется импульс, который устанавливает триггер 17 р единичное состояние.

В fTo время на шине 36 действует сигнал знака входной величины Х. который записывается в регистр 45 сдвига блока 10 знака, а по шине 37 пс ;ледовательно, начиная с младшего разряда, поступает двоичный код абсолютного значения входной величины IXif , который через элементы И 23 и ИЛИ 34 записывается в регистр 3 сдвига.

Двоичный код абсолютного значения начального условия (Х,-. , начиная с младатего разряда, переписывается последовательно с выхода регистра 3 сдвига через элементы И 28 и ИЛИ 35 в регистр 5/ сдвига, из которого сдвигается в регистр 7 сдвига, начиная с младшего разряда, двоичный код абсолютного значения начального условия .j/ . Единичный сигнал младшего разряда величины / / с выхода регистра 5 сдвига по синхронизирующему сигналу пятого выхода блока 11 синхронизации через элемент И 30 поступает на вход триггера 18, устанавливая его в единичное состояние.

Триггеры 17 и 18 в единичном состоянии открывают элементы И 26 и 31 соответственно, через которые с выходов регистров 4 и 6 сдвига

5 соответственно последовательно, начиная с младшего разряда, сдвигаются двоичные, коды коэффициентов А и D соответственно.

Коэффициент А поступает через блок

0 13 формирования дополнительного кода на вход сумматора 9 в прямом или дополнительном коде в зависимости от знака произведения . , сигнал которого действует на втором выходе блока 10 знака. Сигнал знака совпадает с сигналом знака Y,- , так как А70, и фс-рмируется на прямом выходе триггера 50, выходной сигнал которого через элемент И

0 52, открытый сигналом инверсного выхода триггера 43, и элемент ИЛИ 56 поступает на второй выход блока 10 знака

Коэффициент D поступает через

5 блок 14 формирования дополнительного кода на вход сумматора 9 в прямом или дополнительном коде в зависимости от знака произведения .f сигнал которого формируется

0 элементом 49 неравнозначности, на входа которого поступает сигнал знака величины с выхода третьего разряда регистра 45 и Сигнал знака коэффициента D - с выхода третьего

5 разряда регистра 46 блока 10 знака. Сигнал знака , с выхода элемента 49 неравнозначности через элемент И 55, открытьй сигналом инверсного выхода триггера 43, и элемент

0 ИЛИ 57 поступает на третий выход блока 10 знака.

Таким образом, на входы сумматора 9 поступают в прямом или дополнительном коде двоичные коды коэффициентов А и D, алгебраическая сумма которых с выхода одноразрядного последовательного сумматора 9 поступает на вход сумматора 8, на другой вход которого с выхода элемента ИЛИ 32

поступает нулевой код, так как элементы И 20 и 21 закрыты сигналом инверсного выхода триггера 16.

Алгебраическая сумма коэффициентов А и D с выхода одноразрядного сумматора 8 записывается, начиная

5 с младшего, разряда, в регистр 1. Спустя n тактов после установки триггера 16 в единичное состояние, триггеры 16, 17 и 18 сбрасываются в нулевое состояние импульсом второго выхода блока 11 синхронизации. Триг гер 16 в нулевом состоянии сигналом прямого выхода закрывает элементы И 22, 23 и 28, а сигналом инверсного выхода открывает элементы И 21 24, 25 и 29. Элемент И 24 обеспечивает подключение выхода регистра 3 сдвигу к входу регистра 2 сдвига, выход которого элементом И 25 подключается к входу регистра 3 сдвига. Таким образом, регистры 2 и 3 сдвига объединяются в один кольцевой регистр на 2п-1 разряд. Элемент И 29 подключает выход регистра 7 сдвига к входу регистра 5 сдвига, что приводит к объединению регистров 5 и 7 сдвига в кольцевой регистр на 2п-1 разряд. Элемент И 21, открытый сигналом инверсных выходов триггеров 15 и 16 подключает выход регистра 1 сдвига через элемент 19 задержки к входу сумматора 8, что обеспечивает в течение следующих n тактов поступлени с выхода регистра 1 сдвига на вход сумматора 8 прямого или дополнитель ного кода алгебраической суммы коэф фициентов A+D. В это время с выхода регистра 3 сдвига сдвигаются младший разряд входной величины , сигнал которого проходит через элементы И 24 и ИЛИ 33 на первый вход элемента И 27, ас выхода регистра 5 сдвига сдвигается младший разряд величины 4-л I которого поступает на первый вход элемента И 30. В слу чае единичных кодов в младо/ий разряд величин ( и .l элементы И 27 и 30 срабатывают по импульсу пятого выхода блока 11 синхронизаци что приводит к установке триггеров 17и 18 в единичное состояние. Сигналы прямых выходов триггеров 17 и 18открывают соответственно элементы И 26 и 31, через которые с выходов регистров 4 и 6 сдвига сдви.гаются двоичные коды коэффициентов В и С соответственно. Двоичные коды коэффициентов В и С с выходов регис ров 4 и б сдвига преобразуются соот тствующими блоками 13 и 14 формирования дополнительного кода и поступают в прямом или дополнительном ко де на входы сумматора 9. Двоичный код коэффициента В преобразуется блоком 13 формирования дополнительного кода в прямой или д полнительный код в зависимости от знака произведения ВК , сигнал ко торого формируется элементами 47 неравнозначности блока 10 знака. Н входы элемента 47 неравнозначности поступают сигналы знаков величины Х| и В с выходов первых разрядов регистров 45 и 46 соответственно. Выходной сигнал элемента 47 неравнозначности через элемент И 53, откры.тый в это время прямым сигналом триггера 43; и элемент ИЛИ 56 поступает на второй выход блока 10 знака. Аналогичным образом формируется элементе 48 неравнозначности сигнал знака произведения , который через элементы И 54 и ИЛИ 57 поступает на третий выход блока 10 знака, управляя блоком 14 формирования дополнительного кода. Прямой или дополнительный код алгебраической суммы коэффициентов В и С с выхода сумматора 9 поступает на второй вход сумматора В, на первый вход которого с выхода регистра 1 через элемент 19 задержки, элементы И 21 и ИЛИ 32 сдвигается прямой или дополнительный код алгебраической суммы коэффициентов А и D, с выхода сумматора 8 двоичный код алгебраической суммы коэффициентов А,В,С и D записывается в регистр :1. Таким образом, в регистре 1 накапливается за 2п тактов алгебраическая сумма коэффициентов А,В,С и D, после чего триггер 15 устанавливается в единичное состояние импульсом третьего выхода блока 11 синхронизации. Триггер 15 в единичном состоянии открывает сигналом прямого выхода элемент И 20 и закрывает сигнале инверсного выхода элемент И 21. Элемент И 20 подключает выход регистра 1 к входу сумматора 8 в момент сдвига с выхода регистра 1 второго разряда алгебраической суммы коэффициентов А,В,С и D. в это время с Еыхода регистра 3 сдвига сдвигается второй разряд величины I г сигнал которого через элементы И 24, ИЛИ 33, И 27 поступает на вход установки в едиггичное состояние триггера 17, ас выхода регистра 5 сдвига сдвигается второй разряд величины | Х,-,/ , сигнал которого черезэлемент И 30 поступает на вход установки в единичное состояние триггера 18. Триггеры 17 и 18 устанавливаются в единичное состояние, открывая элементы И 26 и 31, через которые с выходов регистров 4 и б сдвига сдвигаются двоичные коды коэффициентов А и D соответствекно. Двоичные коды произведения коэффициентов А к D на двоичные переменные вторых разрядов величин IY,.| и IX.i/ соответственно преобразуются в прямой или дополнительный код блоками 13 и 14 формирования дополнительного кода соответСТвенно, затем суммируются сумматором 9, с которого алгебраическая сумма коэффициентов А и D поступает на второй вход сумматора 8, начиная с младшего разряда, а на первый вход сумматора 8 с выхода ре гистра 1 сдвига сдвигается сумма коэффициентов А,В,С и D, начиная со второго разряда. Таким образом, установка триггера 15 в единичное состояние приводит к сдвигу на один разряд накоп ленной суммы коэффициентов в регист ре 1 сдвига, обеспечивая этим выпол нение операции умножения на два. После окончания суммирования сум матором 8 всех разрядов, сдвигаемых с выхода регистра 1 сдвига, с сумт сой коэффициентов А и D триггер 15 сбрасывается в нулевое состояние импульсом второго выхода блока 11 Синхронизации. Установка триггера 1 в нулевое состояние обеспечивает подключение выхода регистра 1 сдвига через элемент 19 задержки к перв му входу сумматора 8, на второй вх которого с выхода сумматора 9 поступает двоичный кол алгебраической сумма произведения коэффициентов В ,и С на двоичные переменные вторых разрядов величин ( и .,,/ соответственно. Действительно, спустя п тактов после установки триггера- 15 в единичное состояние с выхода регистра 3 сдвига сдвигается второй разряд величины / X - /, сигнал которого чере элементы И 24, ИЛИ 33, И 27 устанав ливает, в случае единичного кода, триггер 17 в единичное состояние, а с выхода регистра 5 сдвига сдвигает ся второй разряд , сигнал которого через элемент И 30 устанав ливает триггер 18 в единичное состо яние, если во втором разряде сдвига ся единичный код. С выходов регистров 4 и б сдвига сдвигаются через элементы И 26 и 31 соответственно двоичные коды коэффициентов В и С, которые преобразуются кодами 13 и 14 формирования дополнительного кода поступают на входы сумматора 9 Сумматор 8 суммирует накопленную и рдвинутую на один разряд в регист ре 1 сдвигу сумму коэффициентов с алгебраической суммой произведения коэффициентов В и С на двоичные переменные вторых разрядов величин Xil и соответственно и результат сдвигается в регистр 1 сдви га. Дальнейшие вычисления в интегррдифференциальном вычислителе выполняются .аналогичным образом. Каждые 2п такта в кольцевых регистрах на 2п-1 разряд, образованных объединением регистров 2 с 3 и 5 с 7-. сдвига происходит сдвиг выходных сигналов относительно выходных импульсов блока 11 синхронизации, что приводит к совпадению (на элементах И 27, 30) с импульсом пятого выхода блока .синхронизации следующих разрядов величин 1-1 „---г л 1-( переключение триггером 15 цепи циркуляции регистра 1 сдвига на п-1 разряд с выхода элемента 19 задержки непосредственно на выход регистра 1 сдвига обеспечивает сдвиг информации в регистре 1 сдвига на один разряд. Спустя тактов после начала вычислений в регистре 1 сдвига накапливаются в прямом или дополнительном коде п старших разрядов выходной величины У; , знаковый разряд которой с выхода сумматора 8 поступает на второй вход (шина 58) блока 10 знака и через элемент И 51 записывается в триггер 50. К этому моменту времени в регистре 3 сдвига содержится код величины , в регистре сдвига 5 :- 1х,-./ , а в регистре 7 сдвига - X .j-./j. I . Первый шаг вычислений в интегро-дифференциальном вычислителе заканчивается. ВЁ1Числения на втором шаге и всех последукяцих шагах осуществляется аналогичным образом, но с новыхначальных условий, которые формируются на предьздущем tuare вычислений. Таким образом, интегро-дифференциальный вычислитель реализует согласно соотношению (2) любую передаточную функцию, заданную в табл|1це. Перестройка интегро-дифференциального вычислителя на заданный вид передаточной функции вьтолняется заданием коэффициентов А,В,С и D в регистрах 4 и б сдвига. Интегро-дифференцйальный вучислитель можно использовать для ЛИН ей ных ин тегро-дифферен циаль ных преобразований любого порядка и по любой зависимой входной переменной. Чтобы осуществить интегро-дифференциальное преобразование высокого порядка необходимо представить это преобразование в виде произведения элементарных передаточных функций, рассчитать их параметры и начальные условия и соединить последовательно ряд одинаковых интегродифференциальных вычислителей в общем случае с различными условиями и коэффициентами Af.B,C и D, В этом случае выходные шины, 38 и 39 каждого предыдущего интегро-дифференциального вычислителя подключаются соответственно к входным шинам 36 и 37 последующего интегро-дифференциального вычислителя. Причем синхронизация работы всего ряда и нескольких одинаковых йнтегро-дифференциальных вычислителей, реализующих каждый свою передаточную функцию, осуществляется от одного и того же блока 11 синхронизации и в этом слу ,чае не требуется дополнительных аппаратурных затрат оборудования. На базе унифицированных интегродифференциальных. вычислителей можно реализовать любые виды интегродифференциальных преобразований, необходимые для задач автоматическо го управления и моделирования сложн динамических объектов в реальном времени. Технико-экономические преимущест ва предложенного интегро-дифференциального вычислителя по сравнению с известным заключаются в повышении быстродействия устройства и точности вычислений. Время вычислений на одном шаге для предложенного интегро-дифференциального вычислителя а для известного /f Таким образом, быстродействие предложенного устройства в 1,5 раза бол ше, чем быстродействие известного устройства. Повышение точности вычислений достигается за счет дополнительного члена DX,,- в рекуррентном соотношении (1), который не учи тывается в известном устройстве. Повышение точности в предложенно интегро-дифференциальном вычислителе позволяет брать более крупный шаг вычислений, и этим еще более ув личить быстродействие. Формула изобретения Интегро-дифференциальный вычисли тель , содержащий первый, второй, тр тий и четвертый регистры сдвига, первый сумматор, блок знака, блок синхронизации, первый и второй блоки формирования дополнительного кода, первый, второй и третий триггеры, элемент задержки, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй и третий элементы ИЛИ, причем вход первого регистра сдвига соединен с выходом первого сумматора, первый вход которого сое динен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй - с выходом второго элемен та И, первый вход первого элемента И соединен с выходом первого регистра сдвига и входом элемента задержки, второй вход первого элемент И соединен с прямым выходом первого триггера, первый вход второго элемента И соединен с выходом элемента задержки, а второй - с инверсным выходом первого тр иггера, третий вход первого элемента И соединен с третьим входом второго элемента И, первый вход первого блока формирования дополнительного кода соединен с первым входом второго блока формирования дополнительного кода, а второй - с выходом элемента задержки, первый вход третьего элемента И соединен с первым входом четвертого элемента И и прямым выходом второго триггера, первый вход которого соединен с первыми входами первого и третьего триггеров, второй вход третьего элемента И соединен с выходом первого блока формирования дополнительного кода, первый вход блока знака является первым входом устройства, второй вход четвертого элемента И является .вторым входом устройства, первый выход блока знака является первым выходом устройства, вьпсод первого блока формирования дополнительного кода является вторым выходом устройства, первый вход пятого элемента И соединен с третьим входом первого элемента И, с первым входом шестого элемента И и с инверсным выходом второго триггера, выход третьего элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход второго элемента ИЛИ соединен с входом второго регистра сдвига, выход которого соединен с вторым входом шестого элемента И, выход четвертого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход третьего элемента ИЛИ соединен с зходом третьего регистра сдвига, выход которого соединен с вторым входом пятого элемента И, выход четвертого регистра сдвига соединен с первым входом седьмого элемента И, второй вход которого соединен с прямым выходом третьего триггера, второй вход которого соединен с выходом восьмого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ, выход седьмого элемента И соединен с вторым входом второго блока формирования дополнительного кода, второй вход блока знака соединен с выходом сумматора, а третий - с первым выходом блока синхронизации, второй выход блока знака соединен с первым входом первого блока формирования дополнительного кода, второй третий, четвертый и пятый выходы блока сихронизации соединены соответственно с первым и,втоptw входами первого триггера, вторыми входами второго триггера и восьмого элемента И, отличающийс я тем, что,с целью повышения быстродействия и точности вычислений, в него введены пятый, шестой и седьмой регистры сдвига, второй сумматор, третий блок формирования дополнительного кода, четвертый триггер, девятый, десятый, одинадцатый и двенадцатый элементы И и четвертый элемент ИЛИ, причем вход пятого регистра сдвига соединен с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены соответственно с вьйсодами девятого и десятого элементов И, первый и второй входы девятого элемента И соединены соответственно с выходом третьего регистра сдвига и прямым выходом второго триггера, выход пятого регистра сдвига соединен с первым входом одиннадцатого элемента И, второй вход которого со единен с пятым выходом блока синхронизации, а выход с первым вводом четвертого триггера, второй вход которого соединен с вторым выходом блока синхронизации, а прямой выход - с первым входом двенадцатого элемента И, второй вход которого соединен с выходом шестого.регистра сдвига, а выход - с первым входом блока формирования дополнительного кода, второй вход которого соединен с третьим выходом блока знака, а выход - с первым входом второго сумматора, второй вход которого соединен с выходом второго блока формирования дополнительного кода, а выход - с вторшл входом первого сумматора, вход седьмого регистра сдвига соединен с выходом пятого регистра сдвига, первый и второй входы десятого элемента И соединены соответственно с инверсным выходом второго триггера и выходом седьмого регистра сдвига.

Источники информации, принятые во внимание при экспертизе

Машиностроение, 1968, с.84 и 196, рис. 15 и 20.

5 кл. G 06 J 1/02, 22.01.79 (прототип).

Авторы

Даты

1982-09-23—Публикация

1980-03-18—Подача