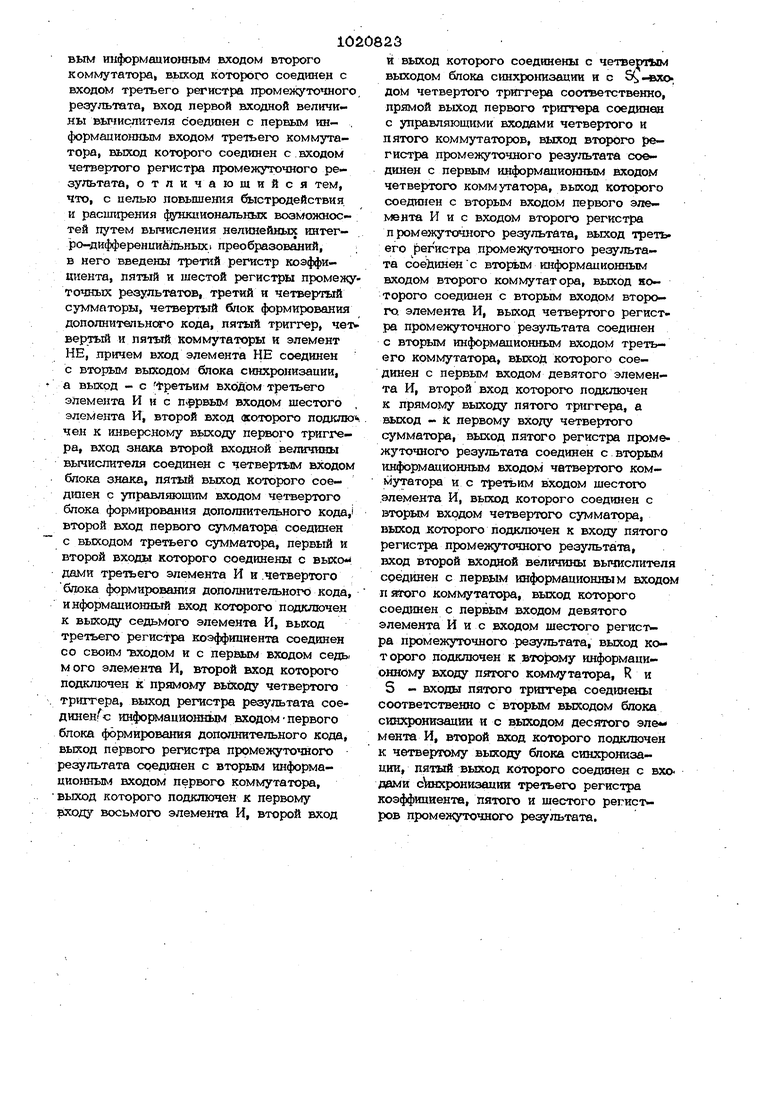

вым информационным входом второго коммутатора, выход которого соединен с входом третьего регистра промежуточного, результата, вход первой входной величины вычислителя соединен с первым ин- , формацио101ым входом третъегчз коммутатора, выход которого соединен с входом четвертого регистра промежуточного результата, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем вычисления нелинейных интегро-дифференцийльных преобразований, в него введены третий регистр коэффициента, пятый и шестой регистры промежуточных результатов, третий и четвертый сумматоры, четвертый блок формирования дополнитепьнсго кода, пятый триггер, че-рвертый и пятый коммутаторы и элемент НЕ, причем вход элемента НЕ соединен с вторым выходом блока синхронизации, а выход - с третьим входом третьего элемента И и с п ррвым входом шестого , элемента И, второй вход (Которого лодклю ч . чен к инверсному выходу первого триггера, вход знака второй входной величины вычислителя соединен с четвер-пьы входом блока знака, пятый выход которого соединен с упрбшляющим входом четвертого блока формирования дополнительного кода, второй вход первого сумматора соединен с выходом третьего сумматора, первый и второй входы которого соединены с выхо дами третьего элемента И и .четвертого блока формирования дополнительного кода, информационный вход которого подключен к выходу седьмого элемента И, выход третьего регистра коэффициента соединен со своим ВХОДОМ и с первым входом седьмого элемента И, второй вход которого подключен к прямому вьгходу четвертого триггера, выход регистра результата соеинен с информационным входом первого блока формирования дополнительного кода, выход первого регистра промежуточного езультата соединен с вторым информаио1шьт4 входом первого коммутатора, ыход которого подключен к первому ВХОД5 восьмого элемента И, второй вход

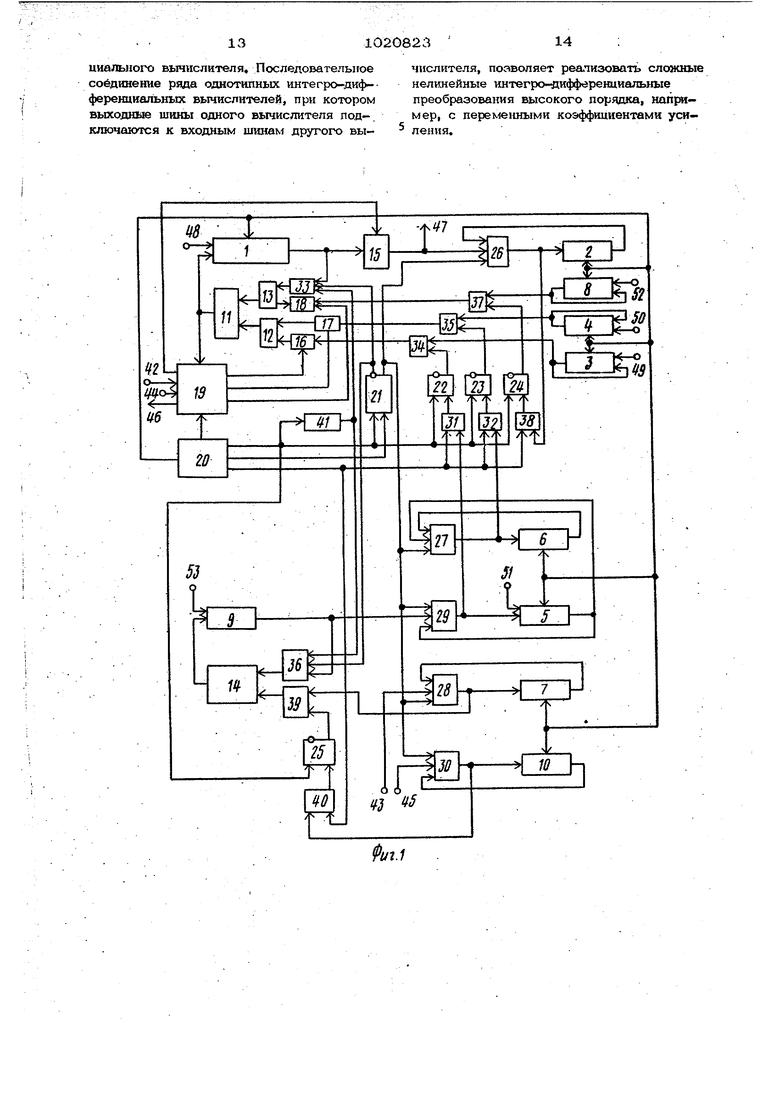

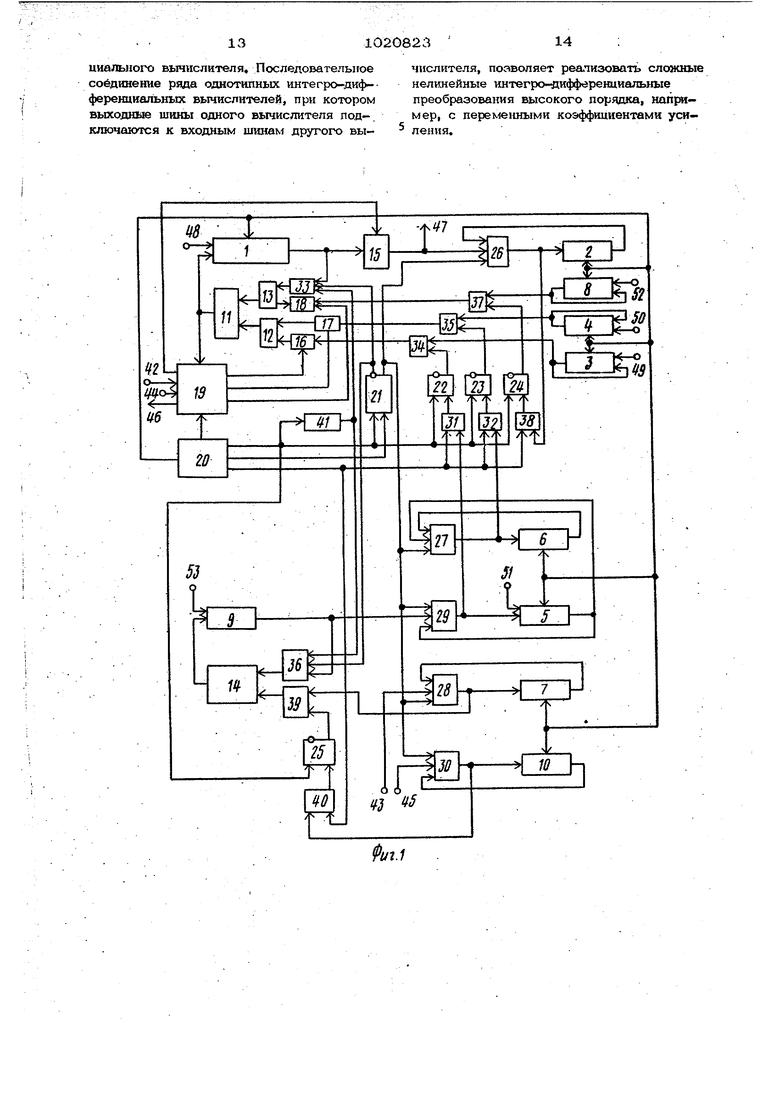

и выход которого соединены с четвертчдм выходом блока С1шхронкзации и с S J-BXO дом четвертого триггера соответственно, прямой выход первого триггера соединен с управляющими входами четвертого и пятого коммутаторов, выход второго регистра промежуточного результата соединен с первым информационным входом четвертого коммутатора, выход которого соединен с вторым входом первого элемента И и с входом второго регистра промежуточного результата, выход третьего регистра промежуточного результата соединен с вторьгм информационным входом второго коммутатора, выход которого соединен с BTOpbnvj входом второго элемента И, выход четвертого регистра промежуточного результата соединен с вторым информационным входом третьего коммутатора, выход которого соединен с первым входом девятого элемента И, второй вход которого подключен к прямому вьпсоду пятого триггера, а выход - к первому входу четвертого сумматора, выход пятого регистра промежуточного результата соединен с вторым информационным входом четвертого коммутатора и с третьим в1ходом шестого элемента И, выход которого соединен с вторым входом четвертого сумматора, выход которого подключен к входу пятого регистра промежуточного результата, вход второй входной величины вычислител соединен с первым информационным входо пжгого коммутатора, выход которого соединен с первым входом девятого элемента И и с входом шестого регист. ра промежуточного результата, выход которого подключен к информационному входу пятсго коммутатора, R и S - входы пятого триггера соединены соответственно с вторым выходом блока синхронизации и с выходом десятого эле- мента И, второй вход которого подключен к четвертому выходу блока синхронизации, пятый выход которого соединен с вхдами с шхронизации третьего регистра коэффициента, пятого и шестого регистров промежуточного результата. Изобретение относится к аптоматщсе и вычислительной техн1же и может быть использовано для моделирования и управления динамическими объектами в различ ных отраслях промышленности. Известны аналоговые ннтегро-диффере циальные устройства , содержащие аналоговые интеграторы, сумматоры и масштабные блоки для задания коэффициентов передачи 1 . Недостатком аналоговых интегро-дифференциальных .устройств является низкая точность вычислений выходных сигналов в случае достаточно больших значений постояашых времени, характерных для многих технологических процессов. Известны цифровые интегро-дифференциальнью устройства тша цифровых дифференциальных анализаторов, которые содержат ряд т1фров1 Х интеграторов, коммут1(руе1йых между собой согласно завшш му Ю1тегр -дифференциапьному преобраэо1закш , Од1ЩК Ш1тегро-чифферейциальные уст ройства характери ются низким быстродействием и слбЖ11Ос1Рью реализации. Наиболее близким по технической сущ ности к предлагаемому является интегро дйфференциалыалй вьршслитель, содержащий семь регистров, два сумматора, три блока формирования дополнительного кода, бп(ж знака, блок синхронизации, четыре трт-гера, двенадцать элементов И четыре элемента ИЛИ и элемент задержки, с соответствующими связям иГЗ, Однако вычислитель обладает низким быстродействием и ограниченными функии М1альными возможностями. Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем вычислениянелинейн интегро-дифференциальнык преобразований Поставленная цель достигается тем, что в интегро-дифференииальный вычис литель, содержащий регистр результата, два. регистра коэффициента и четыре регистра промежугочнык результатов, два сумматсфа, три блока формирования до- . лолнительного кода, блок знака, блок синхронизации, четыре триггера, три коммутатора и десять элементов И, причем вход знака первой входной величины вычислителя соединен с первым входом блока знака, первый выход которого соединен с выходом знака результата вычислителя, выход первого сумматора соединен с входом регистра результата и вторым входом блоке знака, второй, третий и четвертый выходы которого соед1шены с управляющими входами первого, второго и третьего блоков форми- рованкя дополнительного, кода соответстве1шо, первый выход блока синхронизации соед1шен с третьим входом блока знака, второй выход - с R -входами первого, второго, третьего и четвертого триггеров, третий вьрсод - с S -входом первого триггера, четвертЬ1й щ,1ход - с первыми входами первого и второго элементов И и пятый выход - с ксодами синхронизации регистра результата, первого и второго регистров коэффициента и первого, второго, третьего и четвертого регистров промежуточных результатов, выход регистра результата соединен с первым входом третьего элемента И, второй вход которого.соединен с инверсным выходом первого триггера, прямой выход которого подключен к управляю1Ш1м входам первого, второго и третьего коммутаторов, выход первого блока формирования дополнительного кода соединен с выходом абсолютного значения результата вычислителя и с первым информацкошшм входом первого коммутатора, выход которого подключен к входу первого регистра промежуточного, результата, выхо|ды первого и второго регистров коэффициентов соединены со своими входами и с первыми входами четвертого и пятого элемен- тов И соответственно, прж.ые выходы второго и третьего триггеров соединены с вторыми входами четвертого и пятого элементов И соответстеедшо, S -входы второго и третьего триггеров соединены с выходами первого и второгч) элементов соответствешю, первый вход первого сумматора подключен к выходу второго сумматора, первый и второй входы котор ого с выходами -второго и третьего блоков формирования допо1шительного кода, информациошаю входы которых подключены к выходам четвертого и пятого элементов И соответственно, .. выход второго регистра промежуточного результата соединен с первым информационным входом второго коммутатора, выход которого соединен с входом третьего регистра промежуточного результата, вход первой входной величины вьтчислнтеля соед1шен с первым информационным входом третьего коммутатора, выход которого соединен с входом четвертого регистра промежуточнсзго результата, введены трепли регистр коэффициента, пятый и шестой регистры промежуточных результатов, третий и четвертый суммато ры, четвертый блок формирования допол4ЛОlO2 нителыюго кода, пятый триггер, четвертый и пятый коммутаторы и элемент НЕ, причем вход элемента НЕ соединен с вторым выходом блока синхронизации, а выход - с третьим входом третьего элемента И и с первым входом шестого элемента И, второй вход которого подключен к инверсному вькоду первого триггера, , вход знака второй входной велишшы вь1 ислителя соединен с четвертым входом . блока знака, пятый выход которого соединен с управляющим входом четвертого ; блока формирования дополнительного кода, второй вход первого сумматора coe-i динен с выходом третьего сумматора, первьхй и второй входы которого соедйнеЦ ны с выходами третьего элемента И и четвертого блока формирования дополнительного кода, информационный вход которого подключен к выходу седьмого элемента И, выход третьего регистра коэффициента соединен со своим входом и с первым входом седьмого элемента И, второй вход которого подключен к прямому выходу четвертого триггера, выход регистра результата соединен с информационным входом первого блока формирования дополнительного кода, ВЬЕКОД первого регистра промежуточного результата соединен с вторым информационным входом первого коммутатора, выход которого подключен к первому входу восьмого элемента И, второй вход и выход которого соединены с четвертым выходом блока сйнх ронизадии и с S -щодом четвертого тршгт щ соответственно, прямой выход первого триггера соединен с управляющим входами четвертого и пятого комцутаторов, выхо}} второго регистра промежуточного результата соединен с первым инфор мацирюшм входом четвертого коммугатор а, выход которого срйдинен с вторым входом первого элемента И и с-входом второго регистра промежуточного результа та, выход третьего регистра промеиоггочНого результата соединен с вторым информационным входом второго коммутатора, выход которого соединен с вторым входом второго элемента И, выход четвер того регистра промежуточного результата соединен с вторым информационным вгсодом третьего коммутатора, выход которого соединен с первым входом девятого элемента И, второй вход которого подключен к прямому выходу пятого триггера, а выход-к пербому входу четвертого сумматора; выход пятого регистра промея уточного результата соединен с вторым информацио ным входом четвертого коммутатора не ) о/г-.-. -ог-:-, : .оия-о v- OToqcobiJ i3,., ,-, v,.,v,-.i..Третьим входом шестЬго элемента И, В1 ход которого соединен с вторым входом четвертого сумматора, выход которого подключен к входу пятого регистра промежуточного резул тгата,вход второй входной величины вычислителя соединен с первым информационным входом пятого коммутат тора, выход которого соединен с первым входом десятсто элемента И и с входом шестого регистра промежуточного результата, выход которого подключен к второму информационному входу пятого коммутатора, R и 5 - входы пятого триггера соединены соответственно с вторым выходом блока синхронизации и с выходом десятого элемента И, второй вход которого подключен к четвертому выходу блока синхронизации, пятый выход которого соединен с входами синхронизации третьего регистра коэффициента, пятого и шестого регистров промежуточного результата. На фиг. 1 изображена структурная схема интегро-дн ффе ренциальногр вычислителя; на фиг. 2 - структурные схемы блока знака и блока синхронизации. Интегро- дифференциальный вычислитель (фиг. 1) содержит регистр 1 результата, первый регистр 2 промен точного результата, первый и второй регистры 3 и- 4 |соэффициентов соответственно, второй. Третий и четвертый регистры 5-7 промежуточных результатов соответственно, третий регистр 8 коэффициента, пятый и шестой регистры 9 и 10 промежуточных результатов, периый - четвертый сумматоры 11-14 соответственно, первый - четвертый блоки 15--18 формирования дополнительного кода соответственно, блок 19 знака, блок 20 синхронизации, первый - пятый RS -триггеры 21-25 соответственно, первый - пятый коммутаторы 26-30 соответственно, -г десятый элементы И 31-4О соответственно, элемент НЕ 41, входы 42 ввода знака первой входной величины, вход 43 из ввода первой входной величины, вход 44 ввода знака второй входной величины, вход 45 ввода второй входной величины, выход 46 знака результата, выход 47 абсолютного значения результата/ ; входы 48-53 начальной установки, Блок 19 знака (фиг. 2) содержит два регистра 54 и 55, RS -триггер 56, четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 57-60, элемент И 61, две шины 62 и 63 ввода данных, три входные шины 42, 44 и 64, четъ1ре выходные шины 46, 65, 66 и 67. 5 8.loa Блок 2Q синхронизации (фиг. 2) содержит генератор 68 тактовых сигналов, делитель 69 частоты, элемент 70 аадерж ки, делитель 71 частоты и выходные ,шшш 72-75, которые smляютcя соответствешю , третьим, четвертым и пятым выходами. &1ока 2б синхронизации. Интегро-дифференииальный вычислитель в каждом цикле вышюлений реализует pei ppeHTHoe соотношение .,CY.2 где X -j и Х - значения первой и вто. рой вxoJШЫx величин сооттетственно в каждом f -ом цикле вычислений;TlMT,, - значения выходной ве . личины на 1 -ом и 1 циклах вычислений соответствен( Y- ViY - значения произведения входных величин на . , 1 -1 и i -2 цикла вьпислешЬй: соответстве но; А ,В постояиные коэффициенты. Интегро дифференииап ный вычислитель выполняет интегро-;Ш1фферекииалы1ое пре образование первого nopsuuca над велитаной Y(i) , которая 5тляетоя лроиздедени ем двух входных величин Х (i) и Xvj(t) Настройка на вид интегро-дафференциального преобразования осуществляется заданием постоянных коэффициентов. А, В,С и начальных Z ; , Yf и Y;j, Предварительный расчет постояншдх коэффициентов А, В, С для часто реали- зуемых видов интегро-дифференцнальных преобразований выполняют по формулам приведенным в таблице, где К - коэффи циент усиления. Т, Т, Т - постоянные времени, Ь - шаг последовательного преобразования величины Y в выходную Z I I который выбирается из условий заданной точности. Интегро-дифференциальный вычислитель оперирует с двоичными переменными, для которых соотношение (1) принимает следующий вид Г, (,VM BYiHH cYi.i.2) )(,X,., (2)

1020823

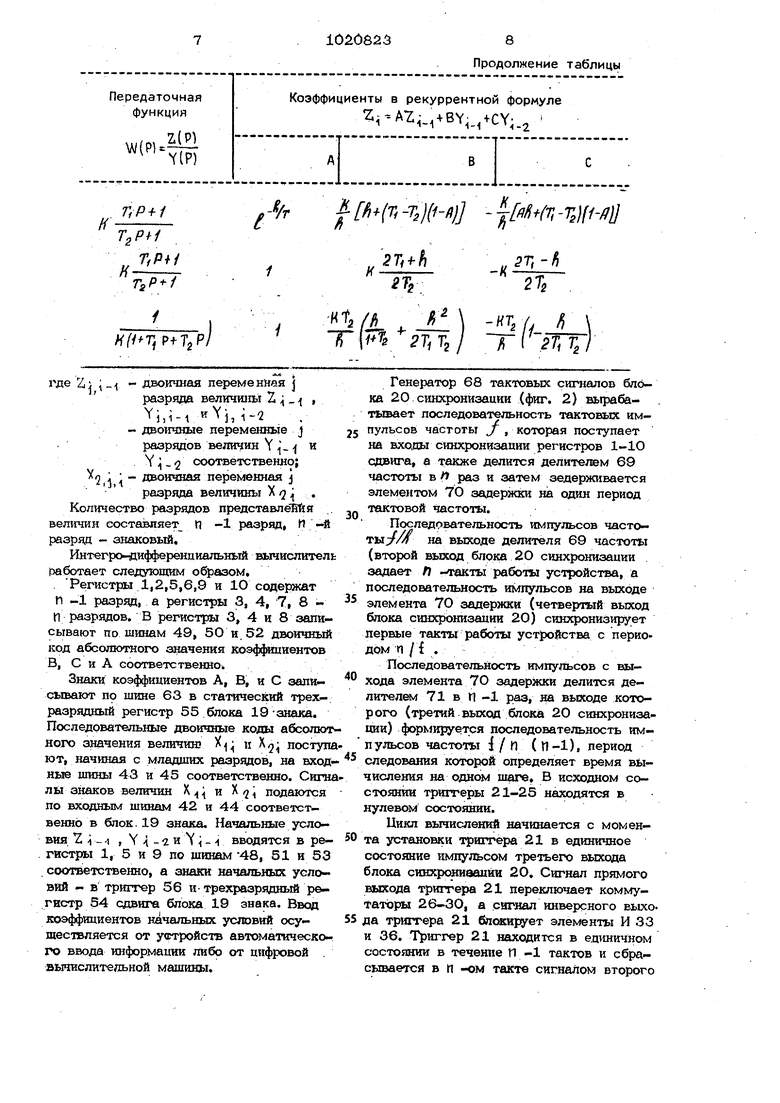

Коэффициенты в рекуррентной формуле

Передаточная функция

8 Продолжение таблицы rA7;.,4BY,.CY;.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

1. ИНТЕГРО-ДИФФЕРЕН-ЦИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ, содержащий регистр результата, два регистра коэффициента и четыре регистра промежуточных результатов, два сумматора, три блока .формирования дополнительного кода, блок знака, блок синхронизации, четыре триггера, три коммутатора и десять элементов И, пртетем вход знака первой вхбдной величины вычислителя соединен с первым входом блока знака, первый выход которого соед1шен с выходом знака результата вычислителя, выход первого сумматора соединен с входом регистра результата и вторым входом бпока знака, второй третий и четвертый выходы которого, соединены с управ: ляющими входами первого, второго и третьего блоков формирования дополнительного кода соответственно, первый выход блока С1шхронизаци11 соед1шен с третьим входом блока знака, второй выX од - с R -входами первого, второго. третьего и четвертого триггеров, третий выход - с S -входом первого триггера, четвертый выход - с первыми входами первого и второго элементов И и пятьй .выход - с входами синхронизации регистра результата, первого и второго регистра коэффициента и первого, второго, третьего и четвертого регистров промежуточных результатов, вьрсод регистра результата соедине н с первым входом третьего элемента И, второй вход которого соед1шен с таверсным выхоаом первого триггера, прямой выход которого подключен к управляющим входам первого, второгх и тречъего коммутаторов, выход первого блока формиi рования дополнительного кода соединен (Л с выходом абсолютного значения результата вычислителя и с первык информаCZ ционным входом первого коммутатора, выход которого подключен к входу первого, регистра прамежуточного результата, выходы первого и второго регистров фициентов соединены со свошчЛс входами. (д и с первыми входами четвертого н пятого элементов И соответственно, прямые о ходы второго и третьего триггеров соеди00 нены с вторыми входами четвертого и пяю того элементов И соответственно, 6 - со входы второго и третьего триггеров соединены с выходами первого и второго элементовИ соответственно, первый вход первого .сумматора подключен к выходу второго сумматора, перщлй и вто- . рой входы которого соединены с выходами второго и третьего блоков формирования дополнительного кода, 1шфорь1ациош1ые входы которых подключены к. выходам четвертого и пятого элементов И соответственно, выход второго регистра промежуточного результата соединен с пер

-fr ПР+f где Z/ - - двоичная переменная j разряда величшпь 2 i i,- двоичные переменньте J разрядов величин Y ;{--j и Y 2 соответственно; Vfj - двоичная переменная j разряда величины X /2 . Количество разрядов представлен я величин составляет П -1 разряд И -и разряд - знаковый. Интегро-дифференциальный вычислител работает следующим образом, Регистры 1,2,5,6,9 и 1О содержат И -1 разрад, а регистры 3, 4, 7, 8 П разрадов. В регистры 3, 4 и 8 записывают по шинам 49, 50 и. 52 двоичный код абсолютного значения коэффициентов В, С и А соответственно. Знаки коэффициентов А, В, и С записывают пр шине 63 в статический трехразрядный регистр 55 блока 19-знака. Последовательные двоичные коды абсолют ного значения величин Х и Х поступ ют, начиная с младших разрадов, на вход ные шины 43 и 45 соответственно. Сигн лы знаков величин и Х/2 подаются по входным шинам 42 и 44 соответственно в блок. 19 знака. Начальные условия Т -л , У4-ги | вводятся в регистры 1, 5 и 9 по шинам 48, 51 и 53 соответственно, а знаки начальных условий - в триггер 56 и-трехразрядный регистр 54 сдвига блока 19 знака. Ввод коэффициентов начальных условий осуществляется от у«стройств автоматического ввода информации либр от цифровой . вычислительной машины. Л ,(г, -r,)(i-fii - fiHT,-T,}li-/il Генератор 68 тактовых сигналов блока 20 синхронизации (фиг. 2} вырабатывает последовательность тактовых импульсов частоты J , которая поступает на входах синхронизации регистров 1-1О сдвига, а также делится делителем 69 частоты в раз и затем зедерживается элементом 70 задержки на один период тактовой частоты. Последовательность импульсов частоты У/Г на выходе делителя 69 частоты (второй выход блока 2О синхронизации задает /7 -/такты работы устройства, а последовательность импульсов на выходе элемента 7О задержки (четвертый выход блока синхронизации 20) синхронизирует первые такты работы устройства с периодом П /{ . Последовательность импульсов с иыхода элемента 70 задержки делится делителем 71 в И -1 раз, на выходе которого (третий выход блока 20 синхронизации) формируется последовательность импульсов частоты i / П ( n-l), период следования которой определяет время вычисления на одном шаге. В исходном состоянии триггеры 21-25 находятся в нулевом состоянии. Цикл вычислений начинается с момента установки триггера 21 в единичное состояние импульсом третьего выхода блока синхрониаацйи 20. Сигнал прямого выхода триггера 21 переключает коммутаторы 26-30, а сигнал инверсного выхо. да триггера 21 блокирует элементы И 33 и 36. Триггер 21 находится в единичном состоянии в течение И -1 тактов и сбрасывается в п -ом такте сигналом второго выхода блока 2 О сшгсроннзаиин. После- , довательный двоичный код начального условия 2,4 сдвигается, начиная с младшего разряда, с выхода регистра 1 через блок 15 формирования дополнитель ного кода и коммутатор 26 в регистр 2 и на первый вход элемента И 38, который срабатывает в случае единичного кода младшего разрада по сигналу четвертого выхода блока 20 синхронизации. Блок 15 формирования дополнительного кода управляется сигналом второго BI IXOда блока 19 знака так, что пр5Ву1ой код пропускается без изменения, дополнитель ный код регистра 1 преобразуется в прямой код. Таким образом, в регистр 2 . залисывается двоичный код абсолютной величины начального условия Z . В этр время последовательный, двоичный код начального условия J -2 сдвигается, начиная с младшего разрядд, с выхода регистра 5 через коммутатор 27 в регистр 6 и на второй вход элемента И 32 KOTOpbrii срабатывает в случае единичного Кода младшего разряда по сигналу четвертого выхода блока 20 cvшxpoниaa- ции. Одновреме нно с этим последовательный двоичный код начального услови -j сдвигается, начиная с младшего разряда, с выхода регистра 9 через ком мутатор 29 в регистр 5 и на второй вход элемента И 31, который срабатыва ет в случае единичного кода младшего разрада по сигналу четвертого выхода блока 20 синхронизации. В первые П -1 тактов осуществляется ввод, начиная с мла,цших разрадов, после довательных двоичных кодов входных величин , и Х2 которые, поступая по входным шинам 43 и 45 соответственно, сдвигаются через коммутаторы 28 и ЗО в регистры 7 и 10 соответстBeisfflo. В случае единичного кода младшего разряда величдаы по сигналу четвертого выхода блока 2О сиихронизации срабатъшает элемент И 40, выход ной сигнал которого устанавливает тригг 25 в единичное состояние. Срабатывание элементов И 31, 32 и 38 приводит к ycTaaoBke в единичное состояние триггеров 22-24 соответственно. Сигналы пря мых выходов триггеров 22-25 открьюают элементы И 34, 35, 37 и 39 соответственно. Спустя П -1 такт триггеры 22-25 сбрасываются в нулевое состояние сигналом второго нькода блока 20 сшссронизаиии. Последовательные двоичные коды коэфф1щиентов В, С и А сдвигаются, начиная с младщйх разрадов, с выходов регистров 3, 4 и 8 соответственно через элементы И 34, 35 и 37 соответственно через блоки формирования дополнительного кода 16-18 COOTW ветстаенно на первый, второй входы сумматора 12 и второй вход сумматора 13 соответственно. Блоки ф6рм1фования 16-18 дополнительного кода управляются сигналами знаков произведений ВЧ. CY 2 А2( ,, которые действуют на третьем, четвертом и пятом выходах блока 19 знака. В зависимости от положительных или отрицательных знаков блоки формирования дополнительного.кода формируют прямой или .дополнительный код. Сигналы знаков формируются блоком 19 знака следующим образом. По шинам 42 и 44 поступают двоичные сигналы знаков входаых величта X, и , которые элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 57 блока 19 знака (фиг. 2) преобразуются в сигнал знака произведешш Y-i iсдвиг1а мый по выходному сигналу делителя 71 частоты блока 20 синхронизации в первый разрад регистра 54 сдвига, во вто рой и третий разряды которого сдвигарт ся из первого и второго разрадов COOTVветственно знаки начальных условий Y i - ( V - -2 соответственно. Знак проиэведения А Z - формтфуется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 58 по сигналам . прямого выхода триггера 56, в котором хранится знак величины Z -,( , и выхода первого разряда регистра 55,, в котором хранится знак коэффициента А. Знак произведения В - формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 59 по сигналам выхода разрада регистра 54, в котором хранится знак величины и выхода второго разрада регистра 55, в котором хранится знак коэффициента В. Знак произведения С формируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 6О «о сиг налам выхода третьего разр5и1Д регистра 54, в котором содержится знак величины , и выхода третьего разрйда регистра 55, в котором хранится знак коэффициента С. Последовательные двоичные суммато ры 11-13 формируют последовательный код алгебраической суммы произведений коэффициентов А, В и С на двоичные переменные младших разрадов величин Z-i-1 ,Y.i- и Y 2 соответственно. Двоичный код суммы с выхода сумматора 11 сдвигается, начиная с младшего разрада, в регистр 1. Оановремешю с этим с выхода сумматора 14 с.овнгается, начиная с младижго рооряда, в регистр 9 последовательгалй двотгчный код произведения велн-чнны К i на разряд величины 2 (который поступает с выхода ком гугатора 28 через элемент И 39 на первый вход сумматора 14). Поскольку регистры 1, 2, 5, 6, 9 и 10 содержат и -1 разрвд, а регистры 3, 4, 7 и 8 ц разрядов, то спустя И тактов двотпплые ко,аы в регистрах 1, 2, 5, 6, 9 и 10 сдвинутся на один разрад по отношению к двоичным кодам в регистрах 3, 4, 7 и 8, а также по о-тоше нию к сигналам четвертого выхода блока 2О синхронизапии. Поэтому в П +1-ОМ также на выходах элементов И 31, 32, 38 и 4О про- изой,пет совпадение сигналов в случае единичных кодов во вторых разрядах величин V i - 1 t; - 2 i - -1 , 9 i I сд гаемых с выходов регистров 5, 6, 2 и Ю соответствешю. Так как триггер. 21 в это время находится в нулевом состояни то комк утаторы 26-30 по,дключа1от выходь регистров 2, б, 7, 5 и 10 соответствешю к их входам соответстве1ШО, а с элементов И 33 и 36 снимается блокировка от триггера 21. В этом слу чае сумматор 13 формирует последовательный двоичный код суммы содержимог регистра 1, с,цВ1п аемого через элемент И 33, и произведения коэффт1иента А, сдвигаемого с выхода регистра 8, на второй разряд величины , , который с выхода регистра 2 через коммутатор 2 и элемент И 38 фиксируется в триггере 24. Сумматор 12 формирует последовательный двоичный код алгебраической суг1мы произведений коэффициентов В и сдвигаемых с выходов pervicTpo 3 и 4 соответствезшо, на BTOpfiie разряды веЛИЧ1Ш Ч - и i - 2 соответственно, которые фш сируются в триггерах 22 vi 23 соответственно. Сумматор 11 суммирует выходные сигналы сумматоров 12 и 13, а результирующая сумма сдвигается в регистр 1. В это время cyi -iMaTop 14 суммирует содержип юе регистра 9, которое сдвигае с я через элемент И 36, с произведением величшаы X j , сдвигаемой с выхода ре гист|:1а 7 через коммутатор 28 и эле{лент И 39, на второй разряд величины К J который с выхода регистра 10 через коммутатор 30 и элемент И 40 поступает в триггер 25. Сигналы суммы с выхода сумматора 14 сдвигаются в регистр 9. В каждом М -ом такте сигнал второго выхода блока 2О синхронизации через штертор 41 блокирует элементы И 33 и 36, оттмрая этим младшие разр{зды накапливаемой суммы в регистрах 1 и 9 соответственно. В дальнейшем устройство функционирует аналогичным образом и через h(n-i) тактов в ретист1эе 1 формируется П -1 старших разрядов выходной величины 2 , в прямом или дополнительном коде, а в регистре 9 формируется п -1 старших разрядов произведения Yi |; Xj Если в регистре 1 сформ 1рова/1ся допо/шительный код, то послдшпгй знаковый разряд с выхода сумматора 11 поступает через элемент И 61 в триггер 56 блока 19 знака Один цикл работы интегро-аи4)фЭреиииального вычислителя или один шаг вычислений заканчивается. Последующие шаги вычислений согласно соотношению (2) вьшолняются интегро-гдифференниальным вьшислителем аналогичным образом. Знак выхашюй величины 2 формируется на прямом выходе триггера 56 блока 19 знака и выходной шине 46. Последовательный код абсолютного значения величюш Z с,двигается с выхода регистра 1 через блок 15 формировантгя дополнительного кода на выходную шину 47. Технико-экономические преимущества предлагаемого интегро-дифференниального вычислителя заключаются в повьпиении быстродействия и в расширении функциональных возможностей. По сравнению с прототипом, в котором один шаг вычислений вьшолняется за 2 п ( П-1) тактов, быстродействие предлагаемого интегро-дифференциального вычислителя ддвое вьпие, так как у него один шаг вычислений занимает только П ( п -1) тактов. Функциональные возможности интегро- диф(})еренциального вычислителя позволяют кроме линей}П)1Х интегро-дифференциальных преобразований первого порядка выполнять также нелинейные инт ггродифференниальные преобразования, например интегро-дифференциальные преобразования лервого порядка с переменным коэффициентом усиления, значение которого изменяется в зависимости от од}юго из входных сигналов и.нтегро-диф(})еренциального вычислителя. Последовательное соединение рада саднотипных интегро-дифференциальных вычислителей, при котором выходные шигеы одного вычислителя подключаются к входным шинам другого вычислителя, позволяет реализовать сложные нелинейные интегро-дифференциальные преобразования высокого поряшса, например, с переме1шыми коэффициентами усиления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Справочник под ред | |||

| Г, Д | |||

| Хаски и Г | |||

| А | |||

| Корна | |||

| Т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М-Л., Энергия, 1964, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| С, Цифровые дифференциальные анализаторы | |||

| М,, Машиностроение, 1968, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-30—Публикация

1981-09-07—Подача