(54) ЦИФРОВОЙ гегулятор

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

1

Изобретение относится к автоматике и может быть использовано в системах управления различными динамическими объектами, например в системах автоматического регулирования технологическ№ми процессами на электростанциях.

Известен цифровой регулятор, содержащий датчик частоты, задатчик частоты, вычитатель частоты, счетчик, триггеры и логические элементы fl

Недостатками такого цифрового регулятора ЯВЛ51ЮТСЯ низкая точность и ограниченные функциональные, возможности, не позволяющие формировать сложные интегро-дифференциальные законы управления.

Наиболее близким к изобретению техг .ническим решением является цифровой регулятор, содержащий, первый, второй н третий регистры, первый сумматор, выход которого подключен к входу первого регистрш, блок настроек, блок знака, первый вход которого подключен к

первому входу регулятора и блок синхронизации. 2 J .

Недостатками известного регулятора 5юляются его относительная сложность, низкое быстродействие и ограниченные функциональные возможности.

Цель изобретения - упрощение yciw ройства, повышение его быстродействия и расширение функциональных возможное тей регулятора.

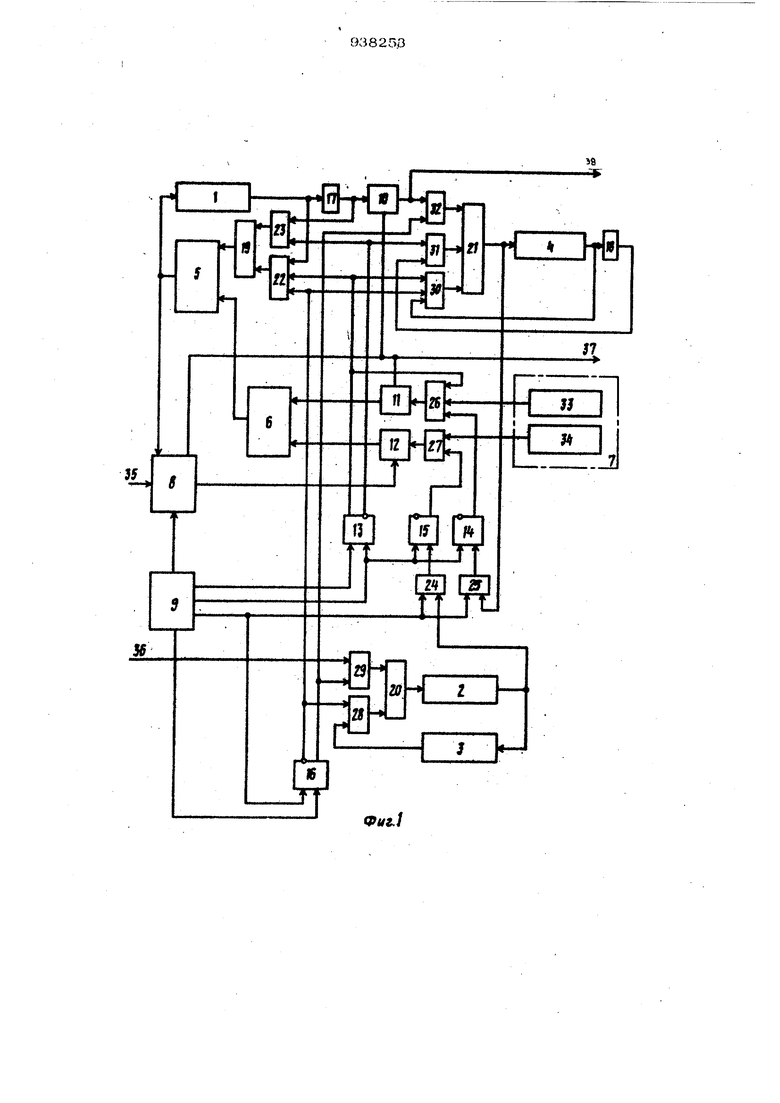

Поставленная цель достигается тем, что в него введены второй сумматор, четвертый регистр, первый, второй и третий блоки дополнительного кода, триггеры, элементы И, элементы ИЛИ и элементы задержки, причем выход первого регистра подключен к первому входу nei вого элемента И к входу первого элемента задержки, выход которого соединен с первым входом второго элемента И, первый вход первого сумматот)а подключен к выходу первого элемеито ИЛИ, первый и второй входы которого coonvuieiii.i го- ответственно с выходами первого и второго элементов И, второй вход первого сумматора подключен к выходу второго сумматора, первый и второй входы которого соединены соо-шетственно с выходами второго и третьего блоков дополнительного кода, блок знака подключен вторым входом к выходам первого сумматора, первым выходом - к первым входам первого и второго блоков дополнительного кода и к первому выходу регулятора, а вторым выходом - к первому входу третьего блока дополнительного кода, блок синхронизации подключен первым выходом к первым входам первого, второго и третьего триггеров, вторым вы- хьдом - к первому входу четвертого триггера и к первым входам третьего и четвертого элементов И, третьим выходом - к второму входу первого триггера, четвертым выходом - к второму входу четвертого триггера и пятым выходом - к третьему входу блока знака, первый и второй выходы блока настройки подключены соответственно к первым входам пятого и шестого элементов И, выходы которых соединены соответственно с вторыми входами второго и третьего блоков дополнительного кода, выход второго регистра подключен к второму входу третьего элемента И к входу третьего регистра, выход которого соединен с первым входом седьмого элемента И, первый вход восьмого элемента И подключен к второму входу регулятора, вход второго регистра подключен к выходу второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами седьмого и восьмого элементов И, вторые входы которых подключены к инверсному и прямому выходам четвертого , триггера, прямой выход первого триггера подключен к второму входу первого элемента И, к второму входу пятого элементе И и к первому входу девятого элемента И, второй вход которого соединен с третьим входом первого элемента И и с инверсным выходом четвертого триггера, инверсный выход первого триггера подключен к второму входу второго элемента И и к первому входу десятого элемента И, второй вход которого соединен с выходом второго элемента задержки, первый блок дополнительного кода подключен вторым входом к выходу первого элеменTia задержки и выходом - к второму выходу регулятора и к первому входу одиннадцатого элемента И, второй вход кото рОго. соединен с прямым выходом четвертого триггера, второй триггер подключен прямым выходом к третьему входу пятого элемента И и вторым входом. - к выходу четвертого элемента И, второй вход которого соединен с входом четвертого регистра и с выходом третьего элемента ИЛИ, третий триггер подключен прямым выходом к второму входу шестого элемента И и вторым входом - к выходу третьего элемента И, выход четвертого регистра подключен к входу второго элемента задержки и к третьему входу девятого элемента И, входы третьего элемента ИЛИ соединень соответственно с выходами девятого, десятого и одиннадцатого элементов И, соответственно. На фиг. 1 изображена блок-схема цифрового регулятора;. на фиг. 2 - блок.схема блоков знака и синхронизации. Регулятор содержит первый, второй, третий и яетвертый регистры 1-4, первый и второй сумматоры 5 и 6, блок 7 настроек, блок 8 знака, блок 9 синхронизашги, первый, второй и третий блоки 10 - 12 дополнительного кода, первый, второй, третий и четвертый триггеры 13 16, первый 17 и второй 18 элементы задержки, первый, второй и третий элементы ИЛИ 19, 20 и 21 и элементы И 22 - 32. Блок настройки 7 состоит из двух регистров 33 и 34, а также имеет входы 35 и 36 и выходы 37 и 38. Блок 8 знака (фиг. 2) содержит регистр 39, два триггера 4О и 41, элемент 42 неравнозначности, элемент ИЛИ 43, три элемента И 44, 45 и 46, а также имеет выход 47 и вход 48. Блок 9 синхронизации содержит генератор 49 тактовых импульсов, первый делитель 50 частоты, элемент el задержи ки, триггер со счетным входом 52 и втоpdft делитель 53 частоты, а также выходы 54 - 57. Блоки 1О - 12 дополнительного кода предназначены для преобразования последовательного двоичного кода в дополнительный код. Цифровой регулятор вырабатьтает регулирующее воздействие для каждого шага управления согла:сно соотношению --.,ъ,, где Y/f и YIH значения регулирующего воздействия в 4-м ти ( i.- 1).-м шагах управления, Х- и - значения рассогласования соответс твенно. Постоянные коэффициент : А, В, С зависят от вида закона управления или передаточной футасюш регулятора У(р;/Х(р; шага квантования по времени коэффициентов усиления и постоянных BpeNfeHH. Коэффициенты А, В, С предварительно рассчитываются и задаются регулятору. Их значения в блоке 7 настройки меняются, когда осуществляется переключения на новый закон управления либо меняютс шаг квантования по времени в соответствии с изменением режима работы объект в процессе его эксплуатации. Шаг квантования по времени выбирается исходя вз требования точности формирования регулирукацего воздействия и устойчивости системы авторегулирования. Соотношение (1) для двоичных переменных имеет следующий вид: . -1 -..i-fCX -si J7-JJ JlTIJH гдеу- - двоичная переменная раз- ряда величины X j -i M X;:- двоичные переменные j разрядов величин -i-xj и соответственно; И - количество разрядов представления двоичных переменных. Настройка цифрового регулятора осуществляется вводом, например от цифровой вычислительной машины ценфолизованного управления, двоичных кодов, постоянных коэффициентов А, В, С в регистры 33- и 34 блока 7 настрой ш, согласно требуемому закону управления, который выбирается в зависимости от режима работы регулируемого объекта и задачи управления., Регистр 33 сдвига имеет и разрядов и содержит двоичный код коэффшщен та А. Регистр 34 сдвига имеет 2vi разря дов, что позволяет ввести в него два V -разрядных кода коэффициентов В и С. Регистр 1 сдвига имеет И - 1 разря и дополняется до Vt разрядов элементов 1 задержки. В регистре 1 накапливается двоичный код регулирующего воздействия текущего шага управления. Регистр 4 сдвига имеет и- 1 раэряд и дополняется до Ш разрядов элементом 18 задержки. В регистре 4 хранитс двоичный код регулирующего воздействия предыдущего шага управления. Регистры 2 и 3 сдвига соответственно на d и VI-1 разряд предназначены для хранения двоичных кодов рассогласования на текущем и предыдущем шпслах управления. ии|)ровой регулятор работает следу1ощкм образом. С каждым шагом управления в регис1 ре 1 вычисляется новое значение вел чины регулирующего воздействия на ос5новании информации о текущем и предшест вующем значениях входной величины рас- согласования, хранящихся в регистрах 2 и 3 и о предшествующем значении регулирукяцего воздействия, которое содержит ся в регистре 4. Закон управления и его параметры задаются блоком 7 настройки, в регистры которого записываются двоичные коды трех коэффициентов А , В и С Коэффициент А записывается в разрядный регистр 33 сдвига, а коэффициенты В и С в 2и-разрядный регистр 34 сдвига. Знак регулирукяцего воздействия вырабатывается блоком 8 знака. Блок 9 синхронизации осуществляет синхронизацию работы устройства и определяет длительность цикла вычислений регулирукяцего воздействия. Блок 9 синхронизации работает сл&дующим образом. Генератор 49 тактовых импульсов (фиг. 2) вырабатывает последовательность тактовых импульсов с частотой f , которая делителем 5О частоты, преобразуется в последовательность импульсов 4aciтоты {/и . поступающие на первый выход 54 блока 9 синхронизации для синхронизации И-ых тактов, работы устройства. Элемент 51 задержки на один такт формирует последовательность импульсов частоты /и . которая поступает на шину 55 второго выхода блока 9 сишфонизашш для синхронизации первых тактов работы устройства. Триггер со счетным входом 52 выполняет деление на два входной последовательности импульсов, формируя на третьем выходе 56 блока 9 синхроннзацои последовательность импульсов с часто- той t /2и . Кроме этого, прямой и инверсный выходы триггера 52 управляют элементами И 44 и 45 блока 8 знака.. Делитель 53 частоты осуществляет деление входной последовательности импульсов в И раз, формируя на выходе последовательность импульсов частоты §/2и период следования которых определяет Юдин цикл работы устройства. Если на вход цифрового регулятора поступает сигнал рассогласования, то знак

рассогласоватга записывается по первому входу 35 -в первый разряд регистре 39 сдвига блока 8 знака, на шину сдвига которого поступает импульс с выхода 57 блока 9 сиюсронизации. Регистр 39 сдаи га имеет два разряда, в первсж разряде которого содержится знак рассогласовав ния текущего пикла, а во вт(Ьм разря де - знак рассогласования предыдущего цикла. Импульс текущего Ш1хла по шине 57 четвертого выхода блока 9 сишфон зации поступает на второй вход трштера 16, устанавливая его в единичное состоя ние. Сигнал прямого выхода tpurrepa 16 открывает элемент И 29, через который осуществляется запись И- и яднсхго последователыюго двоичного кода абсолютной величины рассЬтасовання в ре« гистр 2. Через и тактов двоичный код текущего значения рас огшсования, поступающий начиная с младпгах разрядов, с.второго входа 36 будет записан через элементы И29, ИЛИ20 в регистр 2.

В это же время сигнал выхода триггера 16 попоерживаег в открытом состоянии элемент И 32. Двоичный код регулирующего воздействия, вычисленный во время предыдущего пикла с выхода регистра 1 сдвига через элемент 17 задержки, который дополняет регистр 1 до И разрядов и блок 1Одопопнительногр кода записывается в регистр 4 через элемеаты И 32, ИЛИ 21. Двоичный код регулирующего воздействия передается с выхода регистра 1 на вход регистра 4 и выходную шину устройства 38 последовательно, начиная с младщих разрядов, за И тактов.;

Блок 10 дополнительного кода предназначен Для преобразования последоватепьн ич дополнительного кода, котораый формируется в регистре 1, -в случае oivрйцательной величины регулирующего во действгаг, в двоичный код абсЬлюгной величины регулирукяцего вогздей- ствия. Если в предыдущем цикле величвm 1зегулирукацего воздействия вычислена в дополнительном коде, сигнал знакового У1 НТО разряда с выхода сумматора 5 поступает на второй вход блока 8 знака и через элемент И 46 записывается в триггер 41, сигнал прямого выхода которого поступает на пе1шый выход блока 8 знака и выходную шину устройсттва 37. По этому сигналу блсж 10 дополи тельного кода переходит в режим формирования дополнительного кода отрицательной величины регулирующего воздействия.

который поступает с выхода регистра 1 через элемент 17 задержки на его второй вход. В результате на выходе блока 10 дополнительного кода формируется прямой двоичный код абсолютного значения рагугосрующего воздействия.

Если величина регулирукнцего возде{ н ствия положительна, на первом выходе блока 8 знака сигнал отсутствует и блок 1О дополнительного кода передает без изменений прямой код регулирующего воздействия.

В первом такте младщий разряд двоичного кода регулирующего воздействия предыдущего оикла поступает с выхода элемента ИЛИ 21 на вход регистра 4 и На второй вход элемента И 25, на первый вход которого в это время действует импульс второго выхода блока 9 синхронизашш. Если в младщем разряде регупирукнцего воздействия содержится единичный код, на выходе элемента И 25 формируется импульс, который устанавливает триггер 14 в единичное состояние. Сигнал прямого выхода триггера 14 поступает на третий вход элемента И 26, на втором входе которого действует прямого выхода триггера 13. Триггер 13 устанавливается в единичное состояние и лпульсом третьего выхода блока 9 син онизации.

Элемент И 26 переходит в открытое состояние и пропускает последовательный двоичный код коэффициента А, который , действует на первом выходе блока 7 настройки, на второй вход блока 11 дополнительного кода, управляемый сигнал первого выхода блока 8 знака.

Блок 11 дополнителыюго кода формирует прямой или дополнительный код козффишента А в зависимости от знака предыдущего значения регулирукяцей величины. В это же время сигнал младщего разряда предцдушего значения рассогла сования с выхода регистра 2 поступает на второй вход элемента U 24, на первом входе которого действует импульс второго блока 9 сиихронизаш1и.

Выходной сигнал элемента И 24 устанавливает в единичное состояние триггер 15, сигнал прямого выхода которого открывает элемент И 27. Последовательный двоичный код коэффициента В с второго выхода блока 7 настройки передается через элемент И 27 на второй вход блока 12 дополнительного кода, управляемого Сигналом второгоо выхода блока 8 знака. Который формируется следующим образом.

9938253lO

Сигйал знака предыдущего значенияСигнал прямого выхода триггера ГВ

рассогласования считывается с второгооткрывает элемент И 27, на первый вход разряда регистр 39 и поступает на вход элемента 42 неравнозначности, на второй вход которого поступает сигнап пвдмого выхода триггера 40. В триггере 4О запоминается знак коэффициента В На выходе элемента 42 неравнозначности формируется сигнал знака произведения коаффициента В на предыдущее значение рассогласования. Выходной сигнал элемента 42 неравнозначности через элемент И 45, управляемый триггером 52, и элемент ИЛИ 43 поступает на второй выход 47 блока 8 знака. Блок 12 дополнительного кода формирует в зависимости от знака произведения коэффициента В на предыдущее значение рассогласования прямой или дополнителъ- ный код коэффициента В , который последовательно, начиная с младшего разряда. поступает на второй вход последовательного двоичного сумматора 6. Сумматор 6 формирует последовательный двоичный код суммы или разности коэффициентов А и В, который через последовательный двоичный сумматор 5 записывается в регистр 1. Все описанные операции выполняются устройством за VI тактов. После этого в регистре 1, который дополняется алементом 17 задержки до п разрядов, будет записан последовательный двоичный код суммы или разности произведений коэ4 фициента А на ivHIaдшийpaзpяaпpeaыдyщeгo значения регулирующего воздействия и коэффициента Б на младший разряд предыдущего значения рассогласования. За эти же V тактов последовательный двоичный код предыдущего значения рассогласовария переписывается из регистра 2 в регистр 3, а последовательный двоич ный код текущего значения рассогласования записывается через элементы И 29, ИЛИ 20 в регистр 2. После этого триггер 16 сбрасьшается в нулевое состояние сигналом второго выхода блока 9 синхронизации. Сигнал инверсного выхода триггера 16 открывае элемент И 28, подключая этим выходом регистра 3 через элементы И 28, ИЛИ 2 к выходу регистра 2. Триггер 15 устанавливается в единичное состояние выходным сигналом элемента И 24, если в младшем разряде двоичного кода текущего значения рассогласования, считываемого с выхода регистра 2, содержится единичный код. которого с второго выхода блока 7 настройки поступает последователыЬдЙ двоичный код коэффициента С Блок 12 допотштельвсго кода, упра&ляемый сигналом знака текущего значения рассогласования с второго выхода блока 8 знака, формирует прямой шш до яоянителъный код коэффициента С ,кото|ый через сумматор 6 поступает на сумматор 5, где складывается с двоичным кодом суммы коэфиициентов Д и В . Двоичный код суммы коэффициентов А и. В посяедовательно считывается с выхода р гист 1 через элемент 17 задержки, элемент И 23, открытый сигналом mmepcного выхода триггера 13 и элемента ИЛИ 19 «а яервый вход сумматора 5, с выхо да двоичный код суммы коэффвшенгсж А , Б и С записывается в регистр 1 за время и тактов. Таким образом, спустя 2 И тактов в регистре 1 формируется сумма произве младших разрядов предыдупшх эначений регулирукндего воздействия и рас- согласования н текущего значения рассогласования на соответствующие значе- «ия коэффивдевтов А, В и С . то сигнал третьего выхода блока 9 син ронизагши устанавливает триггер 13 в единичное состояние. Сигнал прямого триггера 13 опсрывает элементы И 22 и И 30, а сигнал инверсного триггера 13 блокирует элементы И 23 и 31. В результате этого, выход регистра 1 подключается через элементы И 22, ИЛИ « первому входу сумматора 5. а выход регистра 4 подключается через элементы И 30; ИЛИ 21 к выходу четвертого регистра и к второму входу элемента И 25. Так как регистры 1 и 4 содержат И- 1 разр5щ, то за У тактов произойдет сдвиг содержащихся в них кодов на один разряд и с импульсом второго выхода блока 9 синхронизации будут совпадать вто- ® разряды регистров 1 и 4. последовательно соединенных регнс рах 2 и 3 также произойдет сдвиг содержащихся в них кодов на один разряд, так как регистр 3 содержит Vl - 1 разряд. Сдвиг двоичного кода на один разряд в регистре 1 обеспечивает умножение на два накопленной суммы коэф1)ициентом А , В и С . Сдвиг на один разряд кодов в регистрах 2, 3 и 4 обеспечивает совпа- дение с младшими разрядами кодов коэ4и фициентов А , В и С следующего второго разряда двоичных кодов расссгласования и регулирующего воздействия. Сигнал второго р азряда предыдущего значения регулируинцего воздействия с вы хода регистра 4 через элементы И 30, ИЛИ 21, И 25 устанавливает триггер 14 в единичное состояние к моменту считы- вання младшего разряда двоичного кода коэффициента А на перёом выходе блока 7 настройки. Сигнал второго разряда двоичного кода предыдущего значения рассогласования с выхода регистра 2 через элемент И 24 поступит на вход триггера 15, устанав;1ивая его в единичное состояние к момен ту считывания младшего р&зряда двоичнбго кода коэффициента В с второго выхода блока 7 настройки. Блока 11 и 12 дополнительного кода формируют прямой или дополнительные коэффициентов А и В соответственно, которые суммируются сумматором 6. Эта сумма произведений вторых разрядов предыдущих значений регулирующего воздействия и рассогласований на коэффициенты АИ В соответственно с вь5хода сумматора 6 поступает на второй вход сумматора 5, на первый вход которого поступает с выхода регистра 1, начиная с второго, разряда, сумма произведений первых разрядов предыдущих значений регулирующего воздействия, рассогласования и текущего значения рассогласования на коэффициенты А В и С COOTV. ветственно. Результат суммирования сумматором 5 записывается последовательно за Y( тактов в регистр 1. После этого триггера 13, 14 и 15 сбрасываются в нулевое состояние сигналом первого выхода блока Э синхронвза- шга. Триггер 13 в нулевом состоявши откр вает алементпы И 23, И 31 и блокирует элементы И 22, 26 в 30. Этим обеспечивается подключение выхода регистра 1 через элемент 17 задержки, элемент И 23, ИЛИ 19 к первому входу сумматора 5 и подключение выхода регистра 4 через элемент 18 задержки, элемент И 31 ИЛИ 21 к выходу регистра 4. Таким об|разом, регистры 1 и 2 дополняются элементами 17 и 18 задержн ки соответственно до У разрядов и в еледующие VI тактов сдвиг кодов в этих регистрах относительно сигналов блсжа 9 синхронизации отсутствует. 9

входу первого регистра, блок настроек, блок знака, первый вход которого подключен к входу регулятора и 5312 Сигнал второго разряда текущего зШйчения рассогласования с выхода регистра 2 через элемент И 24 устанавливает триггер 15 в единичное состояние, сигнал прямого выхода которого открывает элемент И 27. Двоичный код произведения второго разряда кода текущего значения рассоглассюания на коэффициент С поступает через блок 12 дополнительного кода в прямом или дополнительном коде на вход сумматора 6, на первом входе которого сигналы отсутствуют, так как элемент И 26 закрыт сигналом прямого выхода триггера 13, Двоичный код произведения второго разрацца текущего значения рассогласования на коэффициент с выхода сумматора 6 поступает на вход сумматора 5, который суммирует его с суммой, накопленной в регис1ре 1 на предыдущих тактах вычислений.На выходе сумматора 5 формируется сумма произведений первого и второго разрядов предыдущих значений регулирующего воздействия, рассогласования и текущего значения рассогласования на ко эффициентъ А, В и С соответственно, ко- . торая записывается за и тактов в регистр 1. Дальнейшая работа устройства до окончания цикла выч11слений, cBsi3aHHbix с выработкой регулирующего воздействия согласно заданного закона управления, а также в последующих циклах, осуществляемых на каждом шаге управления, аналогична. Такое техническое решение позволяет исключить из состава цифрового регулятора запоминающее устройство, сократив этим аппаратурные затраты на реализацию устройства и повысив его быстродействие, а также расширить его функциональные возможности, увеличив количество типов интегро-дифференциальных законе управления. Все это позволит получитъ определенный технико-экономический эффект в случае применения предлагаемого регулятора. Формула изобретения Цифровой регулятор, содержащий первый, второй и третий регистры первый сумматор, выход которого подключен

блок синхронизации, отличающийс я тем, что, с целью упрощения, повышения быстродействия и расширения функциональных возможностей регулятора, в него введены второй сумматор, четвертый регистр, первый, второй и третий блоки дополнительного кода, триггеры,, элемента И, элементы ИЛИ и элементы задержки, причем выход первого регистра подключен к первому входу первого элемента И, и к входу первого элемента задержки, выход которого соединен с первым входом второго элемента И, первый вход первого сумматора подключен к выходу первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, второй вход первого сумматора подключен к выходу второго сумматора, первый и второй входы которого соединены соответственно с выходами второго и третьего блоков дополнительного кода, блок знака подключен вторым входом к выходу первого сумматора, первым выходом - к первым входам первого и j-BTOporo блоков дополнительного кода и в первому выходу регулятора, а вторым выходом - к первому -входу третьего блока дополнительного кода, блок синхронизации подключен первым выходом к первым входам первого, второго и третьего триггеров, вторым выходом - к первому входу четвертого триггера и к первым входам третьего и четвертого элементов И, третьим выходом - ко второму входу первого триггера, четвертым выходом - ко второму входу четвертого триггера и пятым выходом - к третьему входу блока знака, первый и второй выходы блока настройки подключены соответственно к первым входам пятого и шестого элементов И, выходы которых соединены соот ветственно с вторыми входами второго и третьего блоков дополнительного кода, выход второго регистра подключен ко второму входу третьего элемента И и к входу третьего регистра, выход которого соединен с первым входом седьмого элемента И, первый вход восьмого элемента И подключен ко второму входу регулятора, вход вторся о регистра подключен к выходу второго элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами седьмого и восьмого элементов И, вторые . входы которых подключены соответственно к инверсному и прямому выходам чет вертого триггера, прямой выход первого триггера подключен к второму входу первого элемента И, к второму входу пятого элемента И и к первому входу девятого элемента И, второй вход которого соединен с третьим входом первого элемента И и с инверсным выходом четвертого триггера, инверсный выход первого триггера подключен к второму входу второго элемента VI и к первому входу десятого элемента И, второй вход которого соединен с выходом второго элемента задержlJcи, первый блок дополнительного кода Т одключен вторым входом к выходу первого элемента задержки и выходом - к второму выходу регулятора, и к первому входу одиннадцатого элемента И, второй вход которого соединен с прямым выходом четвертого триггера, второй триггер подключен прямым выходом к третьему входу пятого элемента И и вторым входом - к выходу четвертого элемента И, второй вход которого соединен с входом четвертого регистра и с выходом третьег элемента ИЛИ, третий триггер подключен прямым выходом ко второму входу шестого элемента И н вторым входом - к выходу третьего элемента И, выход четвертого регистра подключен к входу второго элемента задержки и к третьему входу девятого элемента И, входы третьего элемента ИЛИ соединены соответствегшо с выходами девятого, десятого и одиннадцатого элементов И.

Источники информадин, принятые во внимание при экспертизе

Фиъ.1

Авторы

Даты

1982-06-23—Публикация

1979-09-14—Подача