Изобретение относится к цифровой тзычислительной технике и может быть использовано в системах автоматического управления и навигации для преобразования при повороте декартовой системы координат на плоскости.

Известно устройство для преобразования координат, содержащее генератор тактовых импульсов, два сумматора, два блока умножения, два счетчика, сдвигатель, схемы сравнения, блок управления и схемы И, ИЛИ 1 .

Недостатком устройства является его невысокое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для преобразования координат, содержащее регистр первой координаты, выход которого соединен с первыд1И информационньоми входами первого и второго коммутаторов, регистр второй координаты, регистр старших разрядов угла поворота, регистр л/шадших разрядов угла поворота, соединенный по выходу С вторыми входами первого и второго коммутаторов, первый блок памяти, выход которого через первый информационный .вход третьего коммутатора подключен к первому входу сумматора, соединенного по выходу с входами, первого буферного регистра и первого выходного регистра,вычитатель, выход которого подключен к входам второго буферного регистра и второго выходного регистра, блок синхронизации, выходы которого подсоединены к управляющим входам первого, второго и третьего коммутаторов 2j

Недостатком устройства является его относительно невысокое быстро- действие, определяемое временем Т (2t-i + bn , где i - длительЕ ость такта работы устройства, в течение которого происходит пораэрядное сложение-вычитание и сдвиг чисел на регистрах, П - число разрядов операндов.

, Цель изобретения - повышение быстродействия,

Поставленная цель достигается тем, что в устройство, содержащее регистры первой и второй координат, первый и второй выходные регистры, первый и второй буферные регистры, регистры старших и младших разрядов угла поворота, первый блок памя ти, первый, второй и третий коммутаторы, сумматор, вычитатель и блок синхронизации, выход регистра-первой координаты подключен к первым информ.ационнЕдм входам первого и вт.орого коммутаторов, вторые информационные входы которых соединены с выходом регистра младших разрядов угла поворота, выход регистра старших разрядов угла поворота подключен к входу первого блока памяти, выход которого соединен с п-ервым информационным входом третьего коммутатора, выход которого подключен к первому входу сумматора, выход которого соединен с входами, первого буферного регистра и первого выходного регистра, выход вычитателя подключен к входам второго буферного

регистра и второго выходного регистра, первый и второй выходы йлока синхронизации соедийены с управляющими входами третьего коммутатора, а его третий выход подключен к управляющим входам первого и второго коммутаторов, дополнительно введены четыре блока умножения, пятый и шестой коммутаторы и второй блок памяти, вход которого подключен к

выходу регистра старших разрядов угла поворота, а. выход - к первым информационньЕ входам четвертого и пятого коммутаторов, выход регистра второй координаты соединен с первыми входами первого и второго блоков умножения, вторые входы которых подключены соответственно к выходам первого и второго буферных.регистров, а их выходы соединены соответственно с вторыми информационными входами третьего и пятого коммутаторов,

выход пятого коммутатора подключен

к первому входу вычитателя, первый

информационный вход шестого коммутатора подключен к выходу первого

блока памяти, вторые информационные входы четвертого и шестого коммутаторов соединены с выходами второго и первого буферных регистров соответственно, первые входы третьего

и четвертого блоков умножения подключены к выходам первого и второго коммьтаторов соответственно, а их выходы соединены с вторыми входами сумматора и вычитателя соответственно, вторые входы третьего и четвертого блоков умножения подключены к выходам четвертого и. шестого коммутаторов соответственно, управляющие входы четвертого и шестого коммутаторов соединены с первым выходом блока синхронизации, а управляющие входы пятого коммутатора подключены к первому и второму выходам блока синхронизации.

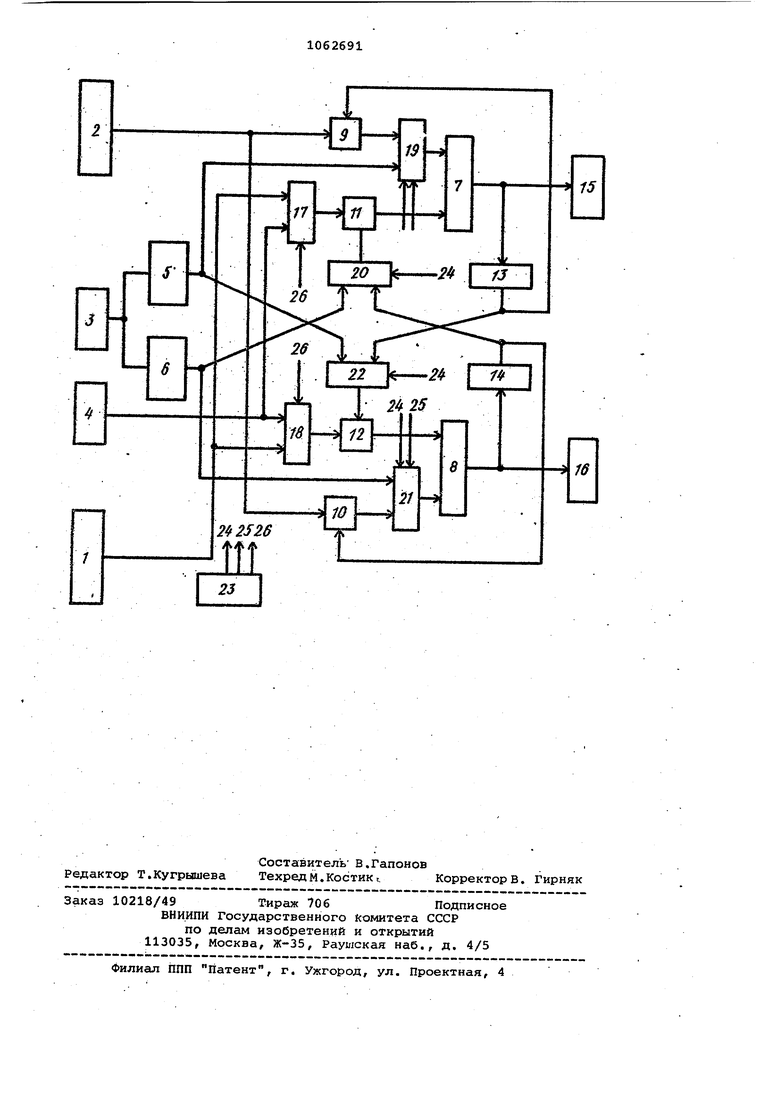

На чертеже представлена блок-схема устройства для преобразования декартовых координат.

Устройство содержит регистр 1 первой координаты, регистр 2 второй координаты, регистр.3 старших разрядов угла поворота, регистр 4 младших разрядов угла поворота, первый и второй блоки 5 и б памяти, сумматор 7, вычитатель 8, первый, второй, третий и четвертый блоки 9-12 умножения, первый и второй буферные

регистры 13 и 14, первый выходной регистр 15 и второй выходной регистр 16, первый, второй, третий, четвертый, пятый и шестой коммутаторы 17 - 22,-блок 23 синхронизации, первый, .второй и третий выходы 24 26 которого подключены к управляющим входам коммутаторов 17-22.

Регистр 1 первой координаты подключен к первыг информационным входам первого коммутатора 17 и второго коммутатора 18, регистр 2 второй координаты соединен с первыми входами первого и второго блоков 9 и 10 умножения. Первый вход третьего блока 11 умножения подключен к вы- ходу первого коммутатора 17, второй его вход - к выходу четвертого коммутатора 20, а выход - к второму входу сумматора 7. Первый вход четвертого блока 12 умножения соединен с выходом второго коммутатора 18, второй его вход - с выходом шестого коммутатора 22, а выход - с вторым входом вычитателя 8, Вторые информационные входы первого и второго ког/1мутаторов 17 и 18 подключены к выходу регистра 4 младших разрядов угла поворота, выход первого блока 5 памяти соединен с первыми информационными входами третьего и шестого коммутаторов 19 и 22, а выход второго блока 6 памяти подключен к первым информационным четвертого и пятого коммутаторов 20 и 21. Второй вход первого блока 9 умножения и второй информационный вход шестого коммутатора 22 соединены с выходом первого буферного регистра 13, вход которого подключен вместе с входом пер-вого выходного регистра 15 к выходу сумматора 7. Второй вхо второго блока 10 умножения и второй информационный вход четвертого коммутатора 20 соединены с выходом второго- буферного регистра 14, вход которого подключен вместе с входом второго выходного регистра 16 к выходу вычитателя 8. .Выходы первого и второго блоков 9 и 10 умножения через соответственно вторые информационные входы третьего и пятого коммутаторов 19 и 21 соединены с первыми входами сумматора 7 и вычитателя 8, Входы первого и второго блоков 5 и 6 памяти подключены к выходу регистра 3 старших разрядов угла поворота. Первый выход 24 блока 23 синхронизации соединен с управляющими входами четвертого и шестого коммутаторов 20 и 22. Первый и второй выходы 24 и 25 блока 23синхронизаид1и подключены к управляющим входам третьего и пятого коммутаторов 19 и 21. Третий выход 26 блока 23 синхронизации соединен с управляющими входами первого и второго коммутаторов 17 и 18.

Преобразование декартовых координат

х X co3(f +Ysin4, Y -X 64ft If +Yco5q,

где X,Y - значения первой и второй координат до преобразования}. - угол поворота системы в

радианах;

0 X, Y - новые значения первой и

второй координат,

выполняется на основе следующих соотношений.

Разложив двоичный код ,угла пово5рота If o.,ot,p4 , ...,pn Ha(k+2) -старших и ( n -k) младших разрядов, положим Cfo РЧ ,.. ., Рк О Щ Of О,..., ,..., РП , так что If Cfo + ЛЦ . ТогдаСоец) ,0

.-btf(5irKf +b S), einffo +

4-Mf (cos%-( ) , где погрешность вычисления Coscf и SITI ср выхо5 . дит за пределы разрядной сетки при k tt /3.

Устройство работает в три такта следующим образом.

Регистр 1 первой координаты содер0жит значение X, регистр 2 второй координаты - значение Y . На регистре 3 старших разрядов угла поворота и регистре 4 младших разрядов угла поворота хранятся соответственно зна5чения и tp . Первый блок 5 памяти хранит таблицу значений Cf, а второй блок 6 памяти содержит таблицу значений cos cp(j . Вычитатель 8 из числа, поступающего на первый вход,

0 вычитает число, поступающее на второй его вход, В начале работы устройства по значению Cfg на входах первого и второго блоков 5 и 6 памяти на выходе этих блоков образуются значения Son if о Hcosipo , поступающие соот5ветственно на первые информационные входы четвертого и шестого коммутататоров 20 и 22 со сдвигом, выполняемым шинами передачи, на один разряд вправо с образованием значений

0

isinifo и -IcosS-o .

В исходном состоянии, когда на входах блока 23 синхронизации отсутствуют управляющие сигналы, к выхо5дам коммутаторов 17 - 22 подключены их вторые информационные.входы.

В первом такте работы устройства блок 23 синхронизации выдает управляющий сигнал с первого выхода 24

0 на управляющие входы третьего, четт вертого, пятого, шестого коммутаторов 19 - 22, выходы которых подключаются к первым информационным их входам, а выходы первого и второго коммутаторов остаются подключенными

5

к .вторым информационным их входам. Поэтому поступающее на второй вход третьего блока 11 умножения с выхода четвертого коммутатора 20 значе1ние 2Со5Ч о умножается этим блоком

на передаваемое через первый коммутатор 17 с регистра 4 младишх разрядов угла поворота значение ьц . Промежуточный результат, равный

blf

-y coSCfg , поступает на второй вход

сумматора 7, на первый вход которого через третий коммутатор 19 с выхода первох о блока.5 памяти поступает значение 51 п iJo / образующееся затем на выходе сумматора 7 значение 5inqi(j + му-созфо запоминается

на первом буферном регистре 13, Одновременно в первом же такте на четвертый блок 12 умножения поступают через выгорай и шестой коммутаторы 18 и 22 значения соответств.енно

1 . и jSAncpg , образующие на его выходе

значение - йср Q , передаваемое н

второй вход вьочитателя 8, на первый вход которого через пятый коммутатор 21 приходит значение costfo выхода второго блока памяти б. Реь. , зультат вычитания cos - J S fo

запоминается на втором буферном регистре 8,.

Во втором такте работы устройства блок 23 синхронизации выдает управляющий сигнал с рторого выхода 25 на управляющие входы третьего и пятого коммутаторов 19 и 21, выходы которых подключаются к первым информационным их входам, а вь1хс5ды первого, второго, четвертого и шестого коммутаторов 17, 18, 20 и 22 к вторым информационным их входам,

ЛЧ Поэтому значения эхп Цо + -у созсроИ

&ч .

собсро - хранящиеся на первом и втором буферных регистрах 13 и 14, поступают соответственно на четвертый и третий блоки 12 и 11 умножения, умножаясь в них на значение &cf . На выходе сумматора 7 образуется значение 5ч п ср{, + &y(cos;(,1 , - )-stnc|i(j) sincf , запоминаемое на

b

первом буферном регистре 13, а на выходе вычитателя 8 образуется значение со з qio (( + -2-003%)

coetp, запоминаемое на втором буферном регистре 14.

В третьем такте работы устройства блок 23 синхронизации выдает управляющийсигнал с третьего выхода 26 на управляющие входы первого и второго коммутаторов 17 и 18, выходы которых подключаются к первым информационным их входам, а выходы третье го, четвертого, пятого и шестого коммутаторов 19 - 22 - к вторым их входам,

На выходе первого блока 9 умножения образуется значение V вдп (f , на выходе третьего блока умножения 5 значение X cosq) , складываемые на сумматоре 7 с образованием х Xtosif+ +Y5«hCff запоминаемом на первом выходном регистре 15. На выходе четвертого блока 12 умножения формиру0 .ется значение Xsin tp а на выходе второго блока 10 умножения - значение Ycoscf, вычитаемое на вычитателе 8 с образованием значения -Xsinqi +VCOS4I, запоминаемом на

5 втором выходном регистре 16.

Время Т работы устройства определяется соотношением

т Ф ц- чт

+ ЗТ

см

где ТЙЫБ время выборки из памятиf Туд - время умножения; TCM время суммирования. Если в качестве блоков умножения используются множительные устройства с анализом двух разрядов множителя, то Тцу - - Tgj,. . Для сумматоров с групповым переносом

(т задержка на логический вентиль, поэтому Т Ци+ 4 Тем (| + 4п +8)

Для прототипа время TQ выполнения преобразования в связи с тем, что

такт t при его работе не может быть сделан меньше ЗС, определяется отношением TQ г (2 п + 8п + 6V 3, Поэтому выигрыш по быстродействию для предложенного устройства по

сравнению с известным составляет

То 3(2п + 8п + б)

раз,

Т

+ 4И + 8

в частности, при И 16 и 24 этот выигрыш Составляет соответственно 11,5 и 12,6 раз.

Таким образом, данное устройство обладает более высоким быстродействием ,

ен

17

i I 22 |e-f / I

18

10

-Э

Ж

1$

15

24 /J f 2

8

16

21

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций двух аргументов | 1983 |

|

SU1191917A1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДЕКАРТОВЫХ КООРДИНАТ, содержащее регистры первой и второй координат, первый и второй выходные регистры, первый и второй буферные регистры, регистры старших и младших разрядов угла поворота, первый блок памяти, первый, второй и третий коммутаторы, сумматор, вычитатель .и . блок синхронизации, выход регистра первой координаты подключен к первым информационным входам первого и второго коммутаторов, вторые информационные входы которых соединены с выходом регистра младших разрядов угла поворота, вьэсод регистра старших разрядов угла поворота подключен к входу первого блока памяти, выход которого соединен с первым информационным входом третьего коммутатора, выход которого подключен к первому входу сумматора, выход которого соединен с входами первого буферного регистра и первого выходного регистра, выход вычитателя подключен к входам второго буферного регистра и второго выход- . ного регистра, первый и второй выходы блока синхронизации-соединены с управляющими входами третьего коммутатора, а его третий вьвсод подключен к управляющим входам первого и второго коммутаторов, о т л и ч а ющ е е тем, что, с целью повышения быстродействия, в него дополнительно введены четыре блока умножения, четвертый, пятый и шестой коммутаторы и второй блок памяти, вход которого подключен к выходу регистра старших разрядов угла поворота, а выход - к первым информационным в.ходам четвертого и пятого коммутаторов, выход регистра второй координаты соединен с первыми входами первого и второго блоков умножения, вторые входы которых подключены соответственно к выходам первого и второго буферных регистров, а § их выходы соединены соответственно с вторыми информационными входами (Л третьего и пятого коммутаторов, выход пятого коммутатора подключен к первому входу вычитателя, первый информационный вход шестого коммутатора подключен к выходу первого блока памяти, вторые информационные входы четвертого и шестого коммутаторов соединены с выходами второго и первого буферных регистров соответственно, первые входы третьего и четвертого блоков умножения подключены к выходам первого и второго коммутаторов соответственно, а их , выходы соединены с вторыми входами сумматора и вычитателя соответственно, вторые входы третьего и четвертого блоков умножения подключены к выходам четвертого и шестого коммутаторов соответственно, управляющие входы четвертого и шестого коммутаторов соединены с первым выходом блока синхронизации, а управляющие входы пятого коммутатора подключены к первому и второму выходам блока синхронизации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования координат | 1977 |

|

SU726534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для преобразования координат | 1977 |

|

SU660055A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-09-27—Подача