Изобретение относится к вычислительной технике и может быть исполь. зовано для расширения функциональных возможностей и повышения надежности работы устройства управления ЭВМ.

Известно микропрограммное устрой ство управления, содержащее блок памяти микрокоманд, регистр адреса, блок формирования адреса, блок выработки микроопераций, блоки задани контрольного режима и блок контроля L11.

Недостатком этого устройства является отсутствие контроля порядка правильности следования операций

Наиболее близким к предлагаемому является устройство, содержащее в своем составе блок выработки очередной микрокоманды, блок памяти микрокоманд, регистр микрокоманд, дешифратор кода микрокоманд, коммутатор, причем выходы блока выработки очередной микрокоманды соединены с входами блока памяти микрокоманд, выходы дешифратора-кода микрокоманд соединены с информационными входами коммутатора.

Для повышения надежности устройства в нем резервируются основные блоки - регистр микрокоманд, блок памяти микрокоманд, дешифратор и вводится регистр контроля. В случае выхода из строя одного из основных, блоков продолжают работать резервные обеспечивая надежное функционирование всего устройства 21.

Однако в известном устройстве невозможен контроль за порядком следования микрокоманд в микропрограмме. При нарушении порядка следования микрокоманд, например по причине случайного сбоя оборудования устройства управления, ошибка обнаружена не будет, т.е. произойдет отказ устройства.

Целью изобретения является повышение надежности за счет контроля правильности порядка следования микрокоманд в микропрограмме.

Указанная цель достигается тем, что в устройство микропрограммного управления, содержащее блок выработки очередной микрокоманды, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, первый выход дешифратора кода микрокоманд соединен с информационным входом первого коммутатора, выход которого подключен к выходуустройства, введены два элемента задержки, второй коммутатор, блок сравнения, блок определения ошибки и сдвигающий регистр кода микропрограммы, причем управляющий вход устройства содинен .с первым входом ключа и первым -управляющим входом блока выработки очередной микрокоманды, второй управляющий вход которого соединен с управляющим входом регистра микрокоманд, с входом первого элемента задержки, с вторым входом ключа и с выходом ключа через второй элемент задержки выход первого элемента задержки соединен с первым управляющим входом второго коммутатора, информационный и второй управляющий входы которого соединены соответственно с информационным и управляющим выходами регистра микрокоманд, первый выход второго коммутатора соединен с вхо дом сдвигающего регистра кода микponporpaMNM, выход которого соединен с первым входом блока сравнения второй вход которого соединен с вторым выходом дешифратора кода микрокоманд, вход которого соединен с вторым выходом второго коммутатора, выход блока сравнения подключен к информационному входу блока определения ошибки, выход которого соединен с управляющим входом первого коммутатора, а управляющий вход с управляющим выходом регистра микрокоманд и с третьим управляющим входом блока определения очередной микрокоманды, информационный вход которого соединен с адресным входом устройства.

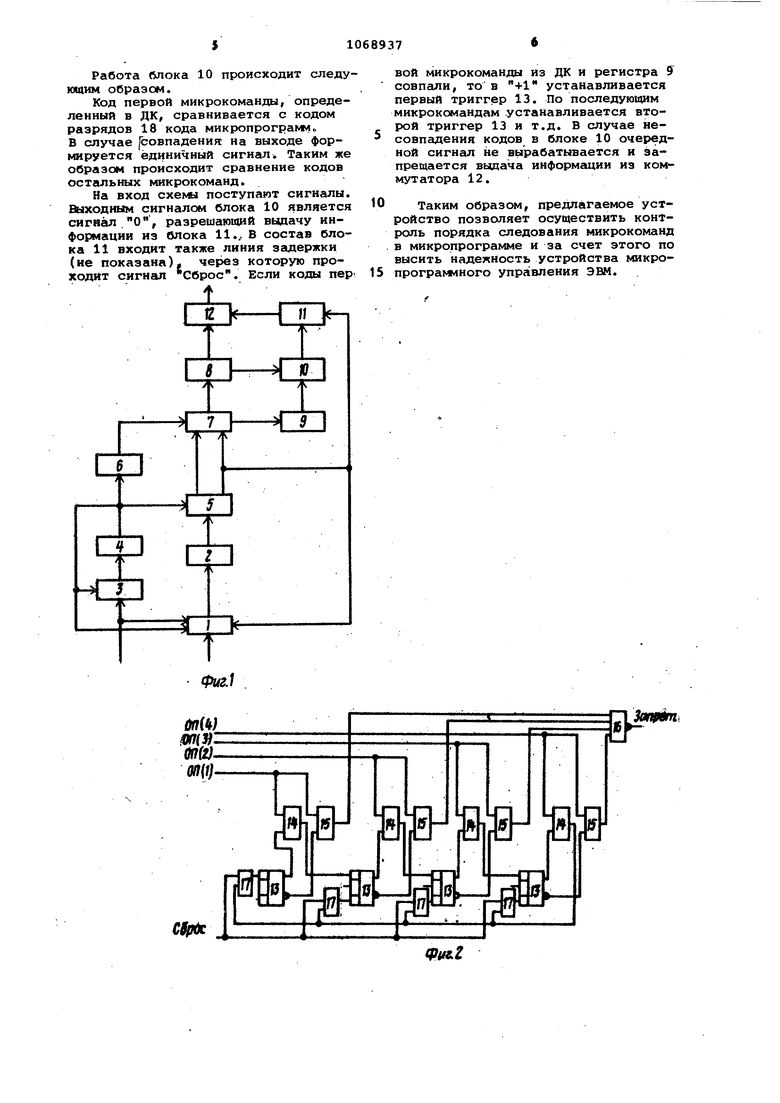

Кроме того, блок определения ошики содержит две группы элементов И, группу элементов ИЛИ, группу триггеров и элемент ИЛИ, причем информационный вход блока подключен к первым входам элементов И первой и второй групп, к вторым входам которых подключены соответственно прямые и инверсные выходы триггеров группы, к входам сброса которых, кроме первого, подключены выходы элементов ИЛИ группы, кроме первого выход которого соединен с единичным входом первого триггера группы, выходы элементов И первой группы, кроме последнего, подключены соответственно к единичным входам триггеров группы, кроме первого, выход последнего элемента И первой группы соединен с первыми входами элементов ИЛИ группы, вторые входы которых соединены с управляющим входом блока, выходы элементов И второй группы соединены с входами элемента ИЛИ, вьлход которого подключен к выходу блока.

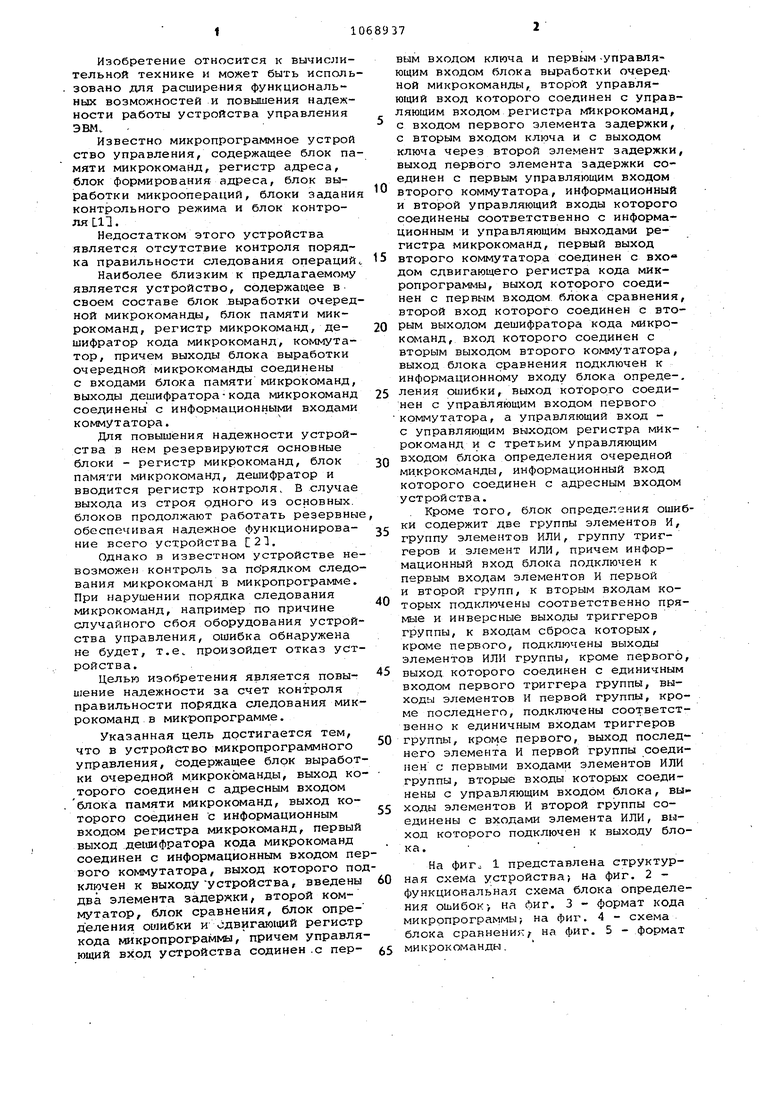

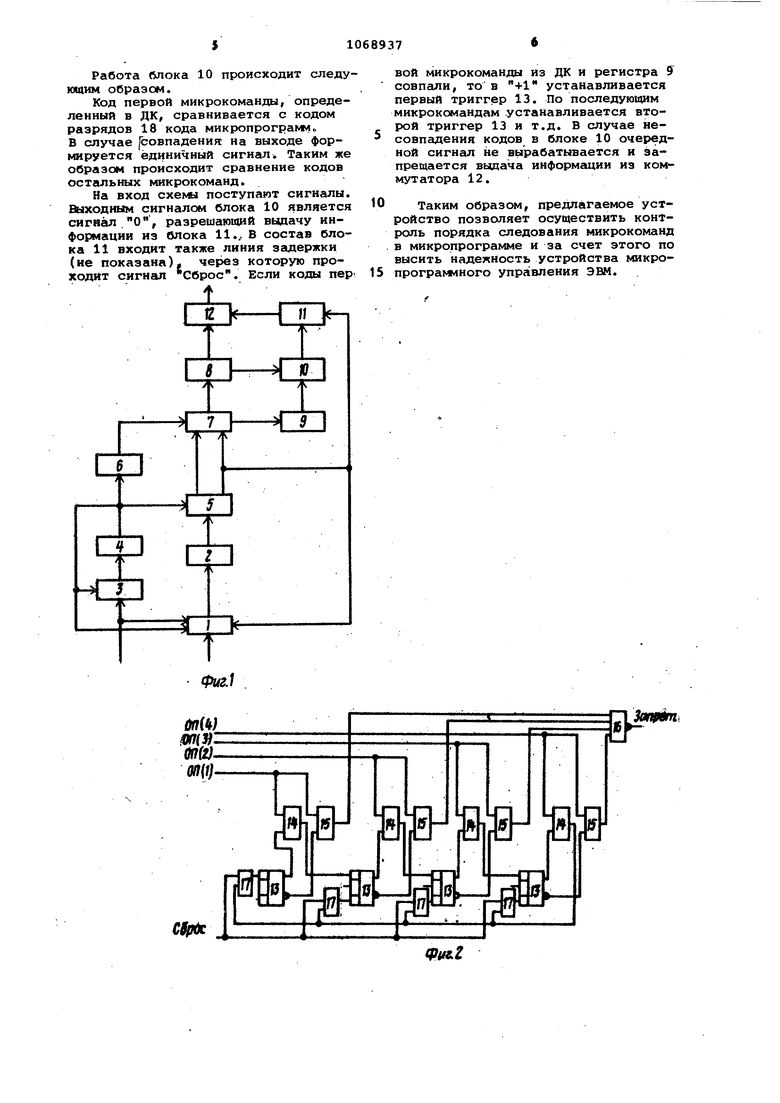

На фиго 1 представлена структурная схема устройства на фиг. 2 функциональная схема блока определения ошибок-, на Лиг. 3 - формат кода микропрограммы-, на фиг. 4 - схема блока сравнения/ на фиг. 5 - формат микрокоманды. Устройство содержит блок 1 выработки очередной микрокоманды, блок 2 памяти микрокоманд, ключ 3, элемент 4 задержки,, регистр 5 микрокоманд, элемент 6 задержки, коммутатор 7, дешифратор 8 кода микрокоманд, сдвигающий регистр 9. кода микропрограммы, блок 10 сравнения, блок 11 определения оишбки и коммутатор 12. Влок 11 определения ошибки (фиг содержит группу триггеров 13, группы элементов И 14 и 15, элемент ИЛ 16, группу элементов ИЛИ I. Форнат кода микропрограммы (фиг„ 3), состоящей из 4-х микрокоманд, состоит из 4-х групп 18-21 разрядов, первые, вторые,- третьи и четвертые разряды которых соответс вуют операциям сложения, вычитания умножения и деления. Блок сравнения (фиг. 4) содержи группы элеме.нтов И 22-26 и элементов ИЛИ 23. БЛОК выработки очередной микрокоманды (ВВОМК) представляет собой счетчик, информационный вход которо.го является входом устройства. На данный вход поступает адре-с выполняемой .команды. На первый управляющий вход одновременно с адресом поступает управляющий сигнал Прием адреса. Второй управляющий вход является счетным, на него поступа.ет сигнал +1. Сигналом по третьему yпpaвJJяющeмy входу БЮМК переводится в исходное состояние. ВПОМК предназначен для хранения микрокоманд., Регистр микрокоманд предназначен для хранения считанной из БПОМК микроманды. На управляющий вход РМ поступает задержанный сигнал 41, который разрешает занесение ь икрокоманды в данный регистр. Коммутатор 7 содержит в своем составе непосредственно коммутатор и триггер, управляюрдий коммутатором. Первый управляющий вход -представляет собой вход установки в О триггера. Второй управляющий вход КМИП представляет собой вход установки триггера . Если триггер находится в единичном состоянии, . то информация из КМИП выдается по второму информационному выходу, а в противоположном случае - по первому Дешифратор кода (ДК) микрокоман по первому выходу выдает все микро команды, а по второму - только результат дешифрации, кода опеграции микрокоманды. Предлагаемое устройство функцио нирует следующим образом. На вход устройства поступает ад рес микропрограммы и управляющий сигнал Прием адреса Адресом мик ропрограммы является код операции команды, которая .выполняется по данной микропрограмме. Адрес поступает на вход ВПОМК. С выхода блока 1 адрес подается в БПОМК. Считанная по данному адресу информация поступает в РМК. Разрешение приема информации в РМК происходит по задержанному сигналу Прием адреса. В первой ячейке, соответствующей каждой микропрограмме, хранится не микрокоманда, а код микропрограммы, который определяет последовательность микрокоманд, выполняе «ах по данной микропрограмме. В конце выполнения каждой микропрограммы триггер коммутатора 7 устанавливается в единичное состояние. Поэтсяиу код микропрограммы из РМК через коммутатор 7 поступает в регистр 9. Задержанным на элементе 4 сигналом Прием адреса триггер коммутатора 8 устанавливается в нулевое состояние. После элемента 4 сигнал Прием адреса поступает также на счетный вход БПОМК и на второй вход ключа. В БПОМК образуется адрес первой микрокоманды микропрограммы, которая считывается из ВПОМК в РМК. Сигнал на выходе ключа проходит через элемент 4 и управляет приемом в РМК, а также является сигналом +1 для ВПОМК. Так как триггер коммутатора 7 в нулев.ом состоянии, то микрокоманда из РМК через него поступает на вход ДК. Микрокоманда состоит из кода операции, адресной части и признака. Признак в ДК не поступает, он выдается по управляющему выходу РМК. У всех микрокоманд, кроме последней и. кода микропрограммы, значение признака нулевое. В последней микрокоманде микропрограммы значение признака единичное. Поэтому после считывания последней микрокоманды происходит установка в единичное состояние триггера коммутатора 7 и сброс ВПОМК и блока 10. После сброса ВПОМК он не реагирует на сигнал ,+1 до прихода сигнала Прием адреса. В начале выполнения первой программы выполняется команда Запуск, которая состоит из одной микрокоманды, имеющей единичное состояние признака. Это делается для установки в единицу триггера коммутатора 7, После того, как вся микрокоманда поступает из РМК в ДК, ее код операции дешифрируется, и выдается в блок 10, а микрокоманда поступает на коммутатор 12. В блоке 10 происходит сравнение кода микрокоманды из ДК с кодом микропрограммы.

Работа блока 10 происходит следующим образом.

Код первой микрокоманды, определеиный в ДК, сравнивается с кодом разрядов 18 кода микропрограмм. В случае (совпадения на выходе формируется единичный сигнал. Таким же образом происходит сравнение кодов остгшьных микрокоманд.

На вход схемы поступают сигналы. Выходным сигналом блока 10 является сигнал,О, разрешающий выдачу информации из блока 11... В состав блока 11 входит также линия задержки (не показана), через которую проходит сигнал Сброс. Если коды пер

вой микрокоманды из ДК и регистра 5 совпсши, то в +1 устанавливается первый триггер 13. По последующим микрокомандам устанавливается второй триггер 13 и т.д. В случае несовпадения кодов в блоке 10 очередной сигнал не вырабатывается и запрещается выдача информации из коммутатора 12.

Таким образом, предлагаемое устройство позволяет осуществить контроль порядка следования микрокоманд в микропрограмме и за счет этого по высить надежность устройства микропрограммного управления ЭВМ.

СО-4JJ

18

i9ZQ

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1981 |

|

SU960815A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168939A1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

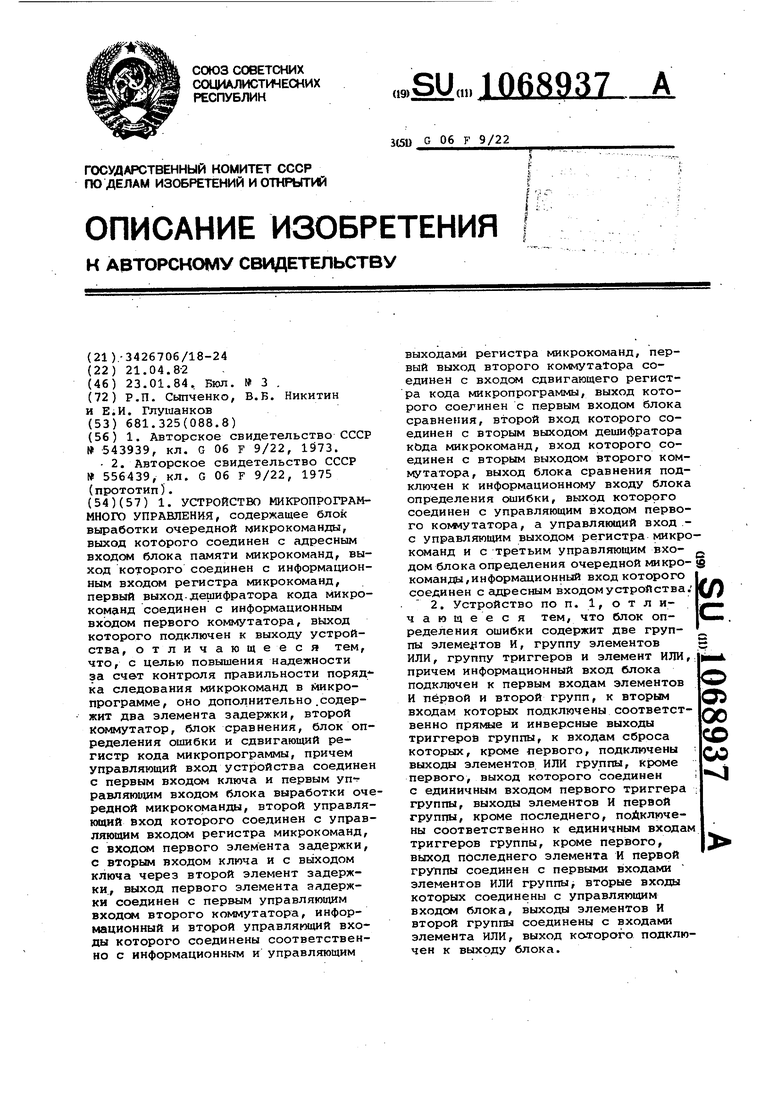

1. УСТРОЙСТЮ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее блок выработки очередной 4Икpoкoмaнды, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, первый выход-дешифратора кода микрокоманд соединен с информационным входом первого коммутатора, вЫход которого подключен к выходу устройства, отличающееся тем, что, с целью повышения надежности за счет контроля правильности поряд ка следования микрокоманд в Микропрограмме, оно дополнительно .содержит два элемента задержки, второй коммутатор, блок сравнения, блок определения ошибки и сдвигающий регистр кода микропрограммы, причем управляющий вход устройства соединен с первым входом ключа и первым управляюишм входом блока выработки очередной микрокоманды, второй управляющий вход которого соединен с управляющим входсяи регистра микрокоманд, с входе первого элемента згщержки, с вторым входом ключа и с вьгходом ключа через второй элемент задержки., выход первого элемента задержки соединен с первым управляющим входом второго коммутатора, информационный и второй управляющий входы которого соединены соответственно с информационным и управляющим выходами регистра микрокоманд, первый выход второго KOMMyTatopa соединен с входсм сдвигающего регистра кода микропрограммы, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с вторым выходом дешифратора кода микрокоманд, вход которого соединен с вторым выходом второго коммутатора, выход блока сравнения подключен к информационному входу блока определения ошибки, выход которого соединен с управляющим входом первого KONwyTaTopa, а управляющий вход с управляющим выходом регистра микрокоманд и с третьим управляющим входом блока определения очередной микрокоманды, информационный вход которого соединен с адресным входом устройства; 2. Устройство по п. 1, о т л ичающееся тем, что блок определения ошибки содержит две группы элеме1 тов И, группу элементов ИЛИ, группу триггеров и элемент ИЛИ,; причем информационный вход блока подключен к первым входам элементов О И первой и второй групп, к вторым входам которых подключены соответст00 венно пря1к&1е и инверсные выходы со со триггеров группы, к входам сброса которых, кроме первого, подключены выходы элементов ИЛИ группы, KjxjMe первого, выход которого соединен с единичным входом первого триггера ; группы, выходы элементов И первой группы, кроме последнего, поДключены соответственно к единичным входам триггеров группы, кроме первого, выход последнего элемента И первой группы соединен с первыми входами элементов ИЛИ группыj вторые входы которых соединены с управляющим входом блока, выходы элементов И второй групги соединены с входами элемента ИЛИ, выход которого подключен к выходу блока.

Сл.

Bwv

J/w.

Onttf)

3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления с самоконтролем | 1973 |

|

SU543939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство микропрограммного управления | 1975 |

|

SU556439A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-23—Публикация

1982-04-21—Подача