Изобретение относится к вычислительной технике, в частности к области запоминающих устройств.

Известны устройства для контроля 5 постоянных запоминающих устройств (ПЗУ) 1.

Недостаток их заключается в том, что они производят проверку ПЗУ в режимах, которые отличаются от режимов |Q работы ПЗУ в реальных изделиях.

Наиболее близким по технической сущности к пре.Щ1агаемому является устройство для контроля ПЗУ, содержащее блок управления, выходы которого подключены ко входу блока контроля чисет, ко входу .контролируемого блока ПЗУ, ко входу первого счетчика. Выходаа разрядов первого счетчика подключены ко входам контролируемого ПЗУ и ко входам cxeNW индикации кода адреса, а выходы разрядов - к выходам схеьы установки адреса. Входы разрядов блока контроля чисел подключены к выходам контролируемого25 ПЗУ, а выход - к блоку управленияЩ

Устройство работает при контроле ПЗУ в режимах:

циклического суммирования , в котором осуществляется поадресный вывод чисел из ПЗУ,их контрольное циклическое суммирование и сравнение контрольной cyMN« с расчетной суммой,

одиночный, при работе в котором производится однократный вывод числа по любому выбранному /.дресу;

непрерывного обращения к ПЗУ по любому адресу , в котором многократно выбирается число из ПЗУ по нужному адресу, отключается схема останова устройства.

Недостатком этого устройства является то, что оно производит контроль ПЗУ в режимах, отличающихся от режимов работы ПЗУ в реальных изделиях, что существенно снижает достоверность контроля ПЗУ.

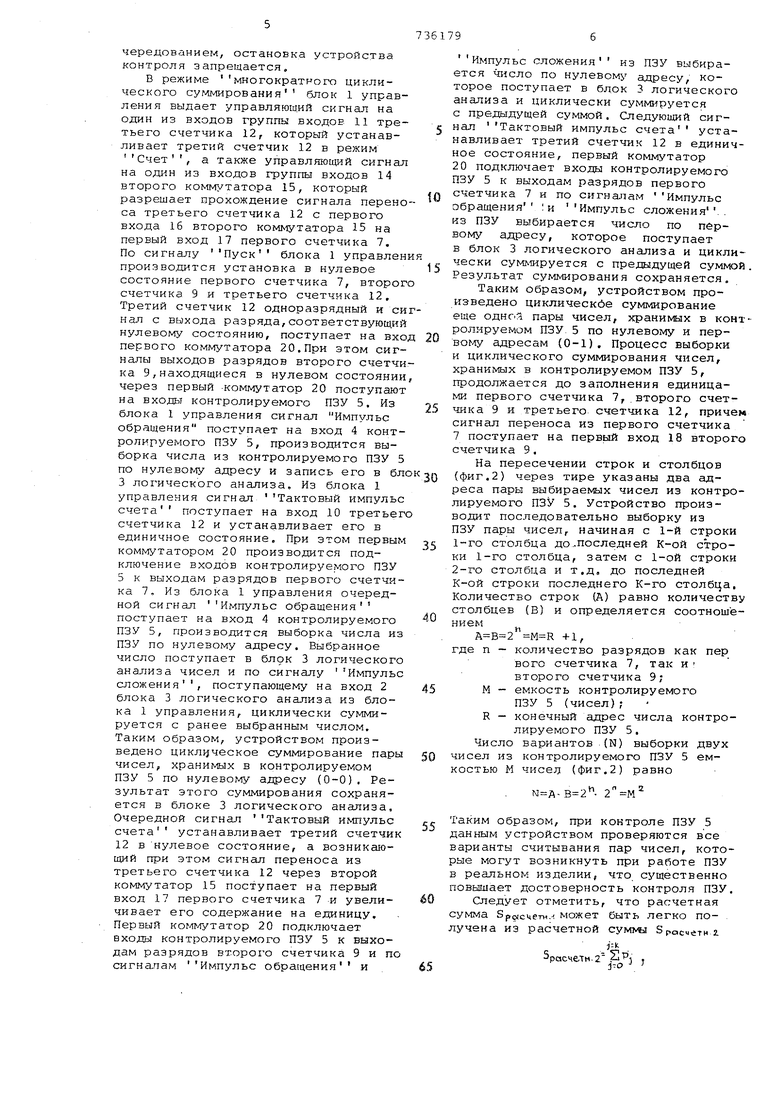

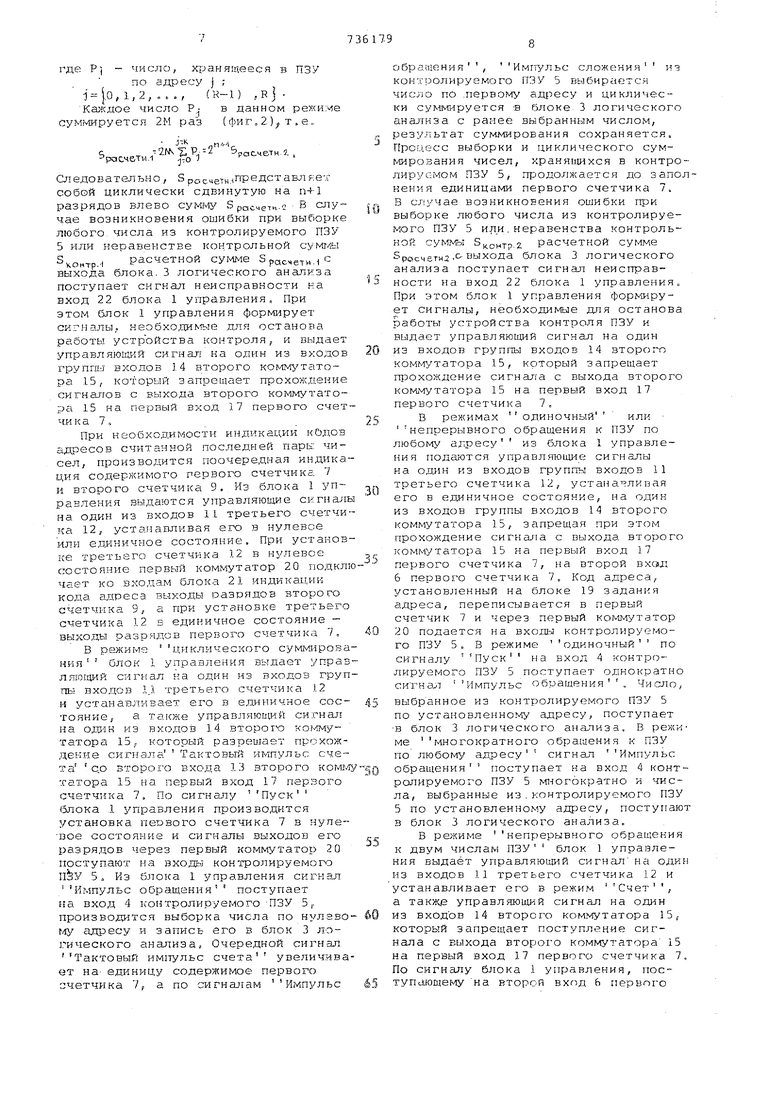

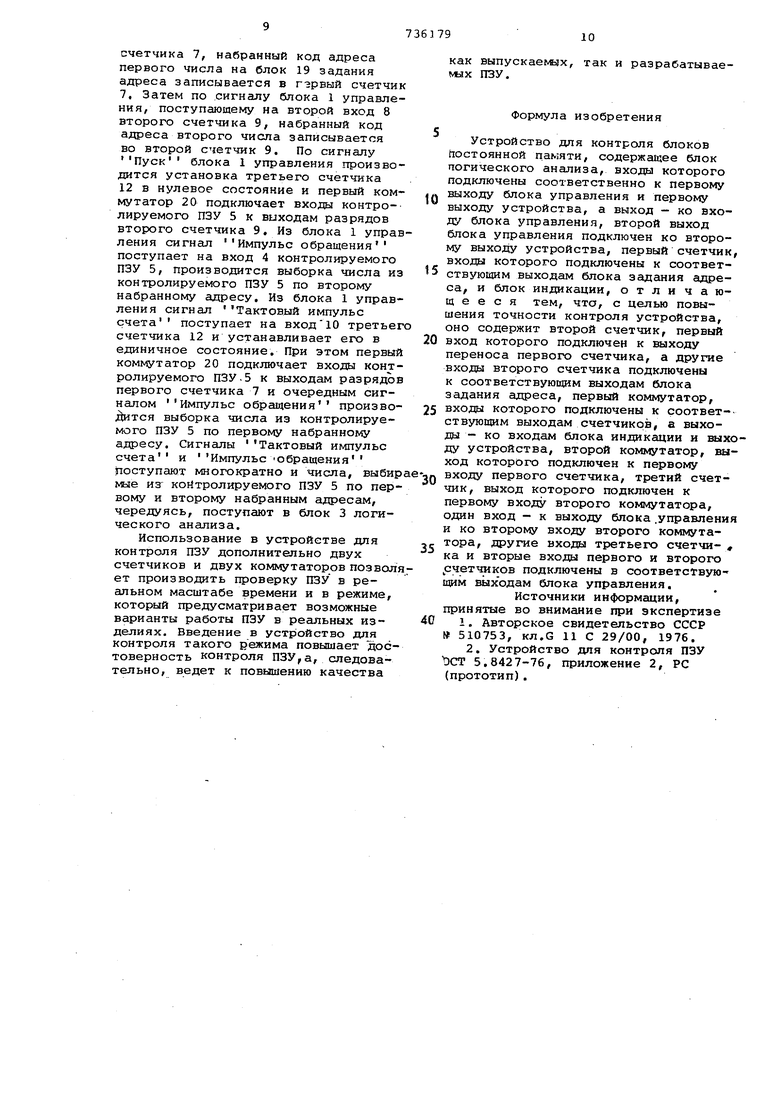

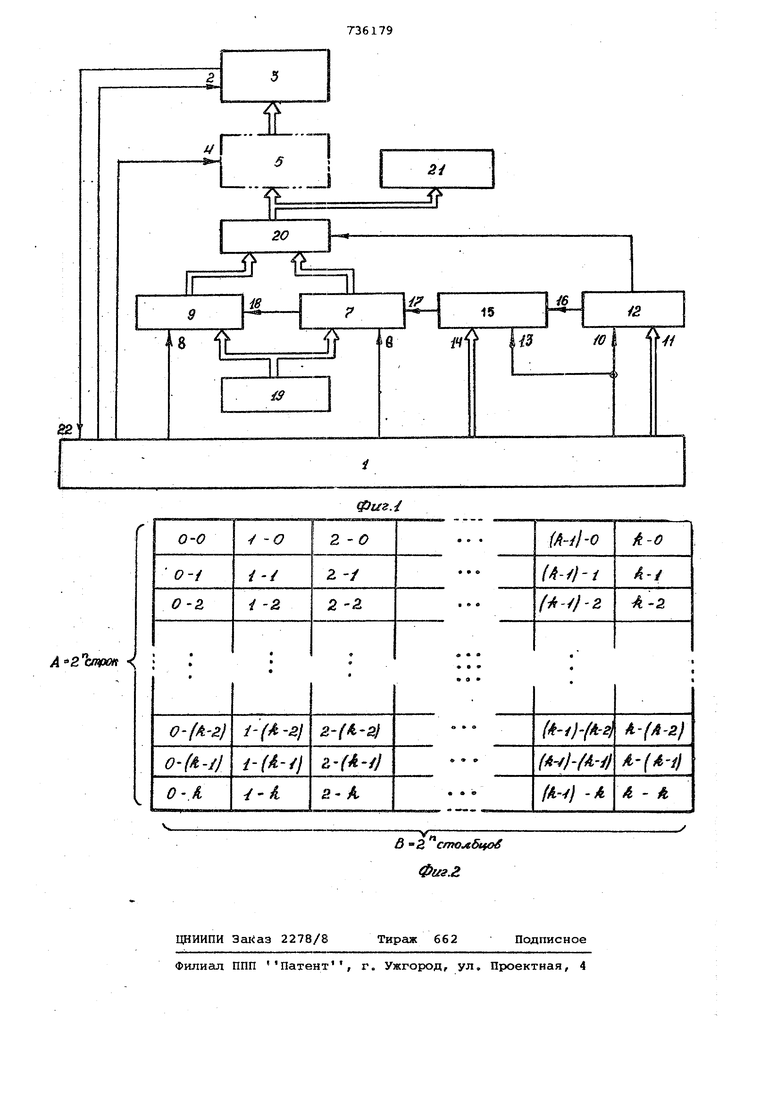

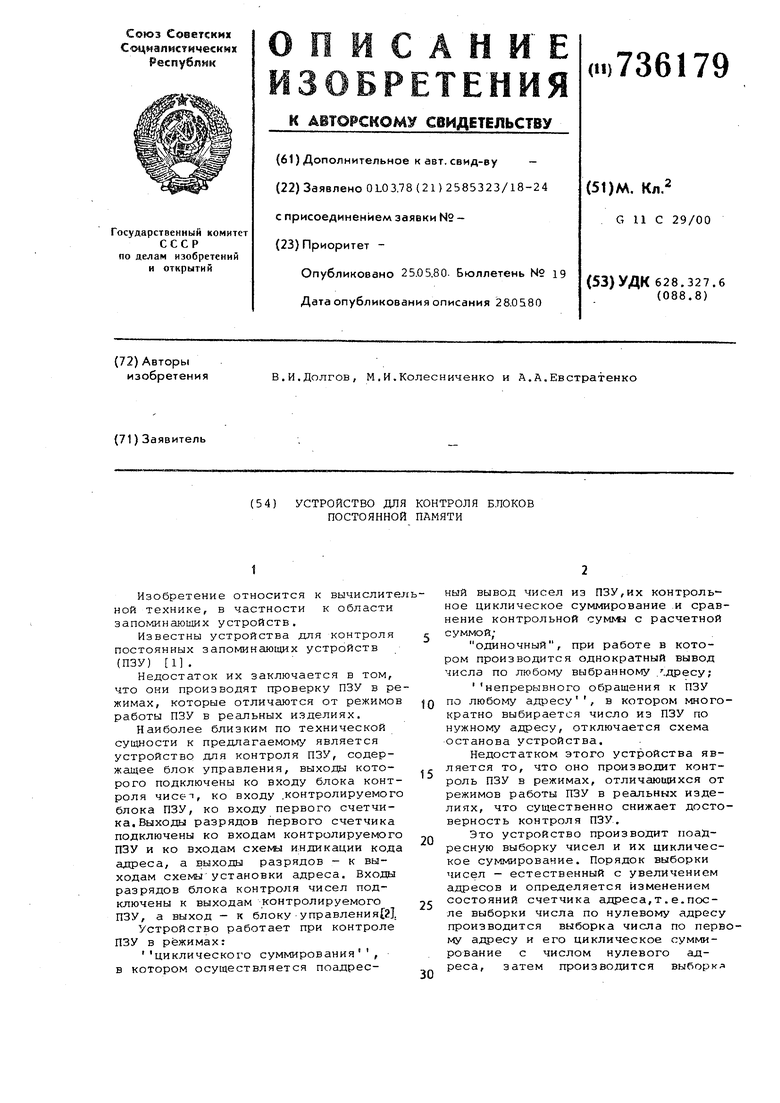

Это устройство производит поаДресную выборку чисел и их циклическое суммирование. Порядок выборки чисел - естественный с увеличением адресов и определяется изменением состояний счетчика адреса,т.е.после выборки числа по нулевому адресу производится выборка числа по первому адресу и его циклическое суммирование с числом нулевого адреса, затем производится выборкл чиапа по второму адресу и циклическ сум-мирован1 е его с полученной преды душей суммой и т.д. до числа,- храня щегося по последнем адресу. При , этом производится М раз циклических суммирований чисел, хранящихся в контролируемом ПЗУ, где М - емкость блока ПЗУ, При работе ПЗУ в реэ,пь-ных изделиях порядок выборки чисел может- быть любым, например три использовании ПЗУ в состгаве ЦВМ (универсальных, управляющих, специализированных)для хранения программ,подпрог рамм, констант , микропрограм- -и и т,д,, после выборки числа по определенному адресу последующая выЬоока числа може производиться по этогчту или любом другому адресу из всего массива М хранимых в ПЗУ чисел. При этом число вариантов (N) выборок двух чисел из ПЗУ елмкостьга М определяется чис.гом размещений из М чисел по два с ловтореннемОчевидно, что число вариантов выборок двух чисел из ПЗУ емкостью М, KOToptJe могут возникнуть при работе ПЗУ 3 реальных изделиях, гораздо больше проверяю цихся устройством контроля ЧТО существенно снижает достовернос контроля ПЗУ вьтшеуказ анным устройст вом. Цель изобретен 1Я - повышегпш точ ности контроля ПЗУ. Поставленная цель достигается те что в устройство .Ц-пя контроля введены второй счетчик, первый вход которого подключен к выходу перегюс первого счетчика, а , входы втор го счетчика подключены соответству ющим выходам блока задания адреса,п Bbifi коммутатор , вхолШ которого подклю чены к соответствующим выходам перво го и второго счетчиков, а вьлходы - к входам блока индикации и выход ;, ус ройства, второй коммутатор, выход которого подключен к пepвo / входупервого счетчика, третий счетчи с, выход которого подключен к первому входу второго комм татора, один вход - К выходу блока упраЕлени5; и второму входу коммутатора, другие входы третьего счетчика и вторые входы первого и второго счетчиков подключены к соответствующим выходдам блока управления . Вв(гдение в устройство контроля д счетчиков, двух коммутаторов и допол пительных связей позволяет производить устройством такой порядок выборок двух чисел из ПЗУ,который предус матривает всевозможные варианты выборок двух чисел. При этом число всевозможных вариантов выборок двух Щ1сел равно числу размещений- с повто рениями из М хранимых в ПЗУ чисел по два. При работе ПЗУ в реальных изделиях всегда будут встречаться выборок двух чисел из числа Бсевозможных и проверенных устройством контроля, что существенно повышает достоверность контроля ПЗУ ука3анным устройством, На фиг.1 представлена блок-схема устройства для контроля ПЗУ; на фиг.2EbiOi-rpaeivFbie пары чисел из контролируемого ПЗУ. Устройство для контроля ПЗУ содержит бл-ок 1 управления, выходы оторого подключены ко входу 2 блока 3 логическ-ого анализа, ко входу 4 контролируемого ПЗУ 5, которое является выходом устройства, ко BTOPOJ.-P/ входу 6 первого счетчика 7, ко второму вхо ду 8 вт-орого счетчика 9, ко входу 10 и к группе входов 11 третьего счетчика 12, ко второг- - входу 13 и к входам 14 второго коммутатора 15, Первый ВХОД , 16 второго KOMf-fyTaTopa 15 подключен к 5ЫХОДУ переноса третьего счетчика 12, а выход к первому входу 17 первого счетчика 17. Первый вход 1-8 второго счетчика 9 подключен к ВЫХОДУ переноса первого счетчика 7, входы разрядов первого счетчика 7 и второго счетчика 9 подключены к выходам блока 19 задания адреса. Входы первого ко мутатора 20 подключены к выходам разрядов первого счетчика 7, второго счетчигса 9, третьего счетчика 12, а выходы - ко входам контролируемого ПЗУ 5 и i-co входам блока 21 1- Ндикации кода адреса. Входы блока 3 логического анализа под; лючены к выходам контролируемого ПЗУ 5, а выход ко входу 22 блока 1 управления. Устройство работает при контроле П ЗУ в р е ж и М а х: многократного циклического сум. иронания , в котором пр-оизводится последовательно вк.иэорка пар чисел по схцре-сам со всевозможныг. размещения№1 их из М по два с повторениями,их коьтрольное цислическое суммирование и сравнение полученной контрольной суммы S кои-(п -I с расчетной суммой 3 расчет i, ци; лического сумм:--:роваь:ия , в кото;эом производится поадресная выборка чисел из ПЗУ,- их контрольное циклическое сугллмрование и сравнение Г;ОЛУчеННОЙ контрольной cyt-it J .-rp.2, с расчетной суммой Зрасче н.г : непрерывного обращения к ПЗУ по любому адресу , в котором многоратно выбирается число из ПЗУ по нужному Ei.npecy, остановка устройс т в а коп т р ол я з а п р е щ а е т с я; одиночный ,, при работе в котором производится однократный вывод числа г;о любому выбрггнному адресу; непрерывного обращения к двум числам ПЗУ , в котором тгроизвохштся многократная выборка двух чисел из ПЗУ по нчокным двум адресам с их чередованием, остановка устройства контроля запрещается. В режиме многократного циклического суммирования блок 1 управления выдает управляющий сигнал на один из входов группы входов 11 третьего счетчика 12, который устанавливает третий счетчик 12 в режим Счет, а также управляющий сигнал на один из входов группы входов 14 второго коммутатора 15, который разрешает прохождение сигнала перено са третьего счетчика 12 с первого входа 16 второго коммутатора 15 на первый вход 17 первого счетчика 7. По сигналу Пуск блока 1 управлен производится установка в нулевое состояние первого счетчика 7, второг счетчика 9 и третьего счетчика 12, Третий счетчик 12 одноразрядный и си нал с выхода разряда,соответствующий нулевому состоянию, поступает на вхо первого коммутатора 20.При этом сиг налы выходов разрядов второго счетчи ка 9,находящиеся в нулевом состоянии через первый -коммутатор 20 поступают на входы контролируемого ПЗУ 5, Из блока 1 управления сигнал Импульс обращения поступает на вход 4 конт ролируемого ПЗУ 5, производится выборка числа из контролируемого ПЗУ 5 по нулевому адресу и запись его в бл 3 логического анализа. Из блока 1 управления сигнал Тактовый импульс счета поступает на вход 10 третье счетчика 12 и устанавливает его в единичное состояние. При этом первы коммутатором 20 производится подключение входов контролируемого ПЗУ 5 к выходам разрядов первого счетчи ка 7, Из блока 1 управления очередной сигнал Импульс обращения поступает на вход 4 контролируемого ПЗУ 5, производится выборка числа и ПЗУ по нулевому адресу. Выбранное число поступает в блок 3 логического анализа чисел и по сигналу Импуль сложения , поступающему на вход 2 блока 3 логического анализа из блока 1 управления, циклически суммируется с ранее выбранным числом. Таким образом, устройством произведено циклическое суммирование пары чисел, хранимых в контролируемом ПЗУ 5 по нулевому адресу (0-0). Результат этого суммирования сохраняется в блоке 3 логического анализа. Очередной сигнал Тактовый импульс счета устанавливает третий счетчи 12 в нулевое состояние, а возникающий при этом сигнал переноса из третьего счетчика 12 через второй коммутатор 15 поступает на первый вход 17 первого счетчика 7 и увеличивает его содержание на единицу. Первый коммутатор 20 подключает входы контролируемого ПЗУ 5 к выходам разрядов BTOpoio счетчика 9 и по сигналам Импульс обращения и Импульс сложения из ПЗУ выбирается число по нулевому адресу, которое поступает в блок 3 логического анализа и циклически суммируется с предыдущей суммой. Следующий сигнал Тактовый импульс счета устанавливает третий счетчик 12 в единичное состояние, первый коммутатор 20 подключает входы контролируемого ПЗУ 5 к выходам разрядов первого счетчика 7 и по сигналам Импульс обращения : и Импульс сложения . . из ПЗУ выбирается число по первому адресу, которое поступает в блок 3 логического анализа и циклически суммируется с предыдущей суммой. Результат суммирования сохраняется. Таким образом, устройством произведено циклическбе суммирование еще однсл пары чисел, хранимых в контролируемом ПЗУ. 5 по нулевому и первo лy адресам (0-1), Процесс выборки и циклического суммирования чисел, хранимых в контролируемом ПЗУ 5, продолжается до заполнения единицами первого счетчика 7, второго счетчика 9 и третьего счетчика 12, причем сигнал переноса из первого счетчика 7 поступает на первый вход 18 второго счетчика 9. На пересечении строк и столбцов (фиг,2) через тире указаны два адреса пары выбираемых чисел из контролируемого ПЗУ 5. Устройство производит последовательно выборку из ПЗУ пары чисел, начиная с 1-й строки 1-го столбца до..последней К-ой строки 1-го столбца, затем с 1-ой строки 2-го столбца и т,д, до последней К-ой строки последнего К-го столбца. Количество строк (А) равно количеству столбцев (В) и определяется соотношением +1, где п - количество разрядов как пер вого счетчика 7, так и второго счетчика 9; М - емкость контролируемого ПЗУ 5 (чисел); R - конечный адрес числа контролируемого ПЗУ 5, Число вариантов . (N) выборки двух чисел из контролируемого ПЗУ 5 емкостью М чисел (фиг,2) равно . Таким образом, при контроле ПЗУ 5 данным устройством проверяются все варианты считывания пар чисел, которые могут возникнуть при работе ПЗУ в реальном изделии, что, существенно повышает достоверность контроля ПЗУ. Следует отметить, что расчетная сумма 8рр.счетн.ч может быть легко получена из расчетной Зрасчетнг о 5расчети-2 5 J

где Pj - число, храняи,ееся в ПЗУ

по адресу J ; .0, 1,2, ,. ., () ,R .

Каждое число Р.- в данном режиме суммируется 2М раз (фиг, 2 ), т , е ,.

-К.г

., 2

Го1

расчети.

Следовательно, S рс сиетк.1Лредставл я:ет собой циклически сдвинутую на n+i разрядов влево сумгиу S расчети-с В случае возникновения ошибки при выборке любого числа из контролируемого ПЗУ 5 или HepaFjeHCTse контрольной сумглы Зконтр.- расчетной сумме S расчетное выхода блока. 3 логического анализа поступает сигнал неисправности на вход 22 блока 1 управления. При этом 6.ЛОК 1 управления формирует сигналы,, необходикые для останова работы устрЪйства контроля, и выдает управляющий сигнал на один из входов групгдг входов 14 второго комм тато ра 15,, который запрещает прохождение сигналов с выхода второго коммутаторгг 15 на пех:)вый вход 17 первого счетчи к а 7 „

При необходимости индикации кОдов адресов считанной последней парь: чисел, производится поочередная индикация содержимого первого счетчика. 7 и второго счетчика 9, Из блока 1 управления выдаются управляюфю сигнал на один из входов 11 третьего счетчика 12, устанавливая его в нулевое или единичное состояние. При установке третьего счетчика 12 в нулевое состояние первый коммутатор 20 :гюдклчает ко входам блока 21 индикац1гги кода адреса выходы разрядов второго счетчика 9, а при установке третьего счетчика 12 в единичное состояние - выходы разрядов первого счетчика 1,

В ргукиме циклического cyMivtHposaния блок 1 управления вьтлает упразля10 ций сигнал на один из входов группы входов 11 третьего счетчика 12 и устанавливает его в единичное состояние, а также управляюгдий сигнал на один иэ входов 14 второтхэ татора 15J который разрешает прохождение сигнала Тактовый импульс счета со второго входа 13 второго KOMj.татора 15 на первый вход 17 первого счетчика 7. По сигналу Пуск (Злока 1 управления производится установка первого счетчика 7 в нулевое состояние и сигналы выходов его разрядов через первый коммутатор 20 поступают на вкодьз контролируемог1Э 5. Из блока 1 управления сигнал И.мпульс обращения поступает па вход 4 ко1ггролируемого ПЗУ 5,. производится выборка числа по нулзво1лу адресу и запись его в блок 3 лоз.-ического анализа. Очередной сигнал Тактовый им тульс счета увеличивает на единицу содержигуюе первого счетчика 1, а по сигналам Импульс

обраи-ения , Имгтульс сложения из контролируемого ПЗУ 5 выбирается число по .первому ад{:1есу и цикли- ески сук -мруется -в блоке 3 логического анализа с ранее выбранньзм числом, результат cyN№«5poBaHHH сохраняется. Прогдесс выборки и циклического суммирования чисел, хранящихся в контролируемом ПЗУ 5, продолжается до запонения единицами первого счетчика 7. В случае возникновения ошибки при выборке любого числа из контролируемого ПЗУ 5 И11и. неравенства контрольной суммь: 2 расчетной сумме Spcc4eTHi . выхода блока 3 логического анализа поступает сигнал неисправности на вход 22 блока 1 управления. При этом блок 1 управления формирует сигн;1лы, необходимые для останова работы устройства контроля ПЗУ и выдает управляющий сигнал на один из входов группь входов 14 второго кoм г/тaтopa 15, крторый запрещает птзохождение сигнала с выхода второго Коммутатора 15 на первый вход 17 первого счетчика 7,

В режимах одиночный или HenpeptiiBHoro обращения к ПЗУ по любому адресу из блока 1 управления подаготся управляющее сигналы на один из входов группы входов 11 третьего счетчика 12, устанаэливая его в единичное состояние, на один из входов группы входов 14 второго коммутатора 15, запрещая при этом прохождение сигнала с выхода второго коммутатора 15 на первый вход 17 первого счетчика 7, на второй вхад 6 первого счетчика 7. Код адреса, установленный на блоке 19 задания адреса, переписывс ется в первый счетчик 7 и через первый KorviMyTaTop 20 подается на входы контролируемого ПЗУ 5. В режиме одиночный по сигналу Пуск на вход 4 контролируемого ПЗУ 5 поступает однократно сигнал Импульс обращения . Число,

выбранное из контролируемого ПЗУ 5 по установленному адресу, поступает в блок 3 логического анализа. В режиме многократного обращения к ПЗУ по любому адресу сигнал Импульс обращения поступает на вход 4 контролируемого ПЗУ 5 многократно и числа, выбранные из.контролируемого ПЗУ 5 по установленному адресу, поступаю в блок 3 логического анализа.

В режиме непрерывного обращения к двум числам ПЗУ блок 1 управления выдаёт управляющий сигнгзл на оди из входов 11 третьего счетчика 12 и устанавливает его в режим Счет, а такисе управляющий сигнал на один из входов 14 второго коммутатора 15 который запрещает поступление сигнала с выхода второго коммутатора 15 на первый вход 17 первого счетчика 7 По сигналу блока 1 управления, поступающему на второй вход 6 первого счетчика 7, набранный код адреса первого числа на блок 19 задания адреса записывается в гэрвый счетчик 7. Затем по сигналу блока 1 управления, поступающему на второй вход 8 второго счетчика 9, набранный код адреса второго числа записывается во второй счетчик 9. По сигналу Пуск блока 1 управления производится установка третьего счетчика 12 в нулевое состояние и первый коммутатор 20 подключает входы контролируемого ПЗУ 5 к выходам разрядов второго счетчика 9. Из блока 1 управ ления сигнал Импульс обращения поступает на вход 4 контролируемого ПЗУ 5, производится выборка числа из контролируемого ПЗУ 5 по второму набранному адресу. Из блока 1 управ ления сигнал Тактовый импульс счета поступает на вход10 третье счетчика 12 и устанавливает его в единичное состояние. При этом первый коммутатор 20 подключает входы конт ролируемого ПЗУ.5 к выходам разрядо первого счетчика 7 и очередным сигналом Импульс обращения произво Йится выборка числа из контролируемого ПЗУ 5 по первому набранному адресу. Сигналы Тактовый импульс счета и Импульс Обращения поступают многократно и числа, выбир мые из контролируемого ПЗУ 5 по пер вому и второму набранным адресам, чередуясь, поступают в блок 3 логического анализа. Использование в устройстве для контроля ПЗУ дополнительно двух счетчиков и двух коммутаторов позвол ет производить проверку ПЗУ в реальном масштабе времени и в режиме, который предусматривает возможные варианты работы ПЗУ в реальных изделиях. Введение в устройство для контроля такого режима повышает дос товерность контроля ПЗУ,а, следовательно, ведет к повышению качества как выпускаемых, так и разрабатываемых ПЗУ. Формула изобретения Устройство для контроля блоков йостоянной памяти, содержащее блок логического анализа, входы которого подключены соответственно к первому выходу блока управления и первому выходу устройства, а выход - ко входу блока управления, второй выход блока управления подключен ко второму выходу устройства, первый счетчик, входы которого подключены к соответствующим выходам блока задания адреса, и блок индикации, о т л и ч а ющ е е с я тем, что, с целью повышения точности контроля устройства, оно содержит второй счетчик, первый вход которого подключен к выходу переноса первого счетчика, а другие входы второго счетчика подключены к соответствующим выходам блока задания адреса, первый коммутатор, входы которого подключены к соответ-ствующим выходам счетчиков, а выходы - ко входам блока индикации и выходу устройства, второй коммутатор, выход которого подключен к первому входу первого счетчика, третий счетчик, выход которого подключен к первому входу второго коммутатора, один вход - к выходу блока .управления и ко второму входу второго коммутатора, другие входы третьего счетчи-, ка и вторые входы первого и второго f:4eT4HKOB подключены в соответствующим выходам блока управления. Источники информсщии, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 510753, кл.С 11 С 29/00, 1976. 2. Устройство для контроля ПЗУ ОСТ 5.8427-76, приложение 2, PC (прототип).

и

..

2i

ur

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Устройство для обнаружения ошибок в блоках памяти программ | 1982 |

|

SU1278982A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля блоков постоянной памяти | 1990 |

|

SU1795522A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

IT 1

is

Т

8 А гЪлрок

J

//J

/г

15

Л

3

Л

//

Фиг.

Авторы

Даты

1980-05-25—Публикация

1978-03-01—Подача