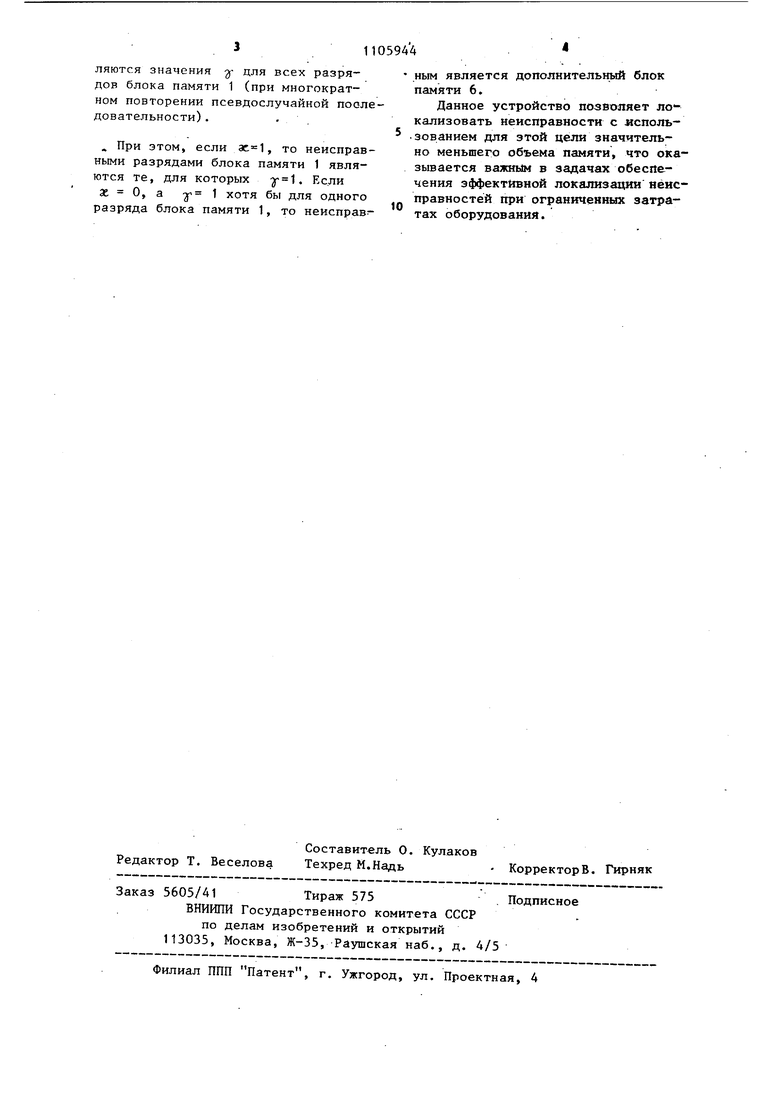

11 Изобретение относится к запоминающим- устройствам, в частности к запоминающим устройствам со встроенными аппаратными средствами контроля и отладки, и может быть использовано в качестве оперативной памяти ЭВМ Известно оперативное запоминающее устройство с самоконтролем, содержащее блок памяти, счетчик, регистр, схему сравнения, элемент ИЛИ, блок управления, дешифратор, блок вентилей, мультиплексоры, блоки {индикации и. Однако это устрЪйство ориентирова но на использование -определенных тес товьгх последовательностей и не позволяет локализовать неисправности по ошибкам, возникающим на произвольных псевдослучайных последовательностях. Это обстоятельство усложняет отдадку памяти. Известно запоминающее устройство с самоконтролем, содержащее блоки памяти, выходы которых подключены к первым входам соответствующих блоков контроля, блок формирования сигнала отказа, выходные и управляющие шины, блок задержки строба считывания и бло ки поразрядного сравнения, входы которых подключены соответственно к выхоДам блоков памяти, блоков контроля и блока задержки строба считывания, а выходы к выходным шинам и одним из входов блока формирования сигнала отказа, другие входы которого соединены с вьгходами блоков контроля, выходы блока формирования сигнала отказа подключены соответственно к вторы входам блоков контроля и одному из входов блока задержки строба считывания, другой вход которого соединен с управляющей шиной 3. Недостатком устройства является его сложность. Цель изобретения - упрощение устройства, Указанная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее блок памяти, входы которого являются информационными входами устройства, блок контроля, входы которого соединены с выходами блока памяти, а выход является первым контрольным выходом устройства, выходы блока памяти являются информационными выходами -устройства, введены первый и второй коммутаторы, блок управления, дополнительный 4 блок памяти и сумматор по модулю два, причем информационные входы первого и второго коммутаторов подключены соответственно к входам и выходам блока памяти, вход блока управления является управляющим входом устройства, а выход подключен к управляющим входам коммутаторов, выход первого коммутатора подключен к входу дополнительного блока памя-. ти, выход которого соединен с первым входом сумматора по модулю два, второй вход которого подключен к выходу второго коммутатора, выход сумматора по модулю два является вторым контрольньм выходом устройства. На чертеже представлена структурная схема устройства. Устройство содержит блок памяти 1, блок контроля 2, первый и второй коммутаторы 3 и 4, блок управления 5, дополнительный блок памяти 6 и сумматор 7 по модулю два. Устройство работает следующим образом. В блок памяти записывается псевдослучайная последовательность слов, включающая как информационные разряды, так и соответствующие им, вычисленные ранее, контрольные разряды, например по модулю 3. Считываемая из блока памяти 1 информация, поступает на выходы устройства, а также на входы блока контроля 2, сопоставляющего информационную и контрольную часть слов и вырабатывающего сигнал контроля X. ( г 1 при наличии ошибки). В блоке управления 5, реализованном, например, в виде тумблерных переключателей, имеющих два положения 1. и О, задается двоичный код i . Этот код поступает на адресные входы первого и второго коммутаторов 3 и 4, выбирающих при этом сигналы с входа и выхода i-го разряда блока памяти 1. С выхода первого коммутатора 3 сигнал заносится в одноразрядный дополнительный блок памяти 6, устроенный подобно части блока памяти 1, хранящей один разряд. С выхода второго коммутатора 4 и выхода дополнительного блока памяти 6 сигналы поступают на входы сумматора 7 по модулю два, вырабатывающего сигнал проверки i-го разряда блока памяти 1. Заданием различных кодов на адресые входы коммутаторов 3 и 4 опреде - . 1105 ляются значения у для всех разрядов блока памяти 1 (при многократном повторении псевдослучайной последовательности). , . При этом, если , то неисправными разрядами блока памяти 1 являются те, для которых у 1. Если Ж О, а у 1 хотя бы для одного раэряда блока памяти 1, то неисправ944 ным является дополнительный блок памяти 6. Данное устройство позволяет ло кализовать неисправности с исполь5 .зеванием для этой цели значительно меньшего объема памяти, что оказывается важным в задачах обеспечения эффективной локализациияёисправностёй при ограниченных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1277216A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1001174A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

ЗАПОМИНАМЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее блок памяти, входы которого являются информационными входами устройства, блок контроля, входы которого соединены с выx) блока памяти, а выход является первым контрольным выходом устройства, выходы блока памяти являются информационными выходами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены первый и второй коммутаторы, блок.управления, дополнительный блок памяти и сумматор по модулю два, причем информационные входы первого и второго коммутаторов подключены соответственно к входам и выходам блока памяти, вход блока управления является управляющим входом устройства, а выход подключен к управляющим входам коммутаторов, выход первого коммутатора подключен к входу дополнительного блока памяти, (Л выход которого соединен с первьм входом сумматора по модулю два, второй вход которого подключен к выходу второго коммутатора, выход сумматора по модулю два является вторым контрольным выходом устройства. ел со 4 д;

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устрой-CTBO C САМОКОНТРОлЕМ | 1979 |

|

SU809402A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU696545A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-30—Публикация

1983-05-23—Подача