Изобретение относится к вычислительной технике и может быть использовано в з апоминающих устройствах на транзисторах для запоминания адресных сигналов и формирования сигналов, поступающих на дешифраторы запоминающего устройства.

Цель изобретения - повышение надежности и быстродействия адресного формирователя.

После подачи тактового сигнала обеспечивается блокировка информационного входа от внутренних элементов формирователя с помощью выходных сигналов формирователя.

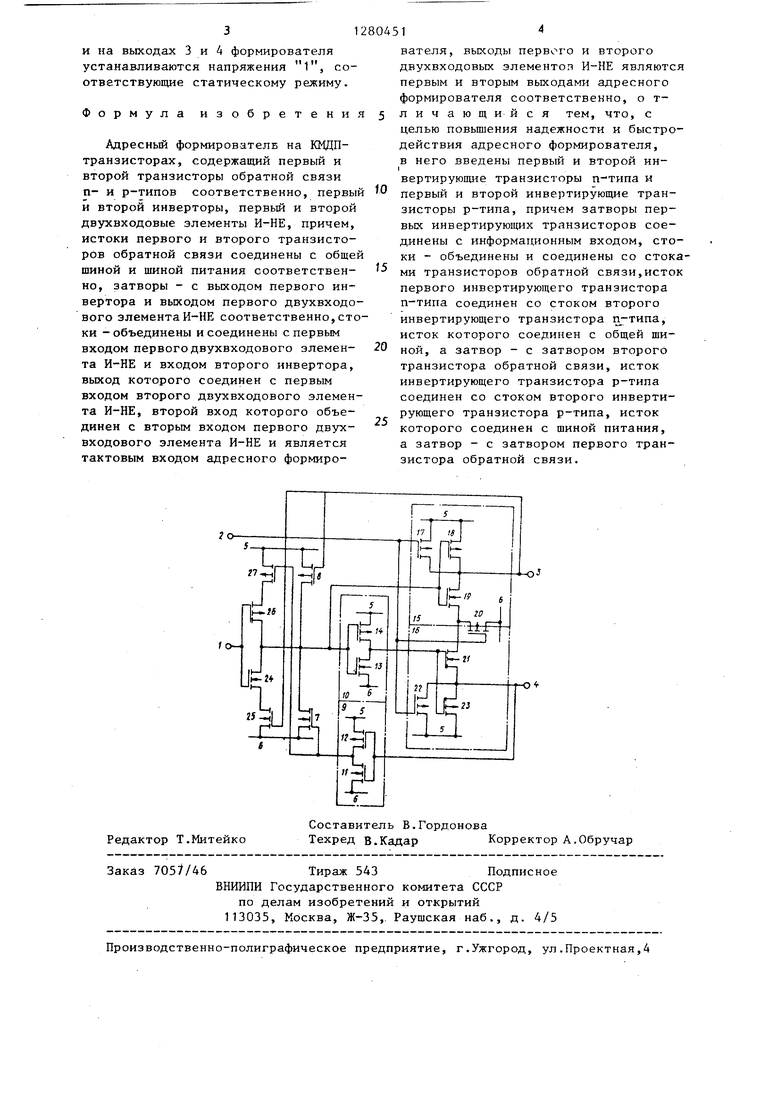

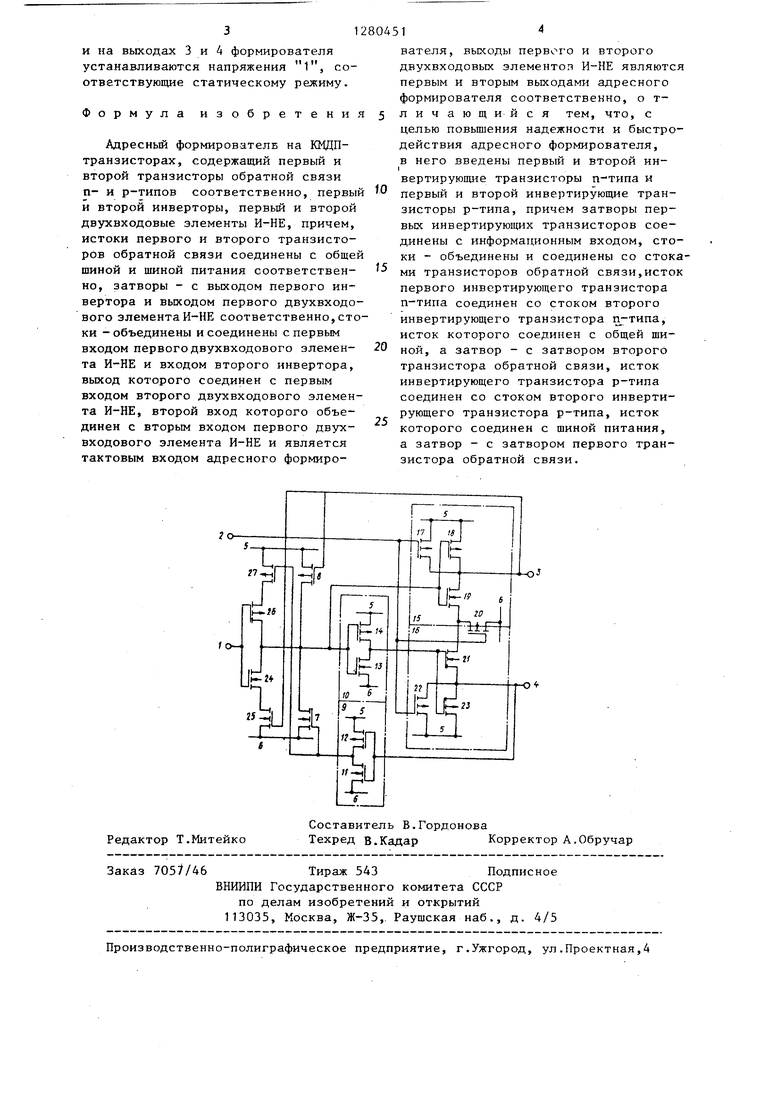

На чертеже дана схема предлагаемого адресного формирователя.

Устройство содержит информационный 1 и тактовый 2 входы, первый 3 и второй 4 выходы, шину питания 5 и общую тину 6, первый транзистор 7 обратной связи п-типа и второй транзистор 8 обратной связи р-типа, перньш 9 и второй 10 инверторы, вьшол- ненные по типовой схеме на транзисторах 11-14, первый 15 и второй 16 двухвходовые элементы И-НЕ, выполненные по типовой схеме на транзисторах 17-23, первый и второй инвертирующие транзисторы п-типа 24 и 25 соответственно, первый 26 и второй 27 инвертирующие транзисторы р-типа, причем истоки первого 7 и второго 8 транзисторов обратной связи соединены с общей шиной 6 и шиной питания 5 соответственно, затворы - с выходом первого инвертора 9, выходом первого элемента И-НЕ 15 и входом второго инвертора 10., выход которого соединен с первым входом второго элемента И-НЕ 16, второй вход которого объединен с вторым входом первого элемента И-НЕ и является тактовым входом 2, выходы первого 15 и второго 16 элементов И-НЕ являются первым 3 и вторым 4 выходами формирователи соответственно, затворы первьк инвертирующих транзисторов 24 и 26 соединены с информационным входом 1, стоки - объединены и соединены со стоками транзисторов обратной связи 7 и 8, исток первого инвертирующего транзистора п-типа 24 соединен со стоком второго инвертирующего транзистора п-типа 25, исток которого соединен с общей шиной 6, а затвор- с затвором второго транзисто ра обратной связи 8, исток первого инвер12

20

25

804312

тирующего транзистора р-типа 26 соединен со стоком второго инвертирующего транзистора р-типа 27, исток которого соединен с шиной питания 5,

5 а затвор - с затвором первого транзистора обратной связи 7.

Адресный формирователь работает следующим образом.

В статическом режиме на тактовом

W входе 2 поддерживается напряжение

О, а на информационном 1 может поддерживаться напряжение, соответствующее произвольной адресной информации (О либо 1). При этом транзистор

5 20 закрыт, а транзисторы 17 и 22 открыты, в результате чего на выходах

3и 4 устанавливаются напряжения,соответствующие 1, независимо от напряжения на информационном входе 1. В результате транзисторы обратной связи оказываются закрытыми, а вторые инвертирующие транзисторы 25 и 27 - открытыми.

В активном режиме на информационном входе 1 устанавливается напряжение, соответствующее адресной информации. Предположим, что н информационный вход 1 подается напряжение 1. При этом на входе и выходе второго инвертора 10 формируется напряжение О и 1 соответственно, В результате после подачи на тактовый вход 2 напряжения 1 на выходе

4формирователя формируется напряжение О (напряжение на выходе 3 остается равным 1). При этом переключается первый инвертор 9, на выходе которого формируется напряжение 1, что приводит к отпиранию транзистора обратной связи 7 и запиранию инвертирующего транзистора

27. Это позволяет запомнить адресный сигнал 1. Последующее инвертирование адресного сигнала,т.е.

45 подача О на вход 1, не изменяет напряжения на входе инвертора 10, так как закрыт инвертирующий тран- , зистор 27 и открыт транзистор обратной связи 7. Аналогично осуществляется прием и запоминание адресной информации, соответствующей О. В этом случае после подачи тактового сигнала на выходе 3 формируется напряжение О, отпирается транзистор

55 обратной связи 8 и запирается инвертирующий транзистор 25.

В режиме восстановления на тактовый вход 2 подается напряжение О

30

35

40

50

31280451

на выходах 3 и 4 формирователя вателя, станавливаются напряжения 1, сответствующие статическому режиму.

двухвхо первым формиро лича целью п действи в него вертиру первый зисторы вых инв динены ки - об ми тра первог п-типа инверт исток ной, а транзи инверт соедин рующег которо а затв зистор

Формула

зобретения 5

Адресный формирователи на КМДП- транзисторах, содержащий первый и второй транзисторы обратной связи п- и р-типов соответственно, первый и второй инверторы, первый и второй двухвходовые элементы И-НЕ, причем, истоки первого и второго транзисторов обратной связи соединены с общей шиной и шиной питания соответственно, затворы - с выходом первого инвертора и выходом первого двухвходо- вого элемента И-НЕ соответственно, стоки - объединены и соединены с первым входом первого двухвходового элемента И-НЕ и входом второго инвертора, выход которого соединен с первым входом второго двухвходового элемента И-НЕ, второй вход которого объединен с вторым входом первого двухвходового элемента И-НЕ и является тактовым входом адресного формироСоставитель В.Гордонова Редактор Т.Митейко Техред В.Кадар

Заказ о5//46Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,. Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

выходы первого и второго двухвходовых элементоп И-НЕ являются первым и вторым выходами адресного формирователя соответственно, о т- личающийся тем, что, с целью повышения надежности и быстродействия адресного формирователя, в него введены первый и второй ин- вертирующие транзисторы п-типа и первый и второй инвертирующие транзисторы р-типа, причем затворы первых инвертирующих транзисторов соединены с информационным входом, стоки - объединены и соединены со стоками транзисторов обратной связи,исток первого инвертирующего транзистора п-типа соединен со стоком второго инвертирующего транзистора п -типа, исток которого соединен с общей шиной, а затвор - с затвором второго транзистора обратной связи, исток инвертирующего транзистора р-типа соединен со стоком второго инвертирующего транзистора р-типа, исток которого соединен с шиной питания, а затвор - с затвором первого транзистора обратной связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Входной усилитель-формирователь с запоминанием информации | 1980 |

|

SU903970A1 |

| Функциональный коммутатор на КМДП-транзисторах | 1988 |

|

SU1506540A1 |

| Усилитель-формирователь для оперативного запоминающего устройства на КМДП транзисторах | 1981 |

|

SU999104A1 |

| Усилитель считывания на КМДП-транзисторах | 1986 |

|

SU1377910A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих, устройствах на КМДП-транзисторах для запоми-г нания адресных сигналов и формирования сигналов, поступающих на дешифраторы запоминающего устройства. Цель - повьппение надежности и быстродействия адресного формирователя. Адресный формирователь на КМДП-транзисторах содержит информационный и тактовый входы, первый и второй выходы, шину питания, общую шину, первый и второй транзисторы обратной связи п- и р-,типа соответственно | первый и второй инверторы,, первый и второй двухвходовые логические элементы И-НЕ с соответствующими связями и дополнительно содержит, первый к, второй инвертирующие транзисторы п-типа и первый и второй инвертирующие транзисторы р-типа с соответствующими связями. 1 ил. Ю

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кармазинский А.Н | |||

| Синтез принципиальных схем цифровых элементов на ЦДЛ-транзисторах | |||

| М.: Радио и связь, 1983, с | |||

| Топливник с глухим подом | 1918 |

|

SU141A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-30—Публикация

1985-08-26—Подача