00 00 4

Фив.1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения - повышение точности контроля.

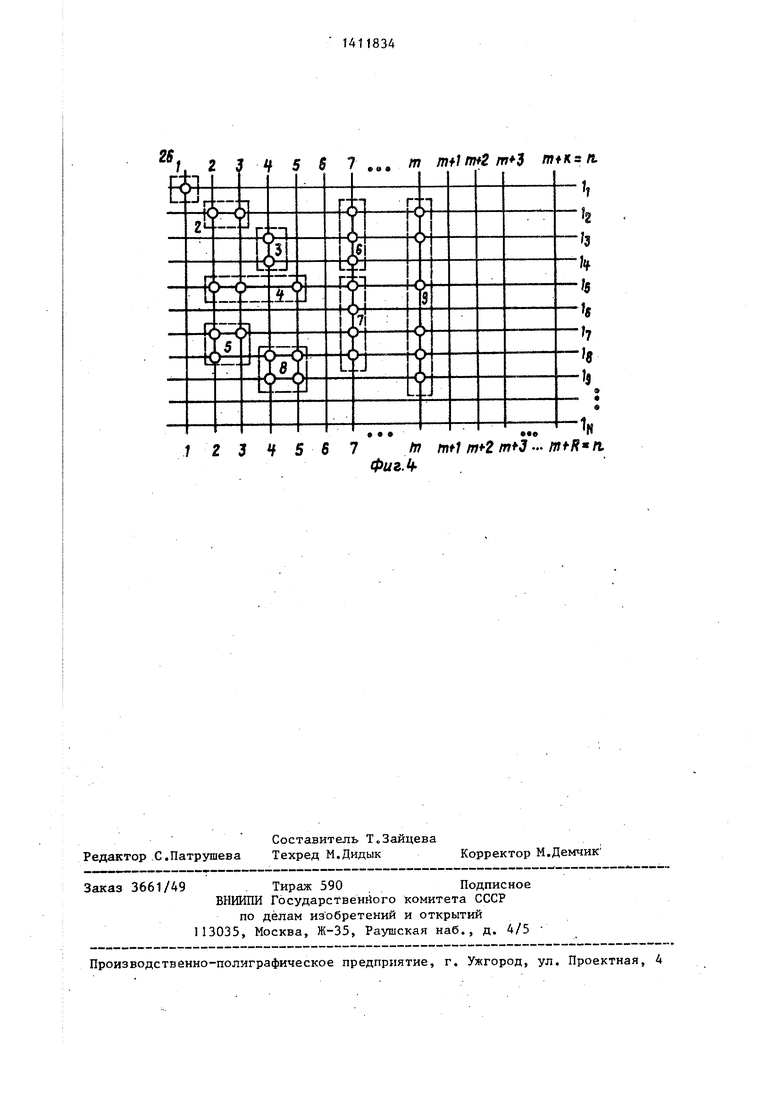

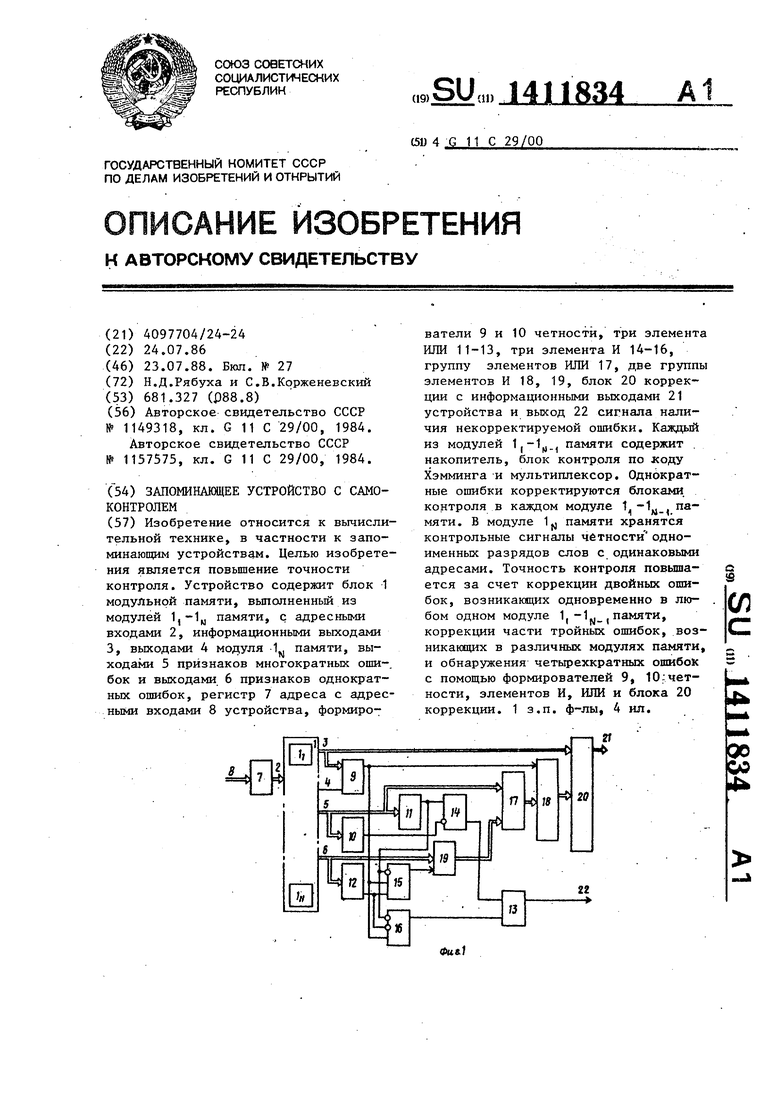

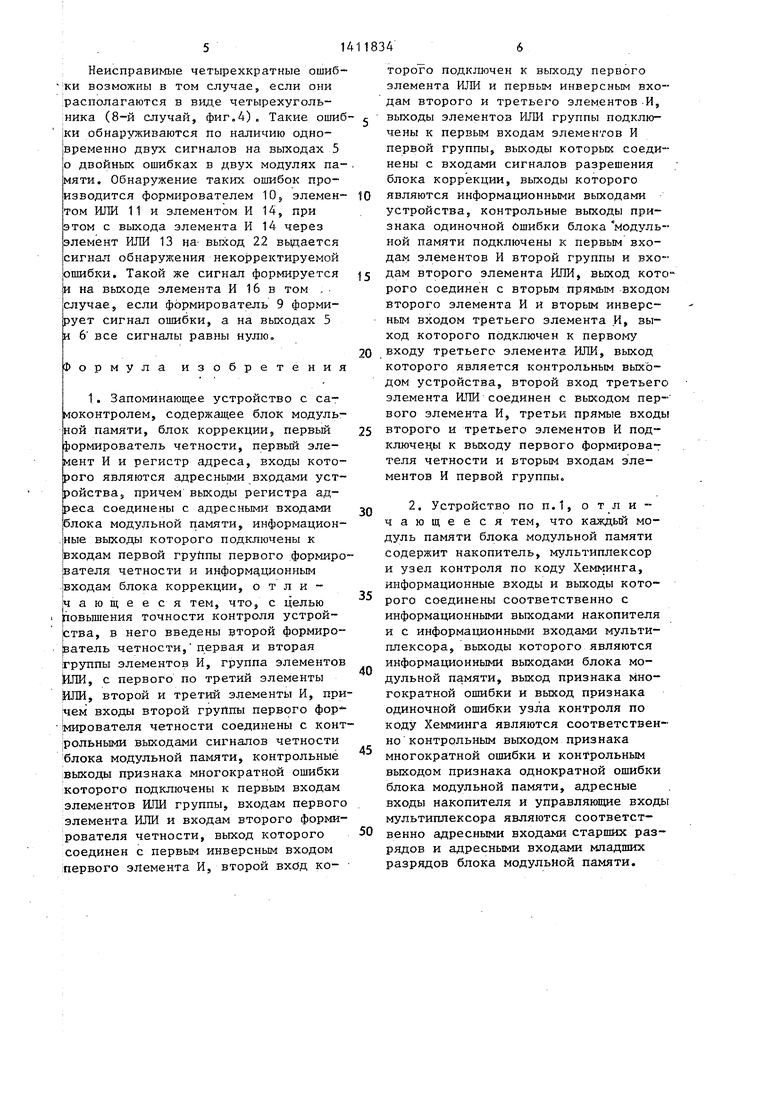

На фиг. 1 представлена функциональная схема предложенного устройства, на фиг. 2 - структурная схема блока модульной памяти, на фиг. 3 - функциональная схема наиболее предпочтительного варианта соединения элементов ИЛИ группы, элементов И первой группы и блока коррекции, на 1ФИГ. 4 - структура используемого корректирующего кода и принцип корре ции ошибок различной кратности, поясняющие работу устройства.

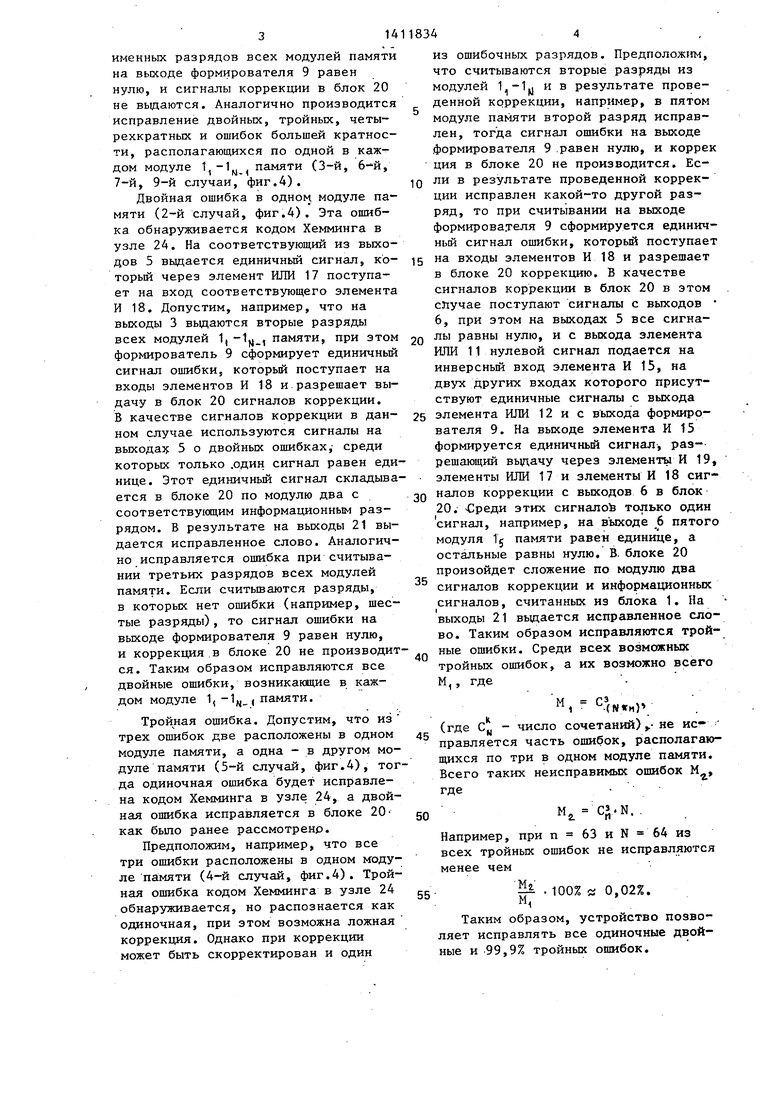

Устройство содержит (фиг.1) блок 1 модульной памяти, вьтолненньш из модулей 1( -1у памяти, с адресными входами 2, информационными выходами 3, выходами 4 контрольного модуля А памяти, выходами 5 признаков многократных ошибок и выходами 6 признаков однократных ошибок, регистр 7 адреса с адресными входами 8 устройства, первьй 9 и второй 10 формирователи четности, с первого по третий элементы ИЛИ 11-13, с первого по тре |тий элементы И 14-16, группу элементов ИЛИ 17, первзпо 18 и вторую 19 группы элементов И, блок 20 коррекции с информационными выходами 21 устройства.и выход 22 сигнала нали- чия некорректируемой ошибки. ; Каждый из модулей 1,-1,., памяти содержит (фиг.2) накопитель 23, узел 24 контроля по коду Хемминга и мультиплексор 25,

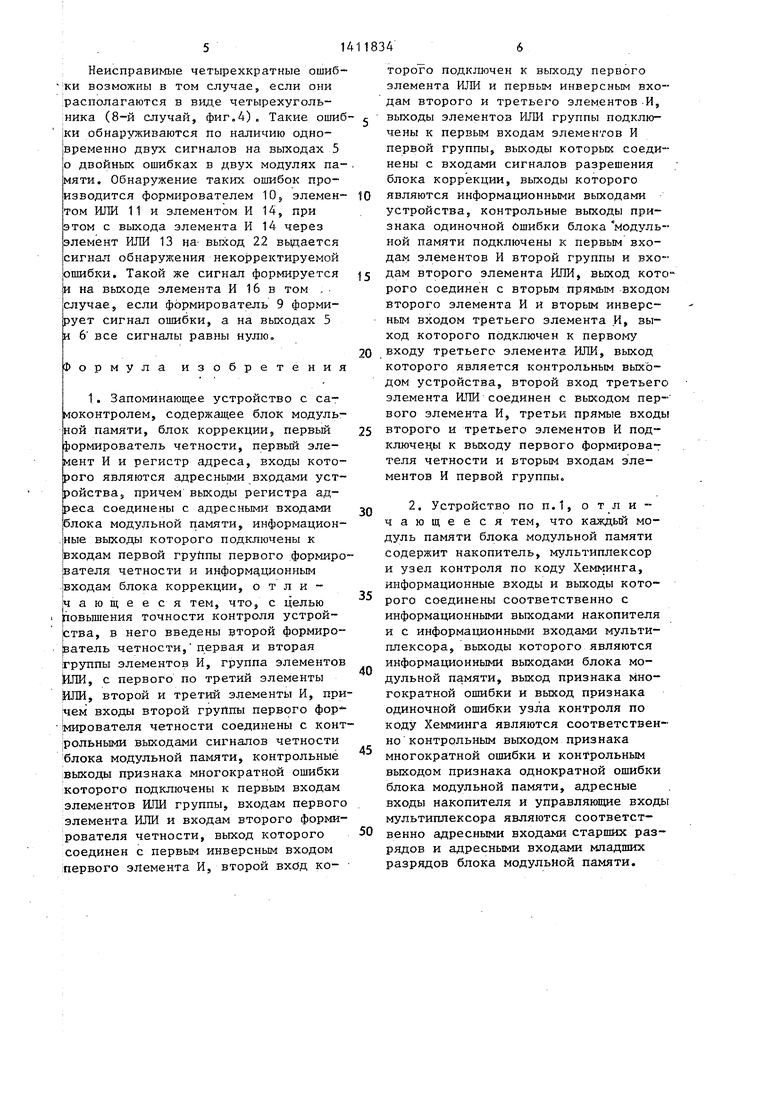

На фиг. 3 обозначены элементы 1ИЛИ. 17,.-17,, элементы И 18,-18 |и сумматоры 20,-21.,по модулю два в блоке 20 коррекции.

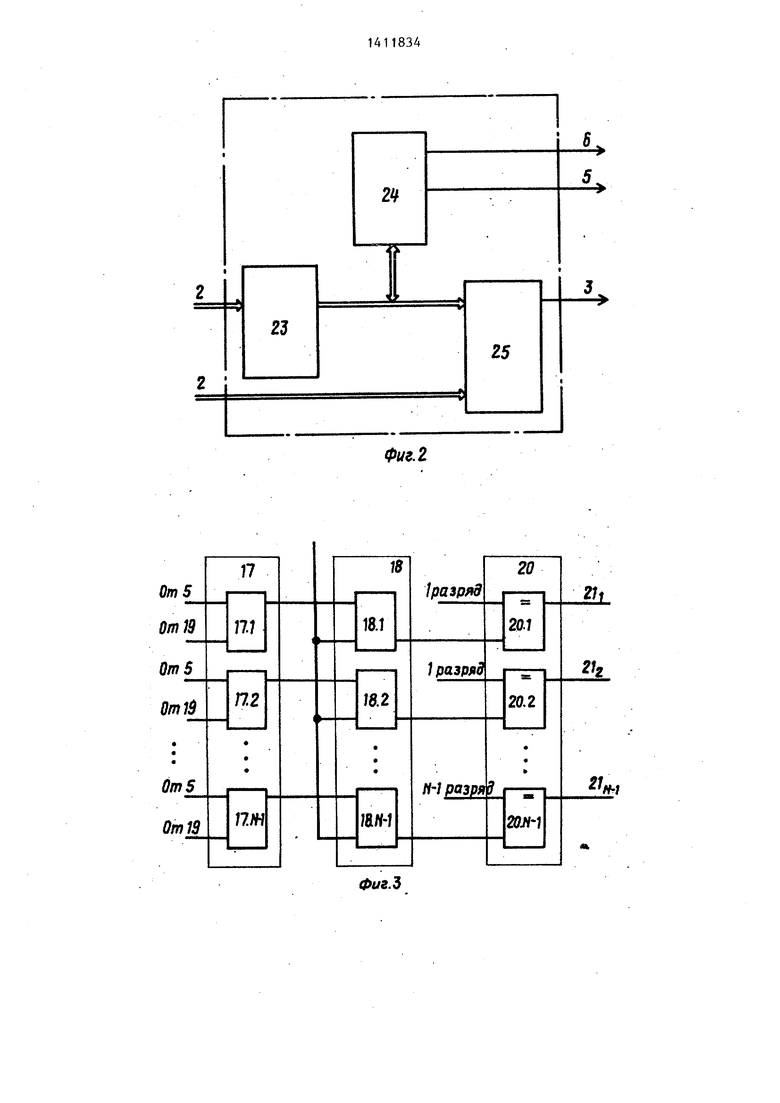

На фиг. 4 обозначены информационные разряды 26,-26, и контрольные разряды (где m - число Iинформационных разрядов, k - число контрольных разрядов слова) кода Хемминга, применяемого для контроля каждого из 1, -1J, j модулей памя ти, и показаны девять вариантов расположения ошибок в информационных разрядах блока 1 модульной памяти.

Устройство рабсЛ-ает следукицим об- jpa3OM.

. В накопителях 23 (фиг.2) модулей ;1 1„., памяти хранятся закодированные модифицированным кодом Хемминга

5

п разрядные слова (где п га + k). В модуле (фиг„1) памяти хранятся контрольные сигналы четности одно- именных разрядов слов с одинаковыми адресами модулей 1 ,-1| памяти.

На выходы 3 модулей 1,-1, (после возможной коррекции) выдаются выбранные одноименные разряды всех

Q модулей памяти. На выходы 4 выдает- , ся сигнал четности вьщанных на выходы 3 информационных разрядов. На выходы 5 вьдаются сигналы обнаружения двойной ошибки, на выходы 6 выдаются сигналы о проведенной коррекции одиночной ошибки в модулях 1,1iy - памяти.

При считывании в каждом модуле 1.-1.. из накопителя 23 считьшается

Q п-разрядное слово, которое проверяется кодом Хемминга в узле 24. При возникновении двойной ошибки производится ее обнаружение и формирование сигнала двойной ошибки. Этот сигнал

5 поступает на соответствующий выход 5. При.возникновении одиночной ошиб ки производится ее коррекция узлом 24 и формируется на вьрсоде 6 сигнал о том, что произведена коррекция.

Q На выходы 3 каждого модуля 1,.-1й. памяти из считанных п-разрядов в соответствии с младшими разрядами адреса выдается только один из информационных разрядов, откорректирован- . ньй кодом Хемминга. Таким образом,

при считывании на выходы 3 вьщается слово из N-1 разрядов, по которым , в формирователе 9 формируется сигнал четности, который складывается по модулю два с сигналом четности, по- ступаюпщм из модуля 1 через выход 4. Результат сложения в виде сигнала ошибки поступает на входы элементов |и 18 и разрешает вьздачу в блЬк 20 сигналов коррекции.

0

5

При возникновении ошибок в Модулях 1,1(j памяти могут быть следую щие ситуации, , Одиночная ошибка в одном модуле

0 памяти (1-й случай, фиг.4). Одиночная ошибка обнаруживается с помощью узла 24 и корректируется кодом Хем- минга. На соответствующей из выходов 6 выдается единичный сигнал, свиде5 тельствующий о том, что произведена коррекция одиночной ошибки в одном модуле памяти. Поскольку ошибка исправлена, то сигнал четности одноименных разрядов всех модулей памяти на выходе формирователя 9 равен нулю, и сигналы корреквдга в блок 20 не вьщаются. Аналогично производится исправление двойных, тройных, четырехкратных и ошибок большей кратности, располагающихся по одной в каждом модуле 1,-1 |у памяти (3-й, 6-й, 7-й, 9-й случаи, фиг,4).

Двойная ошибка в одном модуле памяти (2-й случай, фиг.4). Эта ошибка обнаруживается кодом Хемминга в узле 24. На соответствующий из выходов 5 выдается единичный сигнал, который через элемент ИЛИ 17 поступает на вход соответствующего элемента И 18. Допустим, например, что на выходы 3 выдаются вторые разряды всех модулей 1, -Ij.i памяти, при этом формирователь 9 сформирует единичньй сигнал ошибки, которьй поступает на входы элементов И 18 и разрешает выдачу в блок 20 сигналов коррекции. В качестве сигналов коррекции в данном случае используются сигналы на выходаз 5 о двойных ошибках,- среди которых только .один сигнал равен единице. Этот единичньй сигнал складывается в блоке 20 по модулю два с соответствукщим информационным разрядом. В результате на выходы 21 выдается исправленное слово. Аналогично исправляется ошибка при считывании третьих разрядов всех модулей памяти. Если считьшаются разряды, в которых нет ошибки (например, шестые разряды), то сигнал ошибки на выходе формирователя 9 равен нулю, и коррекция.в блоке 20 не производится. Таким образом исправляются все двойные ошибки, возникающие в каждом модуле 1, -1fj( памяти.

Тройная ошибка. Допустим, что из трех ошибок две расположены в одном модуле памяти, а одна - в другом модуле памяти (5-й случай, фиг,4), тогда одиночная ошибка будет исправлена кодом Хемминга в узле 24, а двойная ошибка исправляется в блоке 20- как быпо ранее рассмотренр.

Предположим, например, что все три ошибки расположены в одном модуле памяти (4-й случай, фиг.4). Тройная ошибка кодом Хемминга в узле 24 обнаруживается, но распознается как одиночная, при этом возможна ложная коррекция. Однако при коррекции может быть скорректирован и один

из ошибочных разрядов. Предположим, что считываются вторые разряды из модулей 1,1ц и в результате проведенной коррекции, например, в пятом модуле памяти второй разряд исправлен, тогда сигнал ошибки на выходе формирователя 9 .равен нулю, и коррек ция в блоке 20 не производится. Если в результате проведенной коррекции исправлен какой-то другой разряд, то при считывании на выходе формирователя 9 сформируется единичньй сигнал ошибки, которьй поступает

на входы элементов И 18 и разрешает в блоке 20 коррекцию. В качестве сигналов коррекции в блок 20 в этом случае поступают сигналы с выходов 6, при этом на выходах 5 все сигналы равны нулю, и с выхода элемента ИЛИ 11 нулевой сигнал подается на инверсньй вход элемента И 15, на двух других входах которого присутствуют единичные сигналы с выхода

элемента ИЛИ 12 и с выхода формирователя 9. На выходе элемента И 15 формируется единичньй сигнал, разрешающий вь1дачу через элементы И 19, элементы ИЛИ 17 и элементы И 18 сигналов коррекции с выходов 6 в блок 20. Среди этих сигналов только один сигнал, например, на в ыходе 6 пятого модуля Tg памяти равен единице, а остальные равны нулю. В. блоке 20 произойдет сложение по модулю два сигналов коррекции и информационных сигналов, считанных из блока 1, На выходы 21 вьщается исправленное слово. Таким образом исправляются тройные ошибки. Среди всех возможных тройных ошибок, а их возможно всего

М

1

где

М «

(N«M)

(где Су - число сочетаний),.- не не- правляется часть ошибок, располагающихся по три в одном модуле памяти. Всего таких неисправимых ошибок М,

где.

50

М,

C3.N.

Например, при п 63 и N 64 из всех тройных ошибок не исправляются менее чем

Mi

М,

100% с 0,02%.

Таким образом, устройство позволяет исправлять все одиночные двойные и 99,9% тройных ошибок.

Неисправимые четырехкратные ошиб ки возможны в том случае, если они располагаются в виде четырехугольника (8-й случай, фиг.4). Такие ошиб- |ки обнаруживаются по наличию одновременно двух сигналов на выходах 5

о двойных ошибках в двух модулях памяти. Обнаружение таких ошибок производится формирователем 10 элементом ИЛИ 11 и элементом И 14, при этом с выхода элемента И 14 через элемент ИЛИ 13 на- выход 22 вьщается сигнал обнаружения некорректируемой ошибки. Такой же сигнал формируется и на выходе элемента И 16 в том . случае, если формирователь 9 формирует сигнал ошибки, а на выходах 5 и 6 все сигналы равны нулю.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее блок модульной памяти, блок коррекции, первьй 5)ормирователь четности, первый элемент И и регистр адреса, входы которого являются адресньми входами устройства, причем выходы регистра адреса соединены с адресными входами блока модульной памяти, информацион- |ные выходы которого подключены к рходам первой группы первого формиро- вателя четности и информ дионным входам блока коррекции, о т л и - Чающееся тем, что, с целью ровышения точности контроля устрой- |ства, в него введены второй формирователь четности, первая и вторая |группы элементов И, группа элементов ИЛИ, с первого по третий элементы ШШ, второй и третий элементы И, при- чем входы второй группы первого форИирователя четности соединены с конт- рольными выходами сигналов четности блока модульной памяти, контрольные ;выходы признака многократной ошибки которого подключены к первым входам элементов ИЛИ группы, входам первого элемента ИЛИ и входам второго формирователя четности, выход которого соединен с первым инверсным входом первого элемента И, второй вход ко-

торого подключен к выходу первого элемента ИЛИ и первым инверсным входам второго и третьего элементов И, выходы элементов ИЛИ группы подключены к первым входам элементов И первой группы, выходы которых соединены с входами сигналов разрешения блока коррекции, выходы которого

являются информационными выходами устройства, контрольные выходы признака одиночной Ошибки блока модульной памяти подключены к первым входам элементов И второй группы и входам второго элемента ИЛИ, выход которого соединен с вторым прямым входом бторого элемента И и вторым инверсным входом третьего элемента И, выход которого подключен к первому

входу третьего элемента ИЛИ, выход которого является контрольным выходом устройства, второй вход третьего элемента ИЛИ соединен с выходом пер- вого элемента И, третьи прямые входы

второго и третьего элементов И под- ключецы к выходу первого формирователя четности и вторым входам элементов И первой группы.

2. Устройство по п.1, о т л и - чающееся тем, что каждый модуль памяти блока модульной памяти содержит накопитель, мультиплексор и узел контроля по коду Хемминга, информационные входы и выходы которого соединены соответственно с информационными выходами накопителя и с информационными входами мультиплексора, выходы которого являются информационными выходами блока модульной памяти, выход признака многократной ошибки и выход признака одиночной ошибки узла контроля по коду Хемминга являются соответственно контрольным выходом признака многократной ошибки, и контрольным выходом признака однократной ошибки блока модульной памяти, адресные входы накопителя и управляющие входы мультиплексора являются соответст- венно адресными входами старших разрядов и адресными входами младших разрядов блока модульной памяти.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство | 1990 |

|

SU1794261A3 |

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1474746A2 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Оперативное запоминающее устройство с коррекцией информации | 1983 |

|

SU1111206A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повышение точности контроля. Устройство содержит блок 1 модульной памяти, вьшолненньш из модулей I,-IM памяти, с адресными входами 2, информационными выходами 3, выходами 4 модуля 1 памяти, выходами 5 признаков многократных оши-. бок и выходами 6 признаков однократных ошибок, регистр 7 адреса с адресными входами 8 устройства, формирователи 9 и 10 четности, три элемента ИЛИ 11-13, три элемента И 14-16, группу элементов ИЛИ 17, две группы элементов И 18, 19, блок 20 коррекции с информащ онными выходами 21 устройства и выход 22 сигнала наличия некорректируемой ошибки. Каждый из модулей 1,1ц,., памяти содержит . накопитель, блок контроля по ходу Хэмминга и мультиплексор. Однократные ошибки корректируются блоками, контроля в каждом модуле 1 м- п мяти. В модуле 1 памяти хранятся контрольные сигналы чбтности одноименных разрядов слов с одинаковыми адресами. Точность контроля повьша- ется за счет коррекции двойных ошибок, возникающих одновременно в любом одном модуле 1,-1 памяти, коррекции части тройных ошибок, возникающих в различных модулях памяти, и обнаружения четырехкратных ошибок с помощью формирователей 9, 10:четности, элементов И, ИЛИ и блока 20 коррекции. 1 з.п. ф-лы, 4 ил. а S (Л с

От 5

тялят

ОгпЮ

От$

От 13

«

От 5

«и

От 19

Фиг.Ъ

2S

1 г 34 5 S ,,/ m ;w2/n 3 nttKsfi

123 567/ mti т К Чг

фигЛ

3

h

b

Jj

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-23—Публикация

1986-07-24—Подача