1. 130

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, выполненным из интегральных микросхем памяти,

Целью изобретения является повыше- ние точности контроля устройства.

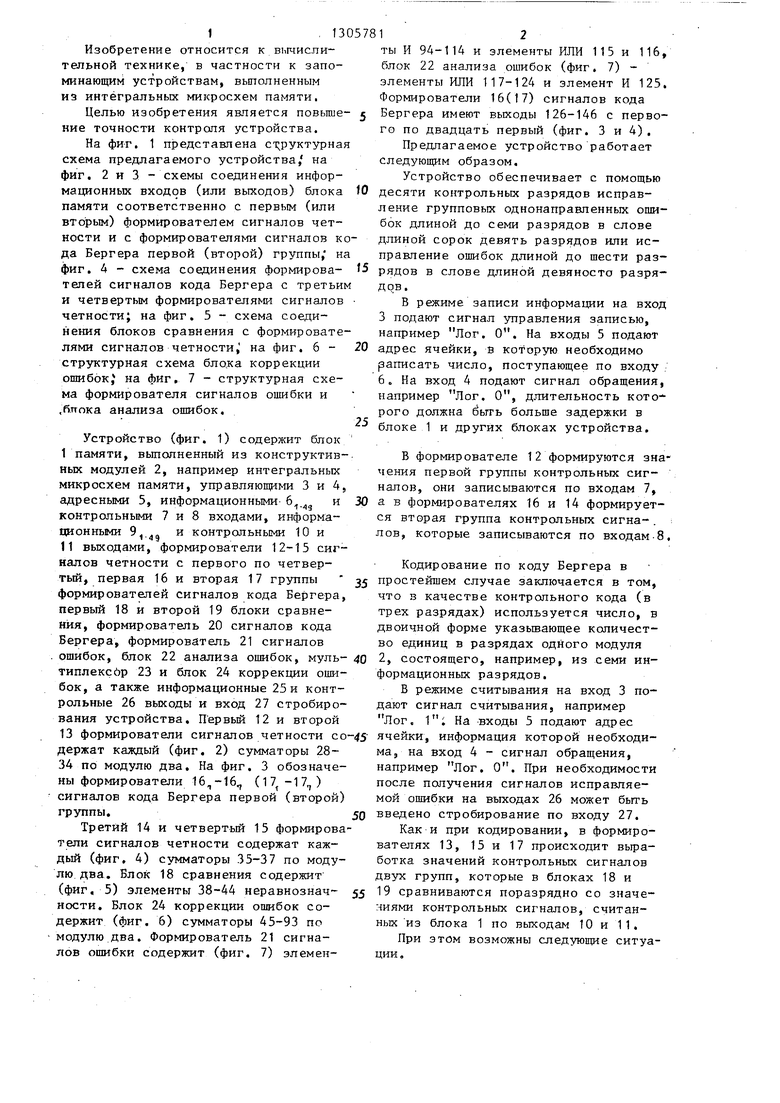

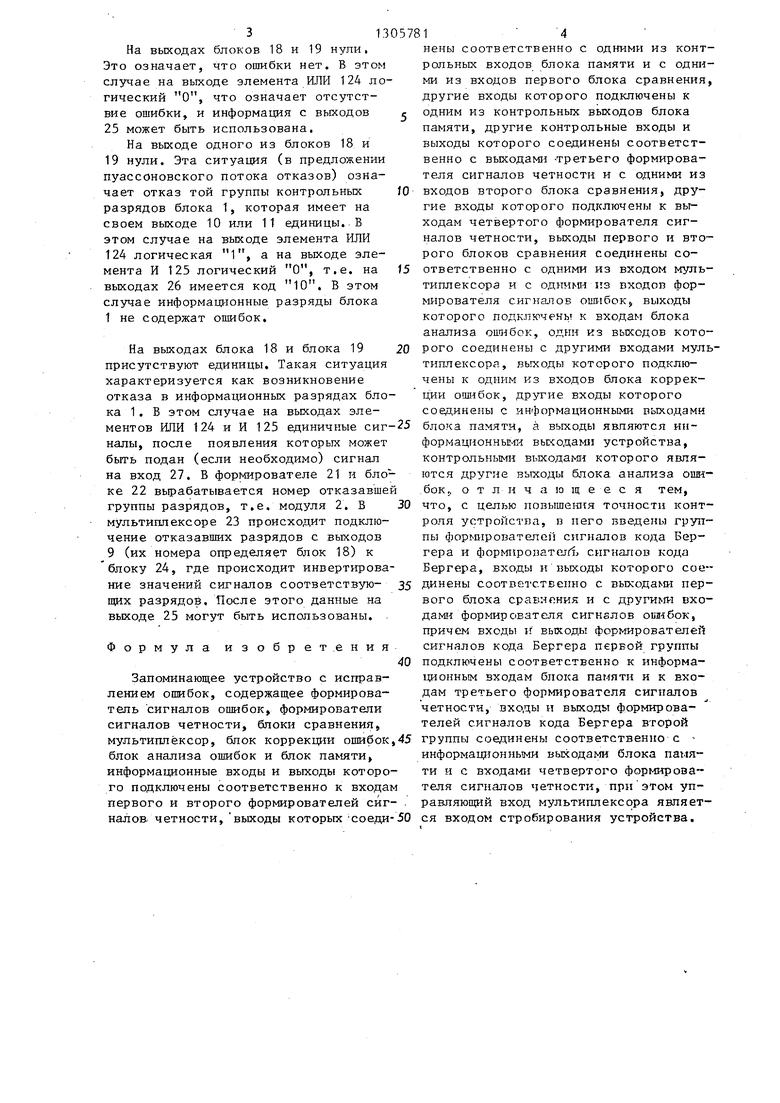

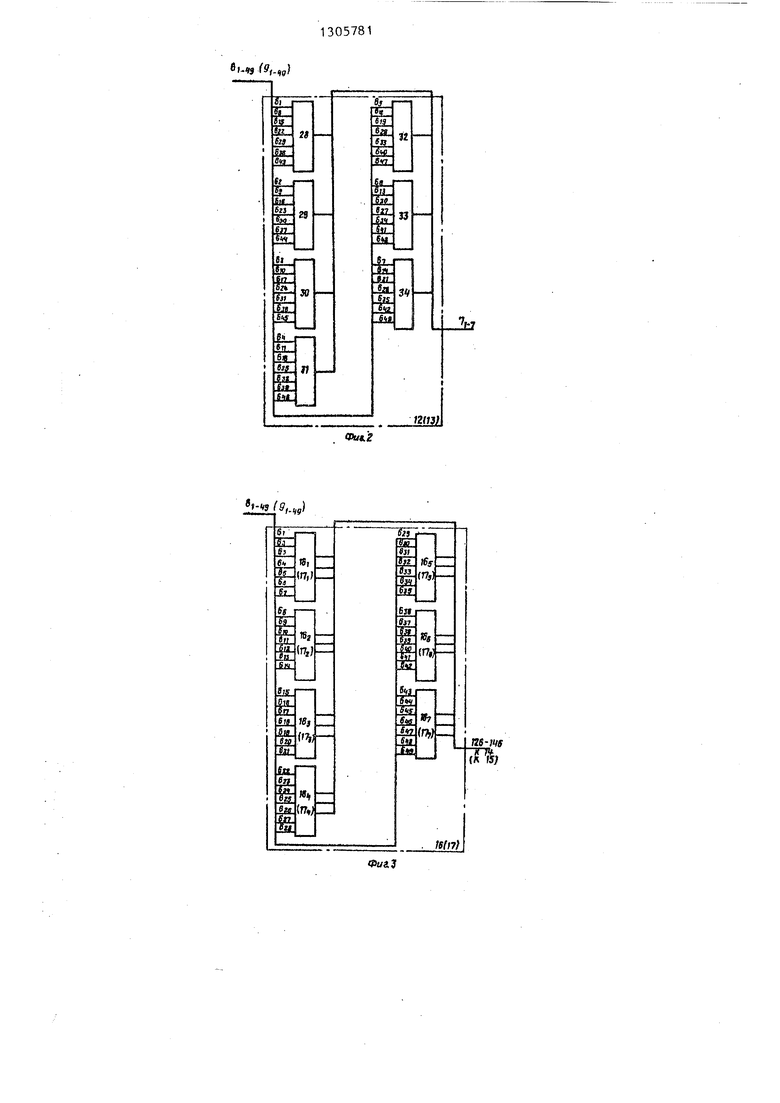

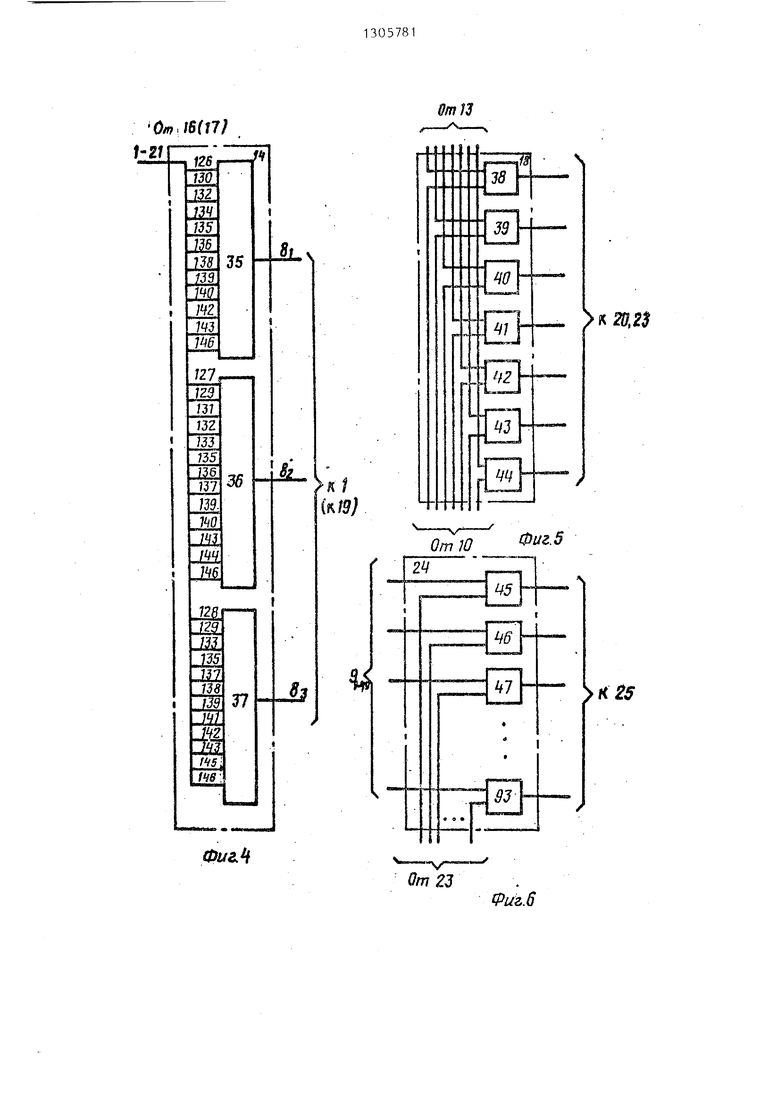

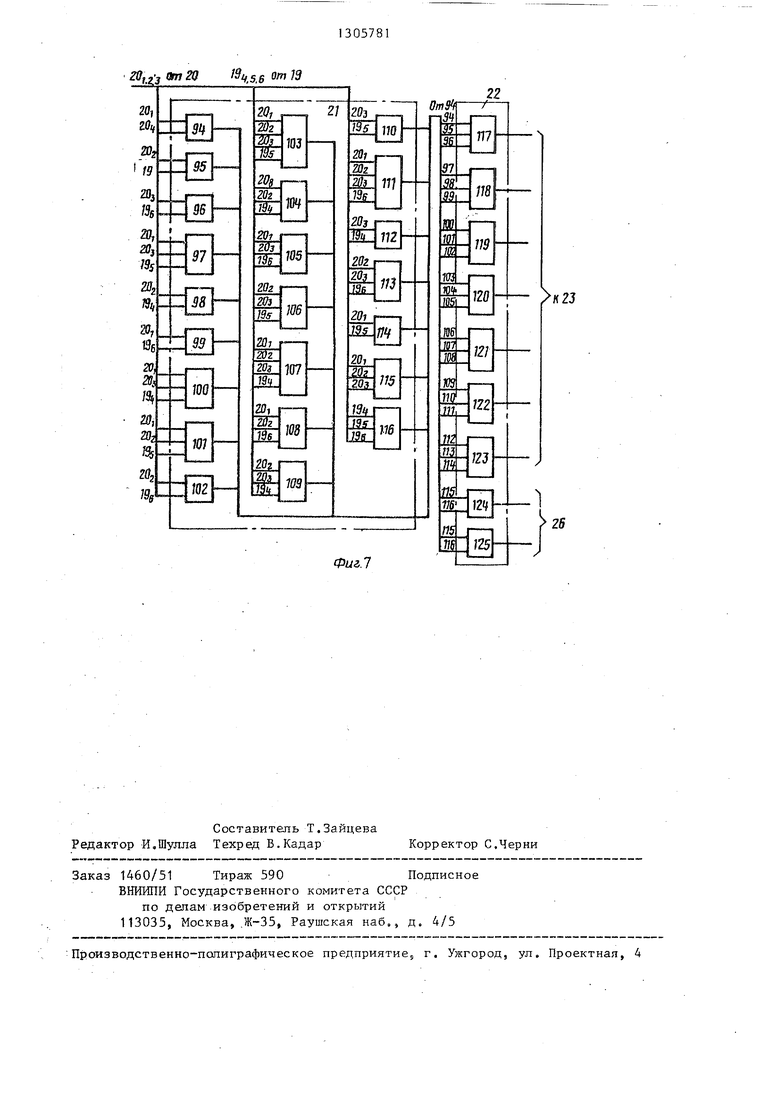

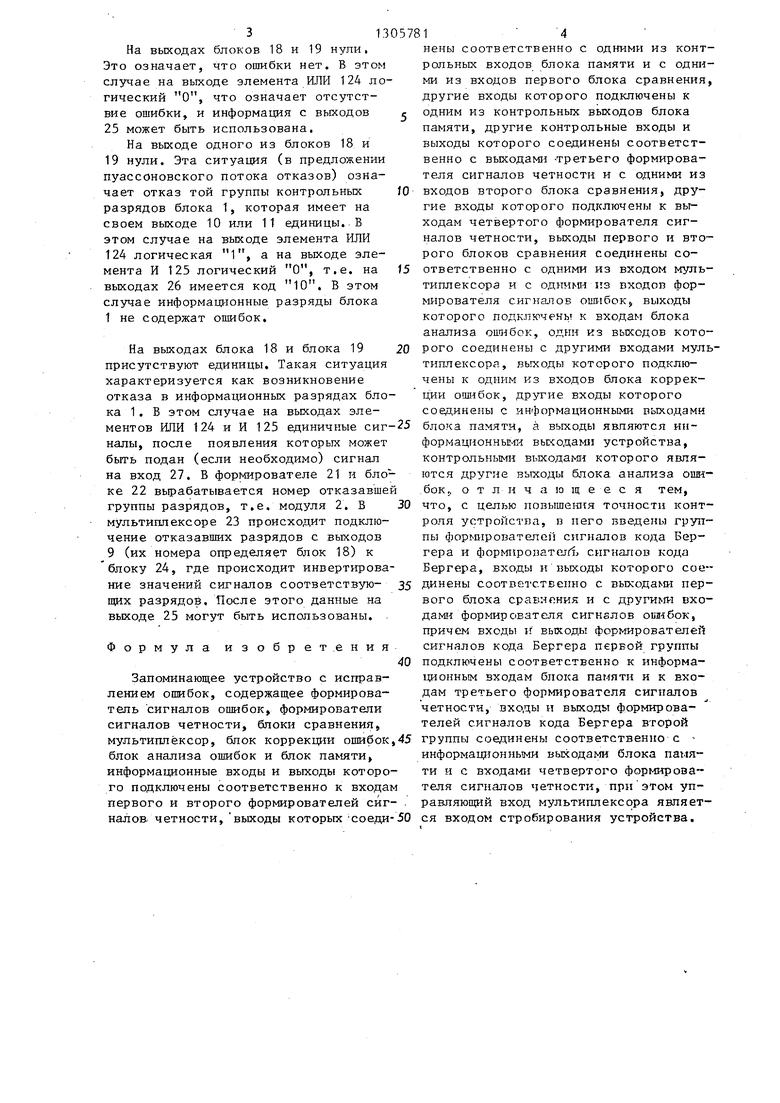

На фиг. 1 представлена ст руктурная схема предлагаемого устройства/ на фиг. 2 и 3 - схемы соединения информационных входов (или выходов) блока памяти соответственно с первым (или вторым) формирователем сигналов четности и с формирователями сигналов кода Бергера первой (второй) группы, на фиг. 4 - схема соединения формирова- талей сигналов кода Бергера с третьим и четвертым формирователями сигналов четностиJ на фиг. 5 - схема соединения блоков сравнения с формирователями сигналов четности, на фиг. 6 - структурная схема бло.ка коррекции ошибок, на фиг, 7 - структурная схема формирователя сигналов ошибки и

.Лттока анализа ошибок.

Устройство (фиг. 1) содержит блок

Iпамяти, вьшолненный из конструктивных модулей 2, например интегральных микросхем памяти, управляющими 3 и 4, адресными 5, информационными- 6, и контрольными 7 и 8 входами, информа- ционньми 9. и контрольными 10 и

IIвыходами, формирователи 12-15 сигналов четности с первого по четвертый, первая 16 и вторая 17 группы формирователей сигналов кода Бергера, первый 18 и второй 19 блоки сравнения, формирователь 20 сигналов кода Бергера, формирователь 21 сигналов ошибок, блок 22 анализа ошибок, муль- типлексбр 23 и блок 24 коррекции ошибок, а также информационные 25 и контрольные 26 выходы и вход 27 стробиро- вания устройства, П ервьй 12 и второй

13 формирователи сигналов четности со держат каждый (фиг, 2) сумматоры 28- 34 по модулю два. На фиг. 3 обозначены формирователи () сигналов кода Бергера первой (второй) группы,

Третий 14 и четвертый 15 формирователи сигналов четности содержат каждый (фиг, 4) сзтматоры 35-37 по модулю два. Блок 18 сравнения содержит (фиг, 5) элементы 38-44 неравнознач- ности. Блок 24 коррекции ошибок содержит (фиг. 6) сумматоры 45-93 по модулю два. Формирователь 21 сигналов ошибки содержит (фиг, 7) элемен12

ты И 94-114 и элементы ИЛИ 115 и 116, блок 22 анализа ошибок (фиг. 7) - элементы ИЛИ 117-124 и элемент И 125 Формирователи 16(17) сигналов кода Бергера имеют выходы 126-146 с первого по двадцать первый (фиг. 3 и 4),

Предлагаемое устройство работает следующим образом.

Устройство обеспечивает с помощью десяти контрольных разрядов исправление групповых однонаправленных ошибок длиной до семи разрядов в слове длиной сорок девять разрядов или исправление ошибок длиной до шести разрядов в слове длиной девяносто разрядов.

В режиме записи информации на вход 3 лодают сигнал управления записью, например Лог. О. На входы 5 подают адрес ячейки, в которую необходимо (Записать число, поступающее по входу 6. На вход 4 подают сигнал обращения, например Лог. О, длительность которого должна dbn-b больше задержки в блоке 1 и других блоках устройства,

В формирователе 12 формируются зна чения первой группы контрольных сиг- нало13, они записываются по входам 7, а в формирователях 16 и 14 формируется вторая группа контрольных сигна- . лов, которые записываются по входам-8

Кодирование по коду Бергера в простейшем случае заключается в том, что в качестве контрольного кода (в трех разрядах) используется число, в двоичной форме указьшающее количество единиц в разрядах одного модуля 2, состоящего, например, из семи ин- формационньк разрядов.

В режиме считывания на вход 3 подают сигнал считывания, например Лог. На -входы 5 подают адрес ячейки, информация которой необходима, на вход 4 - сигнал обращения, например Лог, О, При необходимости после получения сигналов исправляемой ошибки на выходах 26 может быть введено стробирование по входу 27.

Как и при кодировании, в формирователях 13, 15 и 17 происходит выработка значений контрольных сигналов двух групп, которые в блоках 18 и 19 сравниваются поразрядно со значениями контрольных сигналов, считанных из блока 1 по выходам 10 и 11.

При этом возможны следующие ситуации.

На выходах блоков 18 и 19 нули, Это означает, что ошибки нет. В этом случае на выходе элемента ИЛИ 124 ло 0

что означает отсутствие ошибки, и информация с выходов 25 может быть использована.

На выходе одного из блоков 18 и 19 нули. Эта ситуация (в предложении пуассоновского потока отказов) означает отказ той группы контрольных разрядов блока 1, которая имеет на своем выходе 10 или 11 единицы. В этом случае на выходе элемента ИЛИ 124 логическая 1, а на выходе элемента И 125 логический О, т.е. на выходах 26 имеется код 10. В этом случае информационные разряды блока 1 не содержат ошибок.

20

йены соответственно с одними из контрольных входов блока памяти и с одними из входов первого блока сравнения, другие входы которого подключены к одним из контрольных выходов блока памяти, другие контрольные входы и выходы которого соединены соответственно с выходами -третьего формирователя сигналов четности и с одними из входов второго блока сравнения, другие входы которого подключены к выходам четвертого формирователя сигналов четности, выходы первого и второго блоков сравнения соединены соответственно с одними из входом мультиплексора и с из входов формирователя сигналов ошибок, выходы которого подключень к входам блока анализа ошибок, одни из выходов которого соединены с другими входами мультиплексора, выходы которого подключены к одним из входов блока коррекции onni6oK, другие входы которого соединены с информационны ш выходами

На выходах блока 18 и блока 19 присутствуют единицы. Такая ситуация характеризуется как возникновение отказа в информационных разрядах блока 1 . В этом случае на выходах элементов ИЛИ 124 и И 125 единичные сиг-25 блока памяти, а выходы являются ин- налы, после появления которых может формационны я- выходами устройства, быть подан (если необходимо) сигнал на вход 27. В формирователе 21 и блоке 22 вьграбатывается номер отказавшей группы разрядов, т.е. модуля 2. В 30 что, с целью повышения точности конт- мультиплексоре 23 происходит подклю- роля устройства, п пего введены груп чение отказавших разрядов с выходов 9 (их номера определяет блок 18) к блоку 24, где происходит инвертироваконтрольными выходами которого являются другие выходы блока анализа ошибок,, отличающееся тем,

пы форьшрователей сигналов кода Бергера и форм11ровател1 сигналов кода Бергера, входы и выходы которого сое-

ние значений сигналов соответствующих разрядов. После этого данные на выходе 25 могут быть использованы.

Формула изобретения

40 подключены соответственно к информационным входам блока памяти и к входам третьего формирователя сигналов четности, входы и выходы формирователей сигналов кода Бергера второй

Запоминающее устройство с исправлением ошибок, содержащее формирова- тепь сигналов ошибок, формирователи сигналов четности, блоки сравнения, мультиплексор, блок коррекции ошибок,45 группы соединены соответственно с - блок анализа ошибок и блок памяти,информационными выходами блока памяинформационные входы и выходы которо- ти и с входами четвертого формирова™ го подключены соответственно к входам теля сигналов четности, при этом уп- первого и второго формирователей сиг- . равляющий вход мультиплексора явпяет- налон- четности, выходы которых соеди-ЗО ся входом стробирования устройства.

5

0

йены соответственно с одними из контрольных входов блока памяти и с одними из входов первого блока сравнения, другие входы которого подключены к одним из контрольных выходов блока памяти, другие контрольные входы и выходы которого соединены соответственно с выходами -третьего формирователя сигналов четности и с одними из входов второго блока сравнения, другие входы которого подключены к выходам четвертого формирователя сигналов четности, выходы первого и второго блоков сравнения соединены соответственно с одними из входом мультиплексора и с из входов формирователя сигналов ошибок, выходы которого подключень к входам блока анализа ошибок, одни из выходов которого соединены с другими входами мультиплексора, выходы которого подключены к одним из входов блока коррекции onni6oK, другие входы которого соединены с информационны ш выходами

5 блока памяти, а выходы являются ин- формационны я- выходами устройства, 0 что, с целью повышения точности конт- роля устройства, п пего введены груп

блока памяти, а выходы являются ин- формационны я- выходами устройства, что, с целью повышения точности конт- роля устройства, п пего введены груп

контрольными выходами которого являются другие выходы блока анализа ошибок,, отличающееся тем,

блока памяти, а выходы являются ин- формационны я- выходами устройства, что, с целью повышения точности конт- роля устройства, п пего введены груп

пы форьшрователей сигналов кода Бергера и форм11ровател1 сигналов кода Бергера, входы и выходы которого сое-

динены соответс-твепно с выходами первого блока сравнг.ния и с другими входами формирователя сигналов ошибок, причем входы и выходы формирователей сигналов кода Бергера первой группы

подключены соответственно к информационным входам блока памяти и к входам третьего формирователя сигналов четности, входы и выходы формирователей сигналов кода Бергера второй

группы соединены соответственно с - информационными выходами блока памяв (.ад/,.,, J

«ti чд

От 16(17 J

I ll

IZS

;

Ж

Ж

35

ILN

т

т

У К 20.23

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с обнаружением и исправлением модульных ошибок | 1985 |

|

SU1304080A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1986 |

|

SU1322377A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1115107A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1411834A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

Изобретение относится к вычислительной технике, в частности к за- поминаюпрм устройствам, выполненным из интегральных микросхем памяти. Целью изобретения является повышение точности контроля устройства. Устройство содержит блок 1 памяти, выполненный из конструктивных модулей 2 памяти, например из интегральных gi-чэ микросхем памяти, четыре формирователя 12-15 сигналов четности, две группы формирователей 16 и 17 сигналов кода Бергера, два блока 18 и 19 сравнения, формирователь 20 сигналов кода Бергера, формирователь 21 сигналов ошибок, блок 22 анализа ошибок, мультиплексор 23 и блок 24 коррекции ошибок. В устройстве выполняется самоконтроль путем формирования контрольного кода при записи и считывании информации с помощью форьшрова- телей сигналов четности и форм фова- телей сигналов кода Бергера и сравнение этих контрольных кодов в блоках сравнения при считывании информации. Формирователь сигналов ошибок и блок анализа ошибок служат для определения номера отказывающего модуля памяти. В блоке коррекции оишбок выпатт- няется исправление групповых однонаправленных опгабок длино54 до семи разрядов в модуле памяти. 7 ил. 25 с S СЛ iraii ОАЭ О ОТ « 00 П

1Й

(л/5;

т.

т

ш

126

129

Ш

От Ю

2

б

37

Фиг.Ц

7

yK2ff

4

дд

От 23

Фиг.6

Составитель Т.Зайцева Редактор И.Шулла Техред В.Кадар

Заказ 1460/51Тираж 590Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,.Ж-35, Раушская наб., д. 4/5

:Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Корректор С.Черни

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| IBM J | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| РУЧКА С РЕЗЕРВУАРОМ ДЛЯ ЧЕРНИЛ | 1922 |

|

SU402A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-30—Подача