и является первым входом анализатора кодовых комбинаций , вторым входом которого является прямой вход третьего элемента ЗАПРЕТ, объединенный с первым входом четвертого элемента И, к второму входу которого, а также к инверсным входам второго и третьего элементов ЗАПРЕТ и второму входу пятого элемента И подключен выход третьего элемента ИЛИ, входами которого являются соответственно четвертый.

пятьй или шестой входы анализатора кодовых комбинаций, третьим входом которого является второй вход шестого элемента И, при этом выходы генератора синхроимпульсов, первого элемента И, первого элемента ИЛИ, второго элемента И и четвертого элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым и пятым выходами анализатора кодовых комбинаций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1984 |

|

SU1246380A1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| Декодер | 1979 |

|

SU860330A1 |

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

1. УСТРОЙСТВО ДЛЯ МАЖОРИ-.. ТАРНОГО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ КОДОВ ПРИ ТРЕХКРАТНОМ ПОВТОРЕНИИ КОМБИНАЦИИ по авт. св. № 677,123, отличающееся тем, что, с целью повьшения достоверности, введен анализатор кодовых комбинаций, к первому входу которого и первому дополнительному входу мажоритарного элемента подключен выход декодера, к синхронизирующему входу которого подключен первый выход анализатора кодовых ко бинаций, к второму входу которого подключен соотвествующий выход буферного блока памяти, а второй, третий, четвертый и пятый выходы анализатора кодовых комбинаций подключены соответственно к второму дополнительному входу мажоритарного элемента и первому, второму и третьему входам буферного блока памяти, при этом дополнительный выход мажоритарного.элемента и выходы блока памяти кодовых комбинаций результатов декодирования подключены соответственно к третьему, четвертому, пятому и шестому входам анализатора кодовьпс комбинаций. 2. Устройство по п.1, о т л и чающееся тем, что анализатор кодовых комбинаций содержит два счетчика, триггер, четыре элемента ЗАПРЕТ, шесть элементов И, четыре элемента ИЛИ и генератор синхроимпуль- . сов, выход которого подключен к входу первого счетчика, первому прямому входу первого элемента ЗАПРЕТ и первым входам первого и второго элементов И, при этом выход старшего разряда первого счетчика подключен к входу второго счетчика и единичному входу триггера, выход которого подключен к вторым входам первого и второго элементов И и второму прямому входу первого элемента ЗАЛРЕТ, к инверсному входу которого и третьему входу первого элемента И подключен первый выход второго счетчика, второй выход которого подключен к третьему прямому входу первого элемента ЗАПРЕТ и четвертому входу первого элемента И, причем выходы разрядов первого счегчика подключены к входам третьего элемента И. выход .КОТОРОГО подключен к нулевому входу триггера, а выходы второго элемента ЗАПРЕТ и четвертого элемента И подключены к сл первому входу первого элемента ИЛИ, vi выходы третьего элемента ЗАПРЕТ и vi пятого элемента И через второй элемент ИЛИ подключены к прямому входу четвертого элемента ЗАЛРЕТ, к инверсному входу которого и первому входу шестого элемента И подключен выход первого элемента ЗАПРЕТ, а выходы :четБертого элемента ЗАЛРЕТ и шестого элемента И подключены к входам четвертого элемента ИЛИ, при этом прямой вход второго элемента ЗАЛРЕТ объединен с первым входом пятого элемента И

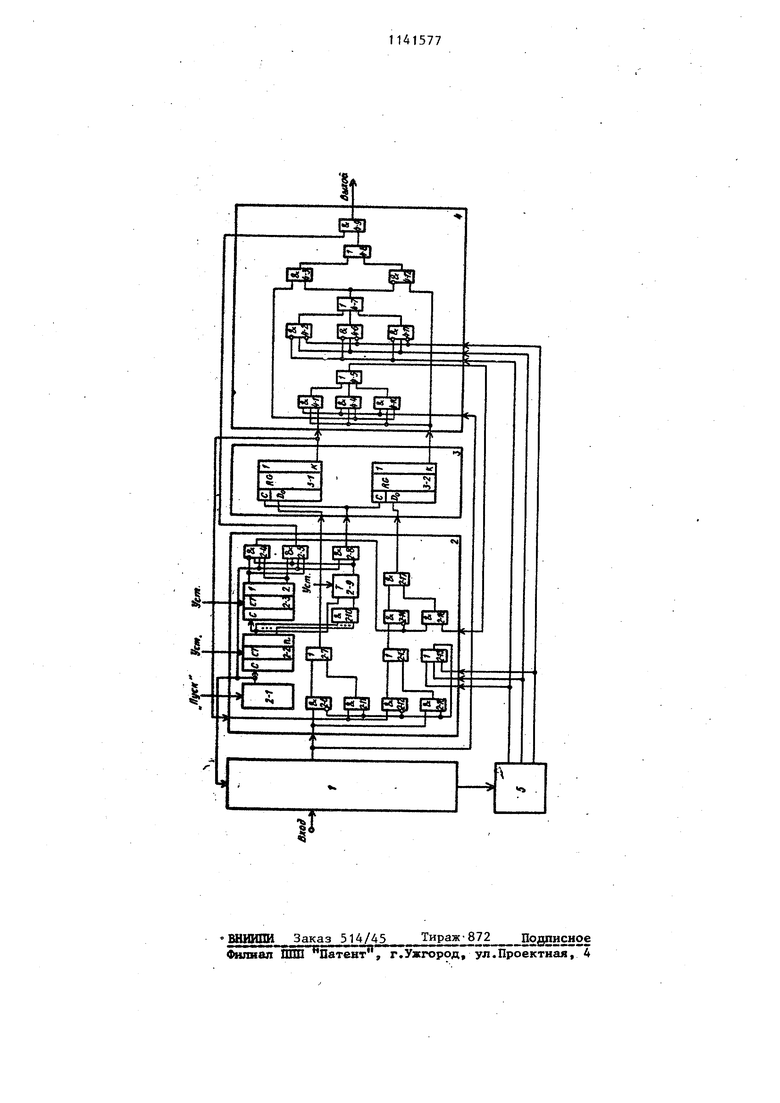

Изобретение относится к технике связи и может быть использовано для повьшения достоверности информации, передаваемой с использованием циклических кодов. По основному авт. св. N 677123 известно устройство для мажоритарного декодирования циклических кодов при трёхкратном повторении комбинации, содержащее последовательно соед ненные буферный блок памяти и мажоритарный элемент, к управляющим входам которого подключены выходы блока памяти кодовых комбинаций результатов декодирования, к входу которого и входу буферного блока памяти подключены соответственно дополнительны выход и вход декодера р . Однако известное устройство для мажоритарного декодирования циклических кодов при трехкратном повторении обладает низкой достоверностью Цель изобретения - повьшение достоверности. Для достижения цели в устройство для мажоритарного декодирования циклических кодов при трехкратном повто рении комбинации, содержащее последо вательно соединенные буферный блок памяти и мажоритарной элемент, к управляющим входам которого подключены выходы блока памяти кодовых комбинаций результатов декодирования, к вхо ду которого и входу буферного блока памяти подключены соответственно дополнительный выход и выход декодера введен анализатор кодовых комбинаций к первому входу которого и первому дополнительному входу мажоритарного элемента подключен выход декодера, к синхронизирующему входу которого подключен первьй выход анализатора кодовых комбинаций, к второму входу которого подключен соответствующий выход буферного блока памяти, а второй, третий, четвертый и пятый выходы анализатора кодовых комбинаций подключ-ены соответственно к второму дополнительному входу мажоритарного элемента и первому, второму и третьему входам буферного блока памяти, при этом дополнительный выход мажоритарного элемента и выходы блока памяти кодовых комбинаций результатов декодирования подключены соответственно к третьему, четвертому, пятому и шестому входам анализатора кодовых комбинаций, Причем анализатор кодовых комбинаций содержит два счетчика, триггер, четыре элемента ЗАПРЕТ, шесть элементов И, четыре элемента ИЛИ и генератор синхроимпульсов, выход которого подключен к входу первого счетчика, первому прямому входу первого элемента ЗАПРЕТ и первым входам первого и второго элементов И, при этом выход старшего разряда первого счетчика подключен к.входу второго счетчика и единичному входу триггера, выход которого подключен к вторым входам первого и второго элементов И и второму прямому входу первого элемента ЗАПРЕТ, к инверсному входу которого и третьему входу первого элемента И подключен первый выход-второго счетчика, второй выход которого подключен к третьему прямому входу первого элемента ЗАПРЕТ и четвертому входу первого элемента И, причем выходы разрядов первого счетчика подключены к входам третьего элемента И, выход которого подключен к нулевому входу триггера, а выходы второго элемента ЗАПРЕТ и четвертого элемента И подключены к первому входу первого элемента ИЛИ, выходы третьего элемента ЗАПРЕТ и пятого элемента И через второй элемент ШШ подключены к прямому входу четвертого элемента ЗАПРЕТ, к инверсному входу которого и первому входу шестого элемента И подключен выход первого элемента ЗАПРЕТ, а выходы четвертого элемента ЗАПРЕТ и шестого элемента И подключены к входам четвертого элемента ИЛИ, при этом прямой вход второго элемента ЗАПРЕТ объединен с первым входом пятого эле мента И и является перйым входом ана лизатора кодовых комбинаций, вторым входом которого является прямой вход третьего элемента ЗАПРЕТ, объединенньй с первым входом четвертого элемента И, к второму входу которого а также к инверсным входам второго |И третьего элементов ЗАПРЕТ и второ1му входу пятого элемента И подключен выход третьего элемента ИЛИ, входами ;которого являются соответственно четвертый, пятый и шестой входы ана|ЛИзатора кодовых комбинаций, третьим входом которого является второй вход шестого элемента И, при этом выходы ;генератора синхроимпульсов, первого элемента И, первого-элемента ИЛИ,второго элемента И и четрветого элемента ИЛИ являются соответственно первым, ;вторым, третьим, четвертым и пятым ; выходами анализатора кодовых комбиiнаций. На чертеже представлена структурная электрическая схема устройства для мажоритарного декодирования циклических кодов при трехкратном повто рении комбинации. Устройство для мажоритарного

декодирования циклических кодов при Qk-разрядные кодовые комбинации через

трехкратном повторении комбинациипервый вход анализатора кодозьпс комсодержит декодер 1, анализатор 2бинаций, элемент ЗАПРЕТ 2-6, элекодовых комбинаций , содержащий гене-мент ШШ 2-7, третий выход анализа;ратор 2-1 синхроимпульсов, счетчикитора 2 кодовых комбинаций, первый

;2-2 и 2-3, первый элемент 2-4 ЗА- 55вход буферного блока 3 памяти запиПРЕТ, первый элемент И 2-5, второйсываются в регистр 3-1. По ок нча:элемент. ЗАПРЕТ 2-6, первый элементник k-ro такта с момента начала при,,ИЛИ 2-7, второй элемент И 2-8, триг-ема первого йовторения сигналы с со- гер 2-9, третий 2-10 и четвертый 2-11 элементы И, третий элемент ЗАПРЕТ 2-12, второй элемент ИЛИ 2-13, четвертый элемент ЗАПРЕТ 2-14, третий элемент ИЛИ 2-15, пятый элемент И 2-16, четвертый элемент ИЛИ 2-17, шестой элемент И 2-18, буферный блок 3 памяти, содержащий регистры 3-1 и 3-2, мажоритарный элемент 4, содержащий первый элемент И 4-1, первый элемент .ЗАПРЕТ 4-2, второй 4-3 и третий 4-4 элементы И, первый элемент ИЛИ 4-5, второй, элемент ЗАПРЕТ 4-6, второй 4-7 и- третий 4-8 . элементы ИЛИ, четвертый 4-9 и пятый 4-10 элементы И, третий 4-11 и четвертый 4-12 элементы ЗАПРЕТ, блок 5 памяти кодовых комбинаций результатов декодирования. Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации работает следующим образом. В исходном положении триггер 2-9 устанавливается в единичное состояние и сигнал 1 с его выхода подается на вторые входы элемента ЗАПРЕТ. 2-4 и элемента И 2-5 и 2-8, а счётчики 2-2 и 2-3 устанавливаются в нулевое состояние. Одновременно с началом приема первого повторения на вход генератора 2-1 синхроимпульсов поступает сигнал Пуск, по которому он начинает выдавать на частоте п приема синхронизирующие импульсы на синхронизирукнций вход декодера 1, вход первого счетчика 2-2 и через элемент И 2-8, четвертый выход анализатора 2 кодовых комбинаций и первый вход буферного блока 3 памяти на синхронизирующие входы регистров 3-1 и 3-2. Емкость счетчика 2-2 равна числу разрядов п в принимаемой кодовой комбинации, закодированной Циклическим (п, k) кодом. п-Разрядные кодовые комбинации поступают на вход декодера 1, с выхода которого после декодирования (обнаружения и. если возможно, исправления ошибок) S1 отвётствующих выходов счетчика 2-2 через третий элемент И 2-10 переводят триггер 2-9 в нулевое состояние, запрещая тем самым прохождение синхронизирующих импульсов на синхронизирзлющие входы регистров 3-1 и 3-2. Таким образом, в течение последующих n-k тактов, когда в декодере 1 происходит формирование остатка от деле ния на образующий полином, запись и сдвиг информации в регистрах 3-1 и 3-2 отсутствуют. По истчении п тактов с момента начала приема первого повтЬрения с декодера 1 на вход блока 5 памяти кодовых комбинаций результатов декодирования поступает сигнал 1 , если оно принято без оши бок. С выхода этого блока сигнал 1 поступает на четвертый вход анализатора 2 кодовых комбинаций и через элемент ИЛИ 2-15 на инверсные входы второго 2-6 и третьего 2-12 элементов ЗАПРЕТ, а также на вторые входы элементов И 2-11 и 2-16, подготавливая анализатор 2 кодовых комбинаций к приему второго повторения. По окон чании приема первого повторения импульс переполнения со счетчика 2-2 поступает на единичный вход триггера 2-9, переводя его в единичное сое тояние и обеспечивая тем самым прохождение синхронизирующих импульсов на синхронизирующие входы регистров 3-1 и 3-2 в течение первых k тактов с момента начала приема второго повторения. Элементы второго повторения через первый вход анализатора 2 кодовых комбинаций, пятый элемент И 2-16 второй элемент ИЛИ 2-13, четвертый элемент ЗАПРЕТ 2-14, четвертьй элемент ИЛИ 2-17 и пятый выход буферного блока 3 памяти записьшается в регистр 3-2. В это время элементы пра вильно принятого первого повторения перезаписываются снова в регистр 3-1 через первый выход буферного блока 3 памяти, второй вход анализатора 2 кодовых комбинаций,. четвертый элемен И 2-11, первый элемент ИЛИ 2-7, первьй выход анализатора ; 2 кодовых комбинаций, первый вход буферного блока 3 памяти, через п тактов с момента начала приема второго повторе ния сигналы с выходов счетчика 2-3 откроют первьй э.лемент. ЗАПРЕТ 2-4 и синхронизирующие импульсы с генератора 2-1 синхроимпульсов в течение k тактов с момента начала приема 77 третьего по вторения поступают на инверсный вход четвертого элемента ЗАПРЕТ 2-14 и на первый вход шестого элемента И 2-18, запрещая запись третьего повторения в регистр 3-2 и подключая его вход через шестой элемент И 2-18 и четвертьй элемент ИЛИ 2-17 к дополнительному выходу мажоритарного элемента 4. Элементы третьего повторения с выхода декодера 1 поступают на первый дополнительный вход мажоритарного элемента 4 в течение первых k тактов с момента начала его приема. В ЭТО же время элементы первого и второго повторений поступают из регистров 3-1 и 3-2 через выходы буферного блока 3 памяти на входы мажоритарного элемента 4. Элементы И 4-1, 4-4, 4-10 и элемент ИЛИ 4-5 формируют мажоритарный результат обработки трех повторений, который через дополнительный выход мажоритарного элемента 4, третий вход анализатора 2 кодовых комбинаций, щестой элемент И 2-18, третий элемент ИЛИ 2-17, пятый выхоп анализатора 2 кодовых комбинаций, третий вход буферного блока 3 памяти записывается в регистр 3-2 на место второго повторения. В это же время элементы первого повторения снова перезаписываются в регистр 3-1. Таким образом, к моменту окончания приема третьего повторения в регистре 3-1 будет записано первое, принятое без ошибок, повторение, а во втором регистре 3-2 будет записан результат мажоритарной обработки трех повторений, через Зп тактов с момента начала приема первого повторения счетчик 2-3 разрешает прохождение синхронизируницих импульсов с генератора 2-1 синхроимпульсов через первьй элемент И 2-5, второй выход анализатора 2 кодовых комбинаций, второй дополнительньй вход мажоритарного элемента 4 на первый вход элемента И 4-9. Если первое повторение окажется единственным правильно принятым (код в блоке 5 памяти кодовых комбинаций результатов декодирования 100), на выходе элемента ИЛИ 4-7 появится сигнал .1, поступающий на инверсный вход элемента ЗАПРЕТ 4-12 и первый вход элемента. И 4-3, подключающий выход первого регистра 3-1 через элементы

И 4-3, ИЛИ 4-8, И 4-9 к выходу устройства.

Таким образом, первое повторение в течение k тактов с момента окончания приема третьего повторения вьщается получателю. Если же правильно приняты хотя бы два или все три повторения (код в блоке 5 памяти кодовых комбинаций результатов декодирования 110, 101, 111), сигнал 1 на выходе элемента ШШ 4-7 не появится, на выход устройства выдается результат мажоритарной обработки из регистра 3-2 через открытьш элемент ЗАПРЕТ 4-12 и Элементы ИЛИ 4-8 и И 4-9.

Если в первом повторении будут обнаружены ошибки, сигнал 1 по окончании его приема на первый вход анализатора кодовых комбинаций 2 не поступит, второй 2-6 и третий 2-12 элементы ЗАПРЕТ во время приема второго повторения останутся открытьми а четвертый 2-11 и пятый 2-16 элементы И закрытыми. При этом элементы второго повторения через первый вход анализатора 2 кодовых комбинаций второй элемент ЗАПРЕТ 2-6, первый элемент ИЛИ 2-7, первьш выход анализатора 2 кодовых комбинаций и первый вход буферного блока 3 памяти записываются в регистр 3-1 на место первого повторения, которые через первьй выход буферного блока 3 памяти, второй вход анализатора 2 кодовых комбинахщй, третий элемент ЗАПРЕТ 2-12, второй элемент ИЛИ 2-13, четвертый элемент ЗАПРЕТ 2-14, четверTbrii элемент ИЛИ 2-17, пятый выход анализатора 2 кодовых комбинаций и третий вход буферного блока 3 памяти перезаписываются в регистр 3-2 в течение первых k тактов с момента начала приема второго повторения. Если во втором повторении ошибок не обнаружено, по окончании его приема сигнал 1 с выхода блока 5 памяти кодовых комбинаций результатов декодирования через пятый вход анализатора 2 кодовых комбинаций и третий элемент ШШ 2-15 поступает на инверсные входы второго 2-6 и третьего 2-12 элементов ЗАПРЕТ и на. вторые входы четвертого 2-11 и пятого 2-16 элементов И.Прием третьего повторения ведется аналогично, как и в

предьщущем случае. При этом, если третье повторение/принято правильно (код в блоке 5 памяти, кодовых комбинаций результатов декодирования 5 011)., мажоритарный элемент 4 выдает получателю результат мажоритарной обработки из регистра 3-2, если же второе повторение окажется единственным правильно принятым (код в

блоке 5 памяти кодовых комбинаций результатов декодирования 010) получателю выдается второе повторение из регистра 3-1.

Если во втором повторений, также

5 будут обнаружены ошибки, сигнал 1 также не поступит на первый вход анализатора 2 кодовых комбинаций, по окончании приема второго повторения второй 2-6 и третий 2-12 элементы ЗАПРЕТ остаются открытыми, а четвертьй 2-10 и пятый 2-16 элементы И закрытыми и во время приема третьего повторения. В этом случае элементы третьего повторения поступают одновременно на первый дополнительный вход мажоритарного элемента 4 и первый вход анализатора 2 кодовых комбинаций.

0 При этом третье повторение через второй элемент ЗАПРЕТ 2-6 и первый элемент ИЛИ 2-7, второй выход анализатора 2 кодовых комбинаций и первый вход буферного блока 3 памяти

5 записываются в регистр 3-1 на место второго повторения, а во второй регистр 3-2 записьшаётся результат мажоритарной обработки трех повторений, аналогично ранее рассмотренному. При этом, если в третьем повторении ошибок не обнаружено (код в блоке 5 памяти кодовых комбинаций результатов декодирования 001), получателю выдается третье повторение из регистра 3-1, если же ошибки будут обнаружены и в третьем повторении получателю выдается результат мажоритарной обработки трех повторений из регистра 3-2 (код в блоке 5

0 памяти кодовых комбинаций результатов декодирования 000).

Таким образом, устройство для мажорита рного декодирования циклических кодов при трехкратном повторении

3 комбинаций обеспечивает высокую достоверность принимаемой информации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1978 |

|

SU677123A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-02-23—Публикация

1983-11-25—Подача