второго элемента И, выход формирователя импульсов подключен к второму входу первого элемента И-НЕ, выход которого подключен к первому входу элемента И формирователя

сигналоввыборки, выход формирователя импульсов подключен к управляющему входу коммутатора и соединен со счетным входом счетчика адреса регенерации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДИНАМИЧЕСКОЙ ПАМЯТЬЮ, содержащее генератор импульсов регенерации, счетчик адреса регенерации, коммутатор, причем выход счетчика адреса регенерации подключен к первому информационному входу коммутатора, выход которого подключен к выходу адреса устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит три элемента И-НЕ,два элемента И, элемент ИЛИ, элемент ИЛИ-НЕ, реверсивный счетчик, формирователь сигналов выборки и формирователь сигналов регенерации, причем первБЙ вход первого элемента И-НЕ подключен к входу запроса устройства, второй вход первого элемента И-НЕ соединен с входом суммирования реверсивного счетчика, вход вычитания которого соединен с выЬсодом генератора импульсов регенерации, а выход подключен к входам второго элемента И-НЕ и соединен с входами элемента ИЛИ-НЕ, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента И-НЕ, а выход подключен к первому входу элемента RITli, второй вход которого подключен к выходу второго элемента И, первьй вход которого подключен к выходу второго элемента И-НЕ, второй информационньм вход коммутатора подключен к входу адреса устройства, причем формирователь сигналов выборки содержит элемент И и элемент задержки, вход элемента задержки формирователя сигналов выборки соединен с первым входом элемента И формирователя сигналов выборки, выход (Л которого и выход элемента задержки формирователя сигналов выборки подключены к первому управляющему вьгходу устройства, .выход элемента задержки формирователя сигналов выборки подключен к первому входу третьего элемента И-НЕ, выход которого подключен к второму управляюще4; му выходу устройства, а формироваip тель сигналов регенерации содержит два элемента зедержки и формирователь импульсов, причем выход элеменел та ИЛИ через первьй элемент задержки формирователя сигналов регенерации подключен к входу формирователя импульсов, выход которого подключен к входу второго элемента задержки формирователя сигналов регенерации, выход которого подключен к второму входу третьего элемента И-НЕ,выход формирователя импульсов подключен к второму входу элемента И формирователя сигналов выборки, выход которого подключен к второму входу

1

Изобретение относится к вычислительной технике и может быть использовано в устройстве управления памятью ЭВМ, выполненной на интегральных схемах полупроводниковой динамической памяти.

Известно устройство для управления полупроводниковой памятью,содержащее блок управления, в состав которого входят счетчик тактовых импульсов, дешифратор тактовых импульсов и узел формирования и вьдачи управляющих сигналов, блок регенерации информации, содержащий генератор импульсов регенерации, узел управления регенерацией и счетчик адресов регенерации, блок ввода-вьгоода, состоящий из генератора тактовых импульсов, регистра адреса и регистра слова, а также блок местного управления, элементы И, ИЛИ и генераторы импульсов l

В данном устройстве процесс регенерации выделен в отдельный режим работы и производится для всего объема адресуемой памяти в течение непрерьганого интервала времени, что требует дополнительное время на регенерацию, в течение которого доступ к памяти запрещен.

Известно устройство, содержащее генератор импульсов регенерации, счетчик адреса регенерации, блок управления и коммутатор, причем выход счетчика адреса подключен к первому информационному входу коммутатора, выход которого подключен к выходу адреса устройства. В устройстве последовательность тактов регенерации разнесена во времени так, что очередной такт регенерации происходит через период времени Т TP/N с таким расчетом,чтобы в накопителе произошел полный перебор адресуемых частей накопителя за

время, равное периоду регенерации Т , где N - количество тактов регерации 2 .

Недостатком известного устройства является синхронная временная диаграмма регенерации, что приводи к возникновению конфликтов при обращении к памяти.

Цель изобретения - повышение быстродействия устройства путем уменьшения среднего времени ожидания процессора при обращении к памяти.

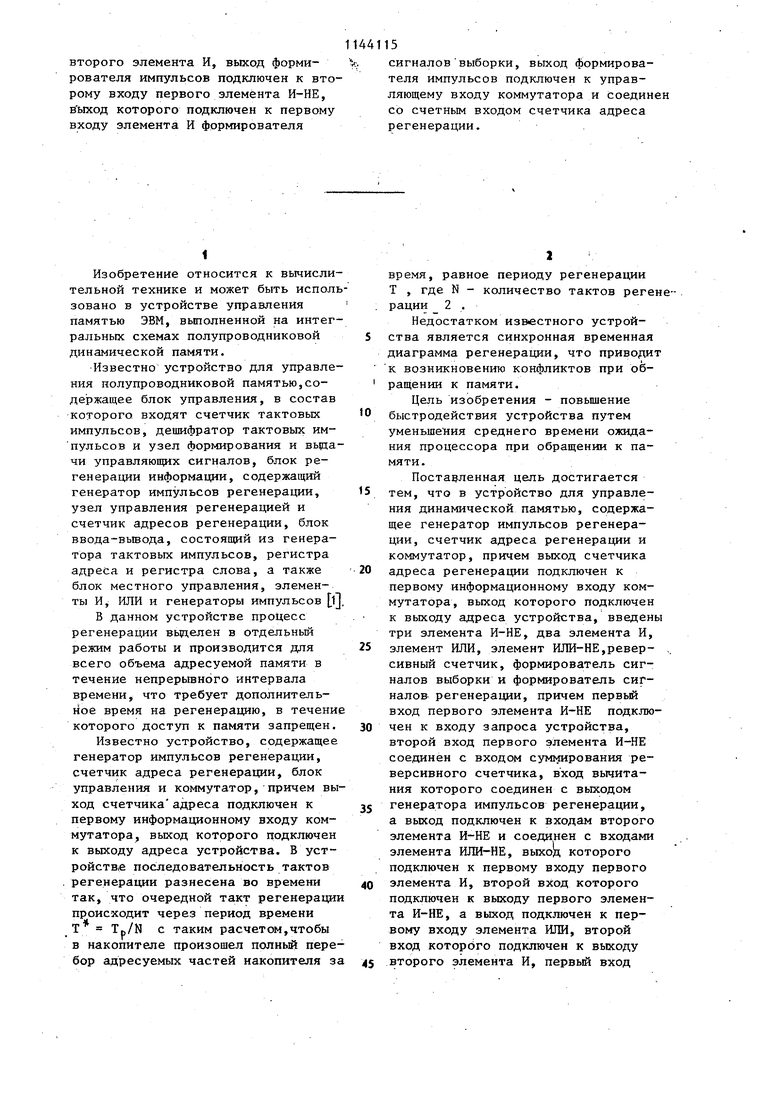

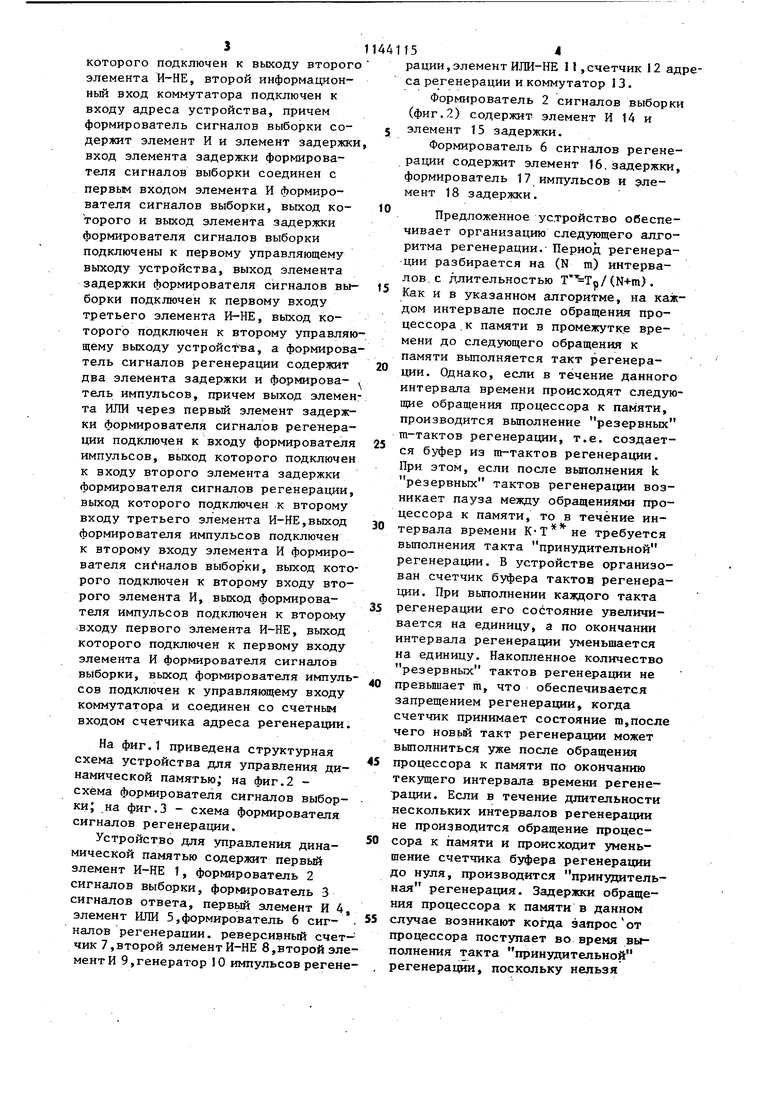

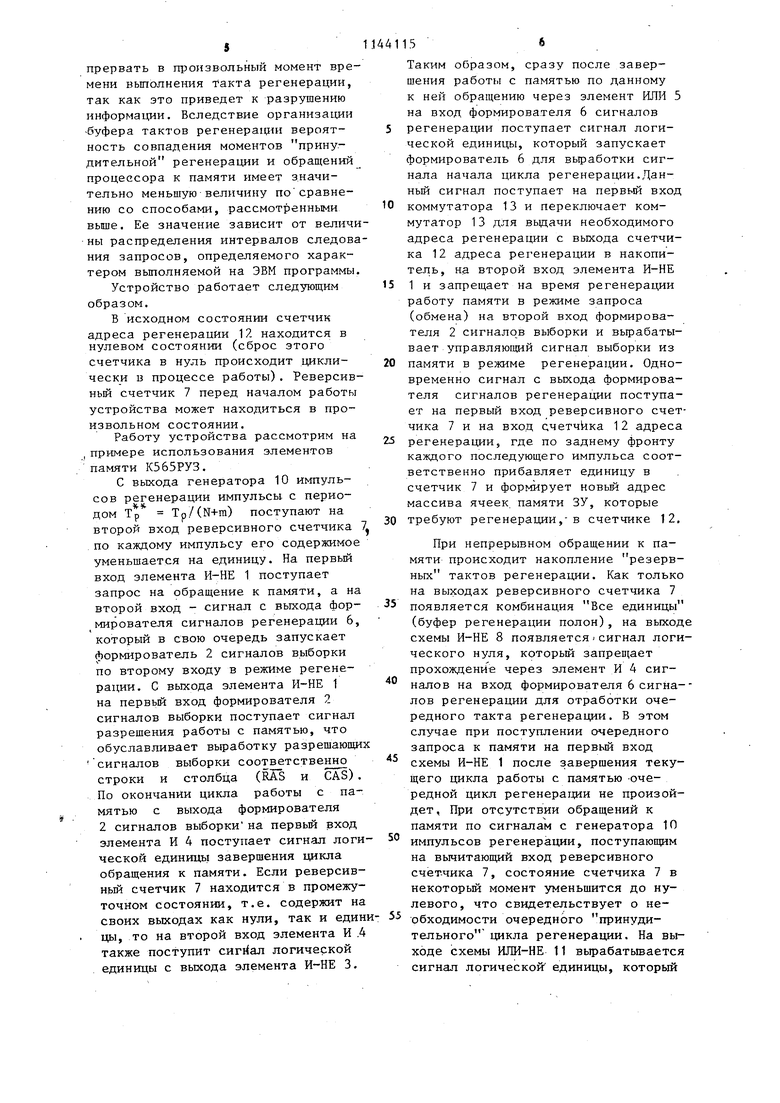

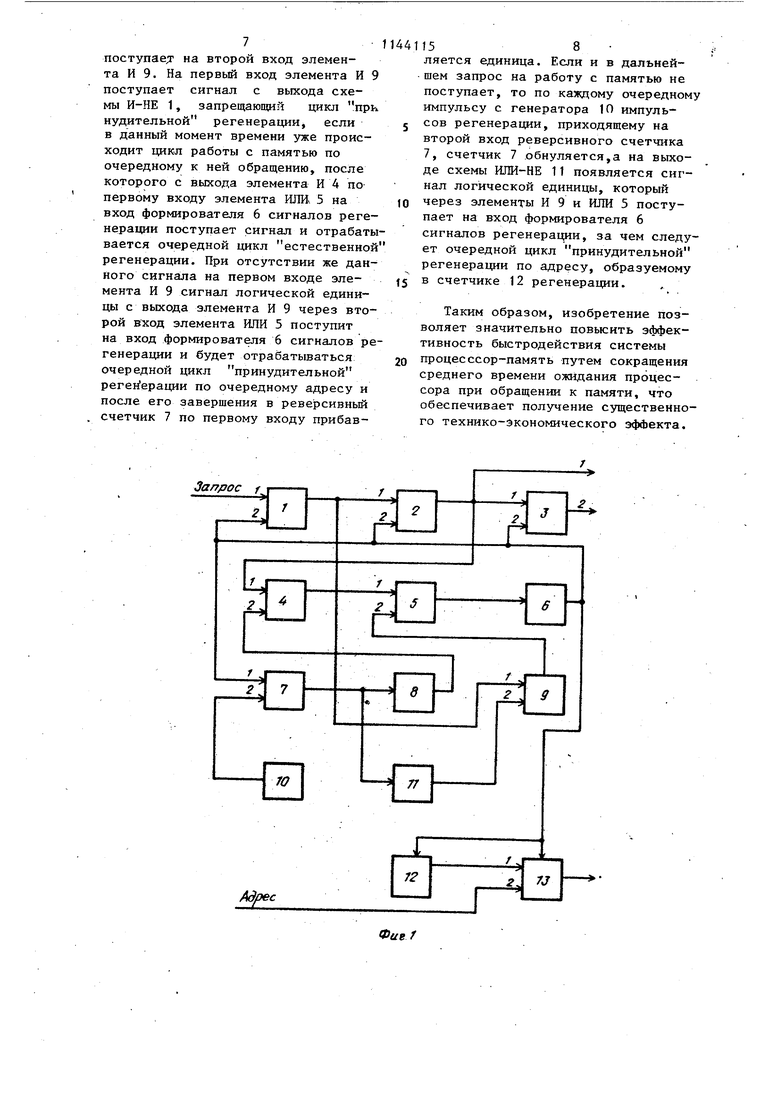

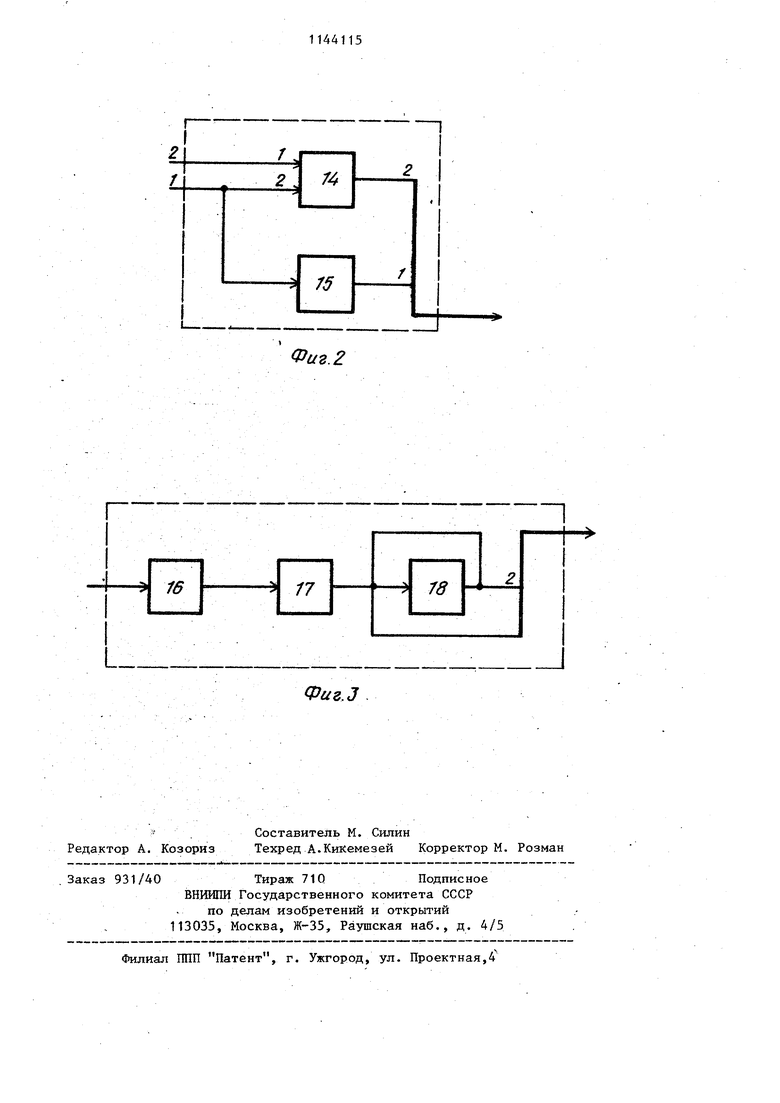

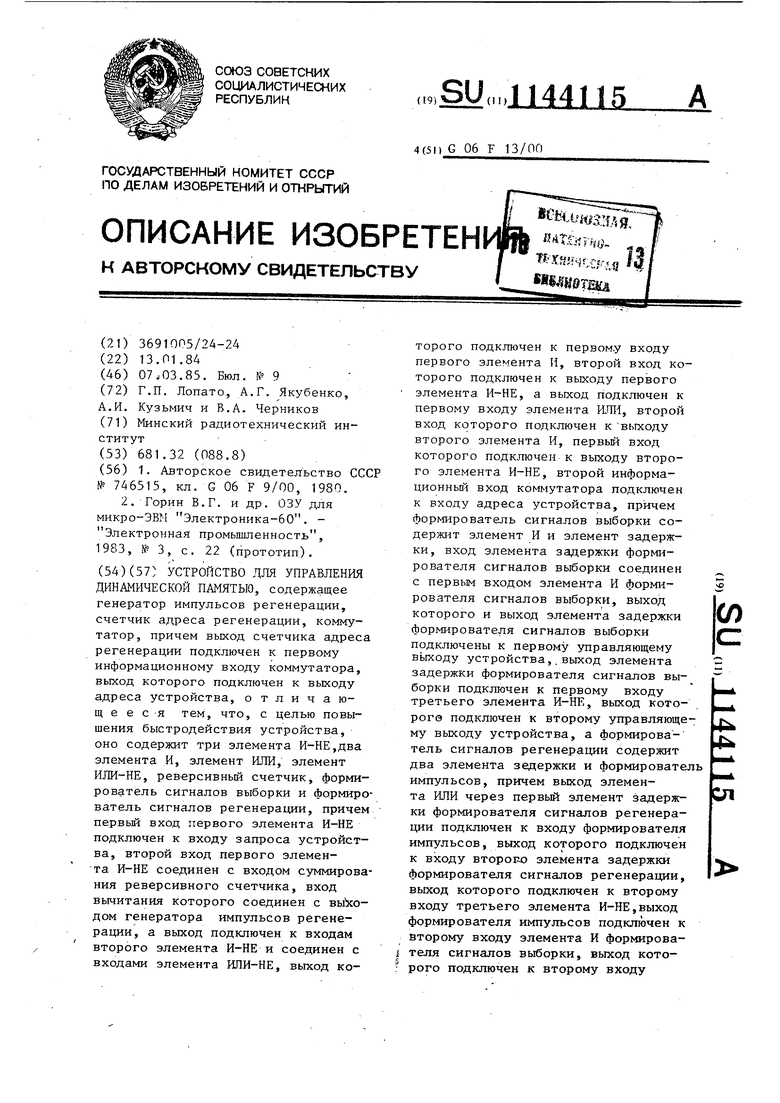

Поставленная цель достигается тем, что в устройство для управления динамической памятью, содержащее генератор импульсов регенерации, счетчик адреса регенерации и коммутатор, причем выход счетчика адреса регенерации подключен к первому информационному входу коммутатора, выход которого подключен к выходу сщреса устройства, введен три элемента И-НЕ, два элемента И, элемент ИЛИ, элемент ИЛИ-НЕ,реверсивный счетчик, формирователь сигналов выборки и формирователь сигналов регенерации, причем первый вход первого элемента И-НЕ подключен к входу запроса устройства, второй вход первого элемента И-НЕ соединен с входом суммирования реверсивного счетчика, вход вычитания которого соединен с выходом генератора импульсов регенерации, а выход подключен к входам второго элемента И-НЕ и соединен с входами элемента ШШ-НЕ, выход которого подключен к первому входу первого элемента И, второй вход которого подключен к выходу первого элемента И-НЕ, а выход подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, первьй вход 3 которого подключен к выходу второго элемента И-НЕ, второй информационньй вход коммутатора подключен к входу адреса устройства, причем формирователь сигналов выборки содержит элемент И и элемент задержки вход элемента задержки формирователя сигналов выборки соединен с первым входом элемента И формирователя сигналов выборки, выход которого и выход элемента задержки формирователя сигналов выборки подключены к первому управляющему выходу устройства, выход элемента задержки формирователя сигналов выборки подключен к первому входу третьего элемента И-НЕ, выход которого подключен к второму управляю щему выходу устройства, а формирова тель сигналов регенерации содержит два элемента задержки и формирователь импульсов, причем выход элемен та ИЛИ через первый элемент задержки формирователя сигналов регенерации подключен к входу формирователя импульсов, выход которого подключен к входу второго элемента задержки формирователя сигналов регенерации выход которого подключен к второму входу третьего элемента И-НЕ,выход формирователя импульсов подключен к второму входу элемента И формирователя си налов выборки, выход кото рого подключен к второму входу второго элемента И, выход формирователя импульсов подключен к второму входу первого элемента И-НЕ, выход которого подключен к первому входу элемента И формирователя сигналов выборки, выход формирователя импуль сов подключен к управляющему входу коммутатора и соединен со счетным входом счетчика адреса регенерации На фиг,1 приведена структурная схема устройства для управления динамической памятью; на фиг.2 схема формирователя сигналов выборки; на фиг.З - схема формирователя сигналов регенерации. Устройство для управления динамической памятью содержит первый элемент И-НЕ 1, формирователь 2 сигналов выборки, формирователь 3 сигналов ответа, первый элемент И 4 элемент ИЛИ 5,формирователь 6 сигналов регенерации, реверсивный счет чик 7,второй элемент И-НЕ 8,второй эл мент И 9,генератор 10 импульсов реген t5Л рации,элемент ИЛИ-НЕ II, счетчик 12 адреса регенерации и коммутатор 13. Формирователь 2 сигналов выборки (фиг.2) содержит элемент И 14 и элемент 15 задержки. Формирователь 6 сигналов регенерации содержит элемент 16, задержки, формирователь 17 импульсов и элемент 18 задержки. Предложенное устройство обеспечивает организацию следующего алгоритма регенерации.- Период регенерации разбирается на (N т) интервалов, с длительностью T Tp/(N+m) . Как и в указанном алгоритме, на каждом интервале после обращения процессора ,к памяти в промежутке времени до следующего обращения к памяти вьшолняется такт регенерации. Однако, если в течение данного интервала времени происходят следующие обращения процессора к памяти, производится выполнение резервных га-тактов регенерации, т.е. создается буфер из т-тактов регенерации. При этом, если после выполнения k резервньпс тактов регенера1щи возникает пауэа меязду обращениями процессора к памяти, то в течение интервала времени требуется выполнения такта принудительной регенерации. В устройстве организован счетчик буфера тактов регенерации. При выполнении казвдого такта регенерации его состояние увеличивается на единицу, а по окончании интервала регенерации уменьшается на единицу. Накопленное количество резервных тактов регенерации не превышает т, что обеспечивается запрещением регенерации, когда счетчик принимает состояние го,после чего новьй такт регенерации может вьтолниться уже после обращения процессора к памяти по окончанию текущего интервала времени регенерации. Если в течение длительности нескольких интервалов регенерации не производится обращение процессора к памяти и происходит уменьшение счетчика буфера регенерации до нуля, производится принудительная регенерация. Задержки обращения процессора к памяти в данном возникают когда запросот процессора поступает во время выполнения такта принудительной регенерации, поскольку нельзя прервать в произвольный момент времени выполнения такта регенерации, так как это приведет к разрушению информации. Вследствие организации -буфера тактов регенерации вероятность совпадения моментов принудительной регенерации и обращений процессора к памяти имеет значительно меньа1ую величину посравнению со способами, рассмотренными выше. Ее значение зависит от величи ны распределения интервалов следова ния запросов, определяемого характером выполняемой на ЭВМ программы Устройство работает следующим образом. В исходном состоянии счетчик адреса регенерации 12 находится в нулевом состоянии (сброс этого счетчика в нуль происходит циклически в процессе работы). Реверсив ный счетчик 7 перед началом работы устройства может находиться в произвольном состоянии. Работу устройства рассмотрим на , примере использования элементов - памяти К565РУЗ. С выхода генератора 10 импульсов регенерации импульсы, с периодом Тр Tp/(N+m) поступают на второй вход реверсивного счетчика по каждому импульсу его содержимое уменьшается на единицу. На первый вход элемента И-НЕ 1 поступает запрос на обращение к памяти, а на второй вход - сигнал с выхода формирователя сигналов регенерации 6, который в свою очередь запускает формирователь 2 сигналов выборки по второму входу в режиме регенерации. С выхода элемента И-НЕ 1 на первьй вход формирователя 2 сигналов выборки поступает сигнал разрешения работы с памятью, что обуславливает выработку разрешающи сигналов выборки соответственно строки и столбца (RAS и CAS) По окончании цикла работы с памятью с выхода формирователя 2 сигналов выборки на первьй вход элемента И 4 поступает сигнал лог ческой единиць завершения цикла обращения к памяти. Если реверсив ный счетчик 7 находится в промежу точном состоянии, т.е. содержит н своих выходах как нули, так и еди цы, то на второй вход элемента И . также поступит сигнал логической единицы с выхода элемента И-НЕ 3. Таким образом, сразу после завершения работы с памятью по данному к ней обращению через элемент ИЛИ 5 на вход формирователя 6 сигналов регенератдии поступает сигнал логической единицы, который запускает формирователь 6 для выработки сигнала начала цикла регенерации.Данньй сигнал поступает на первьй вход коммутатора 13 и переключает коммутатор 13 для вьщачи необходимого адреса регенерации с выхода счетчика 12 адреса регенерации в накопитель, на второй вход элемента И-НЕ 1 и запрещает на время регенерации работу памяти в режиме запроса (обмена) на второй вход формирователя 2 сигналов выборки и вырабатывает управляющий сигнал выборки из памяти в режиме регенерации. Одновременно сигнал с выхода формирователя сигналов регенерации поступает на первый вход реверсивного счетчика 7 и на вход счетчика 12 адреса регенерации, где по заднему фронту каждого последующего импульса соответственно прибавляет единицу в счетчик 7 и формирует новьй адрес массива ячеек памяти ЗУ, которые требуют регенерации,-в счетчике 12. При непрерывном обращении к памяти происходит накопление резервных тактов регенерации. Как только на выходах реверсивного счетчика 7 появляется комбинация Все единицы (буфер регенерации полон), на выходе схемы И-НЕ 8 появляетсясигнал логического нуля, который запрещает прохожденйе через элемент И 4 сигналов на вход формирователя 6сигна-лов регенерации для отработки очередного такта регенерации. В этом случае при поступлении очередного запроса к памяти на первьй вход схемы И-НЕ 1 после завершения текущего цикла работы с памятью -очередной цикл регенератдаи не произойдет , При отсутствии обращений к памяти по сигналам с генератора 10 импульсов регенерации, поступающим на вычитающий вход реверсивного счетчика 7, состояние счетчика 7 в некоторьй момент уменьшится до нулевого, что свидетельствует о необходимости очередного принудительного цикла регенерации. На выходе схемы ИЛИ-НЕ 11 вырабатывается сигнал логической единицы, который nocrynaej на второй вход элемента И 9. На первый вход элемента И 9 поступает сигнал с выхода схемы И-НЕ 1, запрещающий цикл прк нудительной регенерации, если в данный момент времени уже происходит цикл работы с памятью по очередному к ней обращению, после которого с выхода элемента И 4 по первому входу элемента ИЛИ 5 на вход формирователя 6 сигналов регенерации поступает сигнал и отрабаты вается очередной цикл естественной регенерации. При отсутствии же данного сигнала на первом входе элемента И 9 сигнал логической единицы с выхода элемента И 9 через второй вход элемента ИЛИ 5 поступит на вход формирователя 6 сигналов ре генерации и будет отрабатываться очередной цикл принудительной регенерации по очередному адресу и после его завершения в реве рсивный счетчик 7 по первому входу прибав58ляется единица. Если и в дальнейшем запрос на работу с памятью не поступает, то по каждому очередному импульсу с генератора 10 импуль- сов регенерации, приходящему на второй вход реверсивного счетчика 7, счетчик 7 обнуляется,а на выходе схемы ИЛИ-НБ 11 появляется сигнал логической единицы, который через элементы И 9 и ИЛИ 5 поступает на вход формирователя 6 сигналов регенерации, за чем следует очередной цикл принудительной регенерации по адресу, образуемому в счетчике 12 регенерации. Таким образом, изобретение позволяет значительно повысить эффективность быстродействия системы процесссор-память путем сокращения среднего времени ожидания процессора при обращении к памяти, что обеспечивает получение существенного технико-экономического эффекта.

Фиг. 2

Фиг,3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления полупроводниковой памятью | 1977 |

|

SU746515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Горин В.Г, и др | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Электронная промышленность, 1983, № 3, с, 22 (прототип). | |||

Авторы

Даты

1985-03-07—Публикация

1984-01-13—Подача