Изобретение относится к вычислительной технике, в частности к средствам микропроцессорного управления и может быть использовано в автоматизированных системах управления обработки информации и измерительных системах с применением микропроцессоров и/или ЭВМ.

Цель изобретения - повышение пропускной способности устройства за счет увеличения скорости выполнения системных операций.

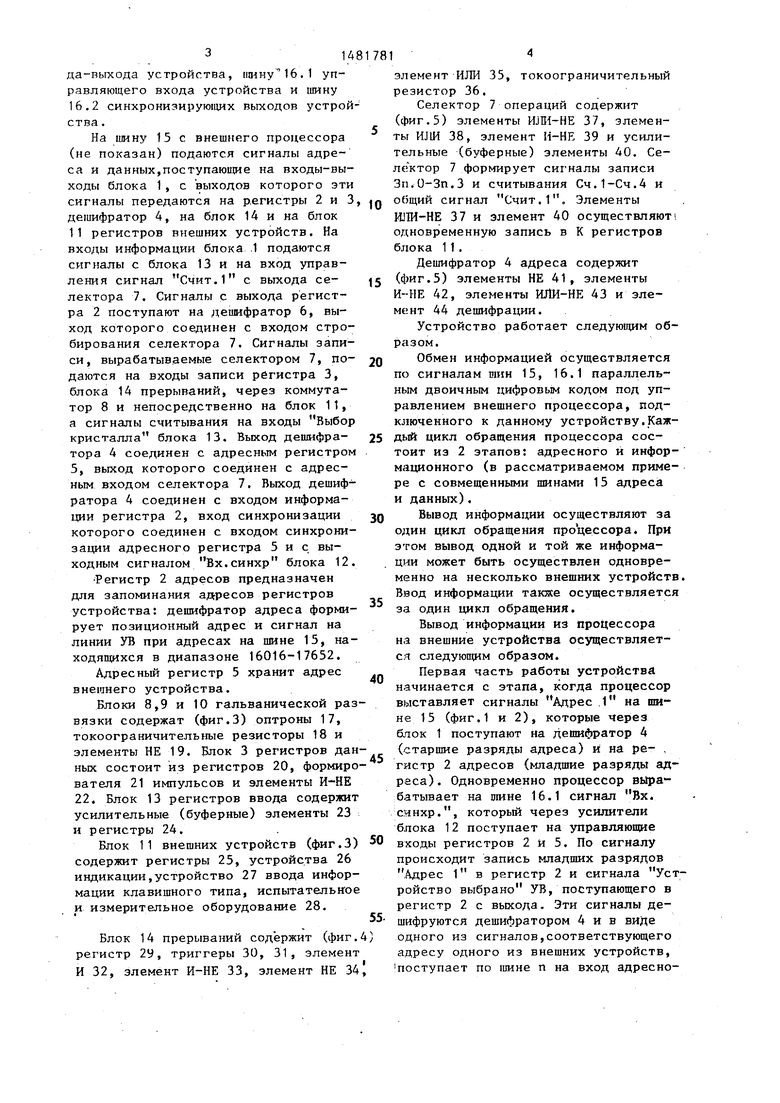

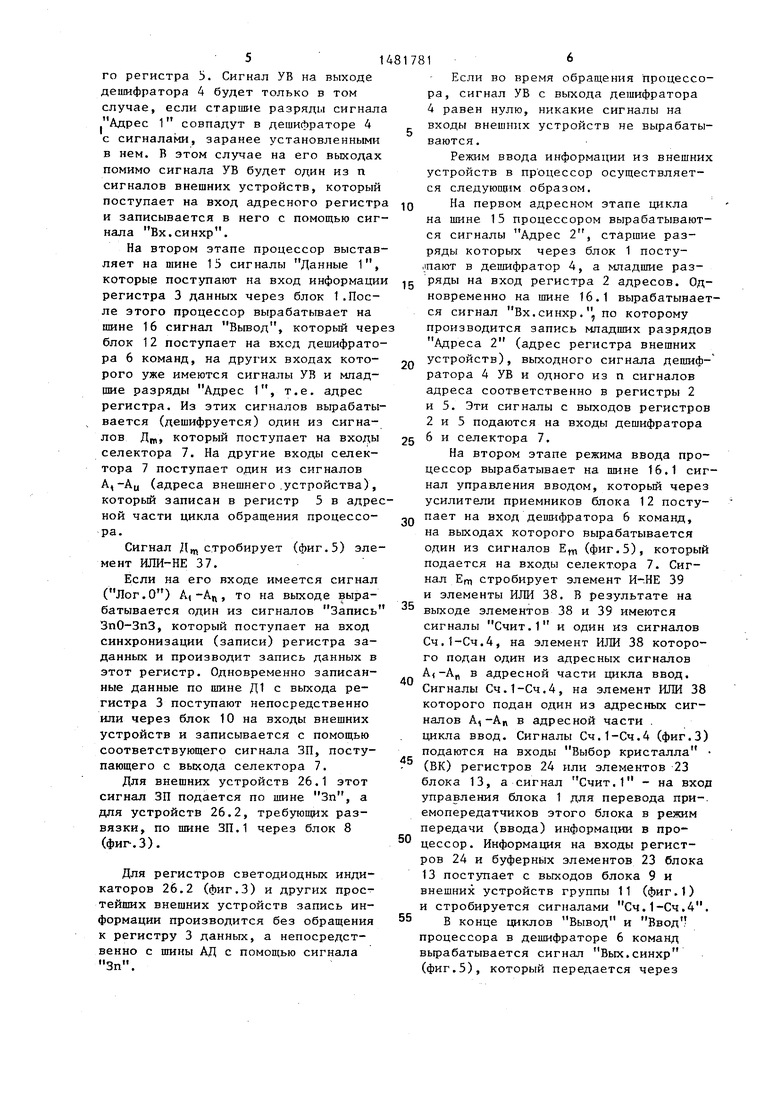

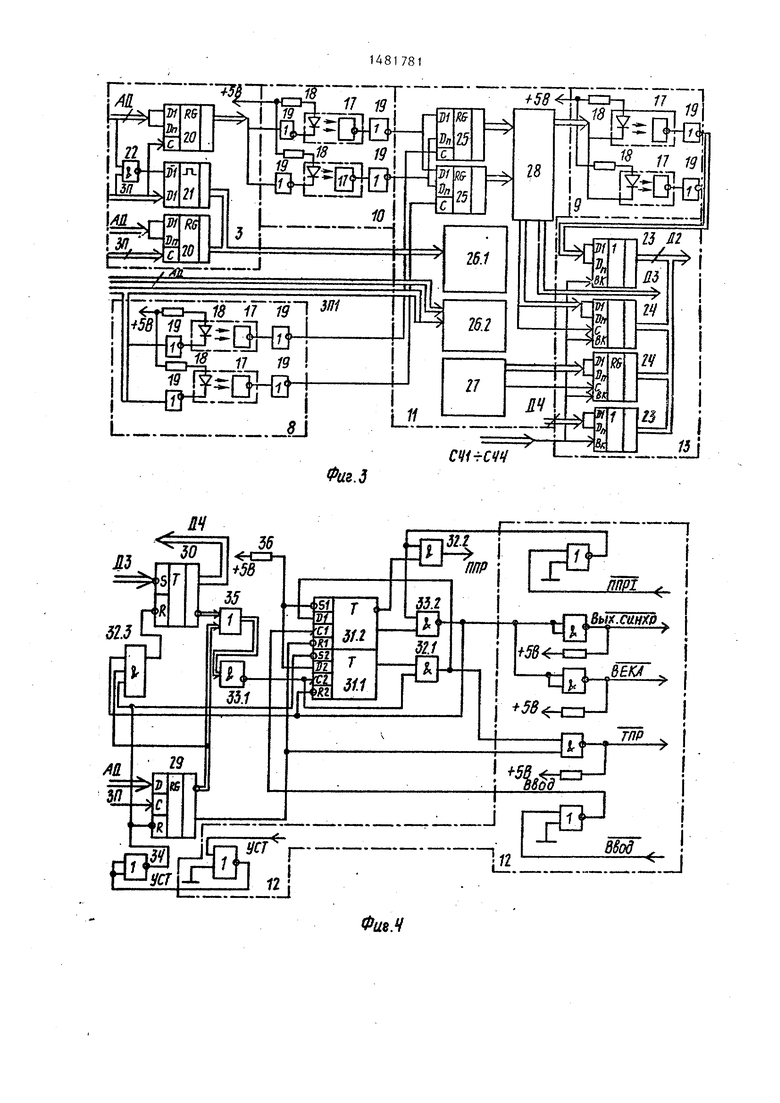

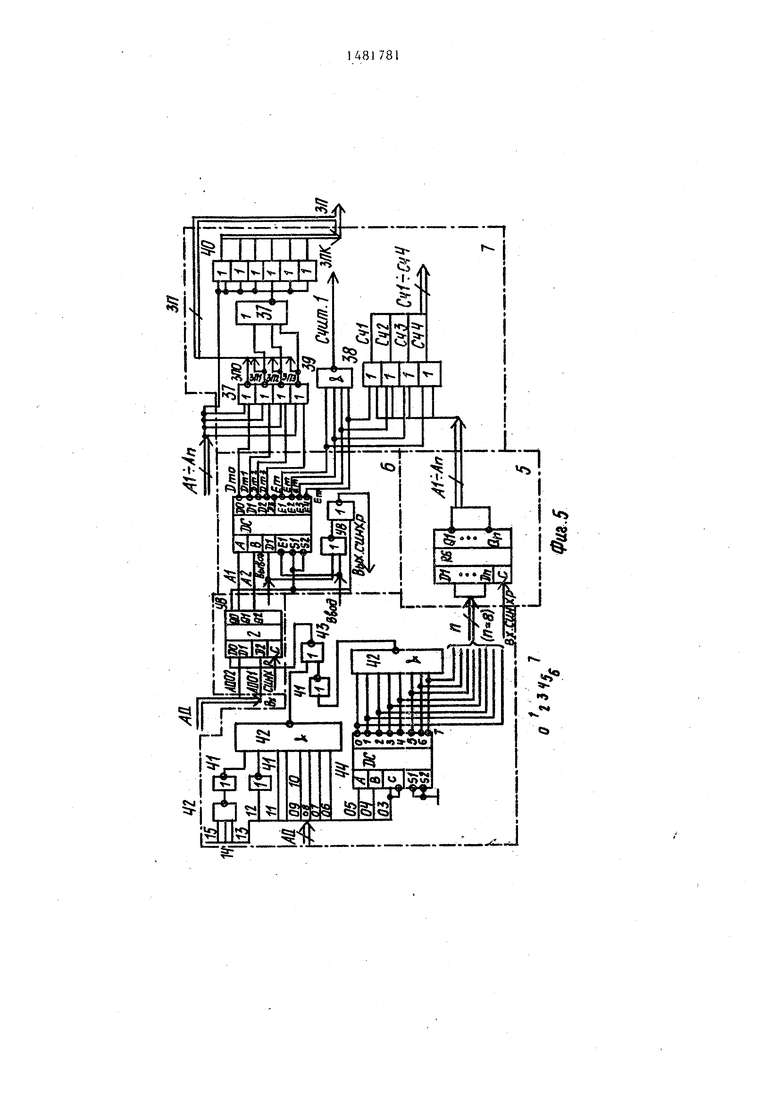

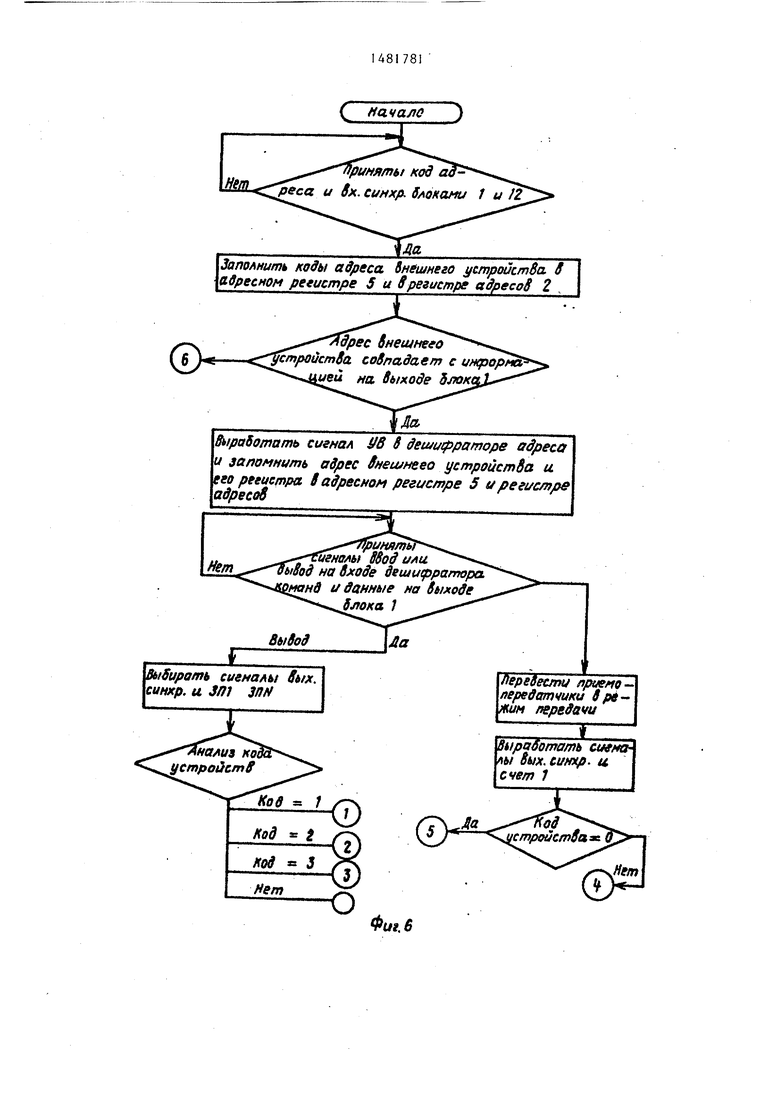

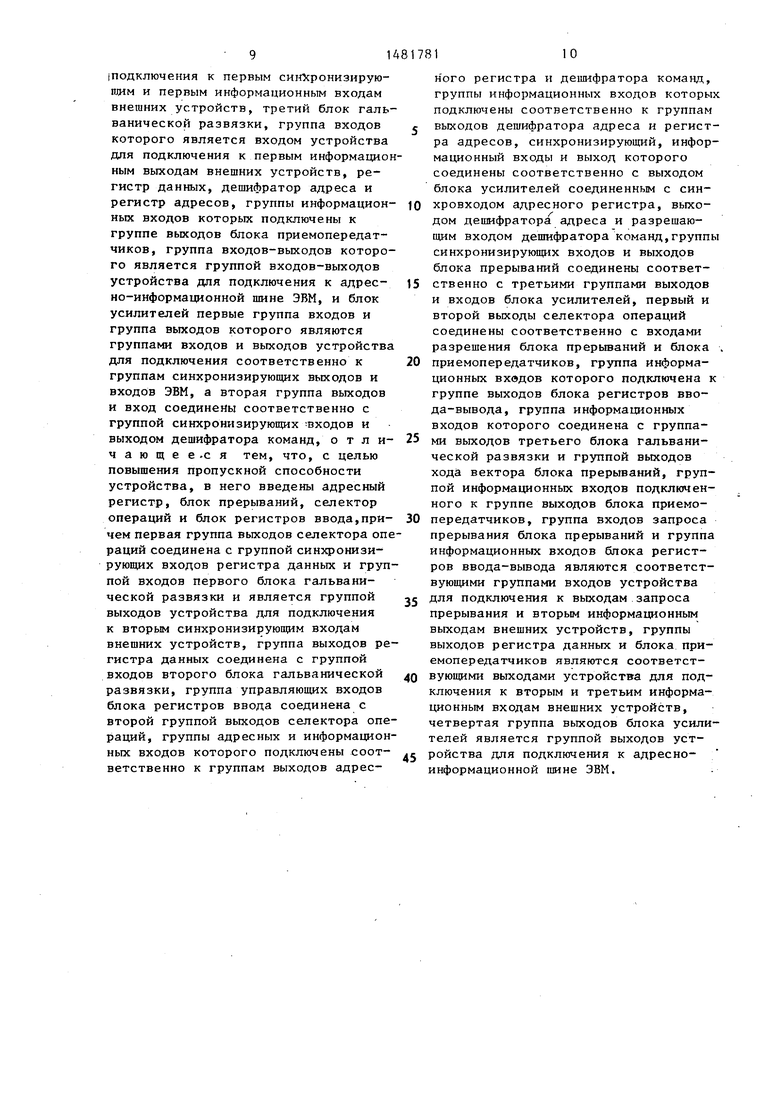

На фиг.1 представлена блок-схема устройства} на фиг.2 - временные диаграммы работы устройства1,на фиг.З функциональные схемы блоков гальванической развязки, блока регистров ввода-вывода, регистра данных и

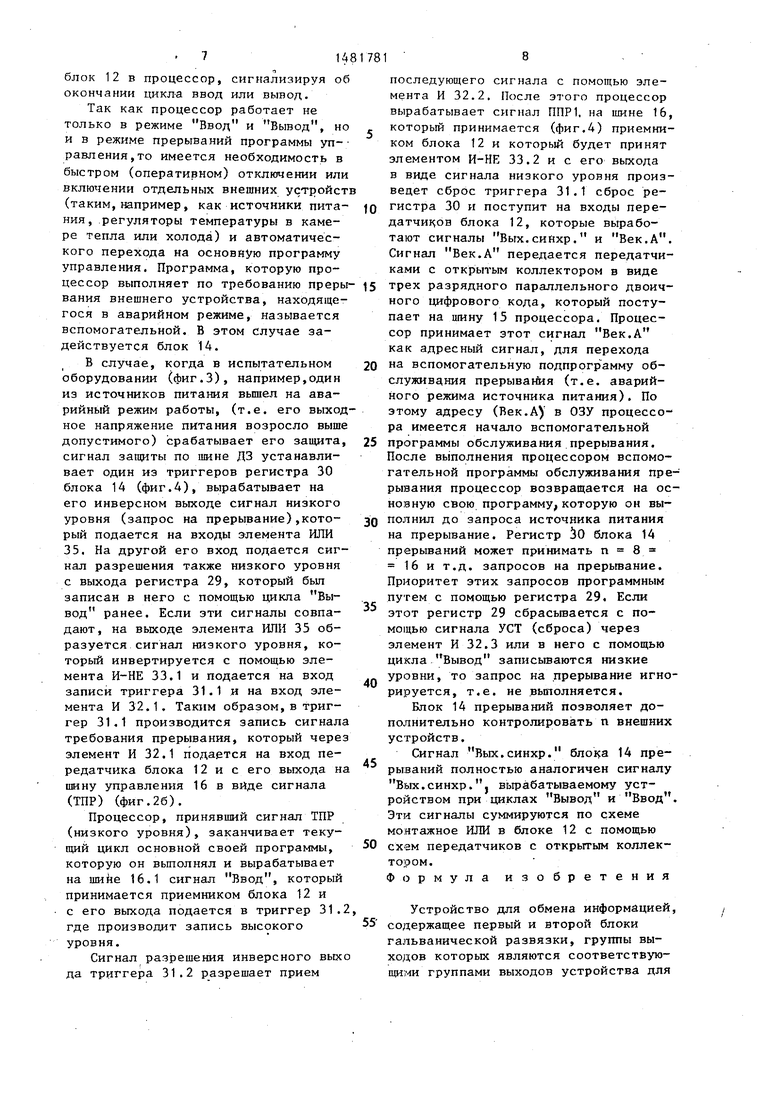

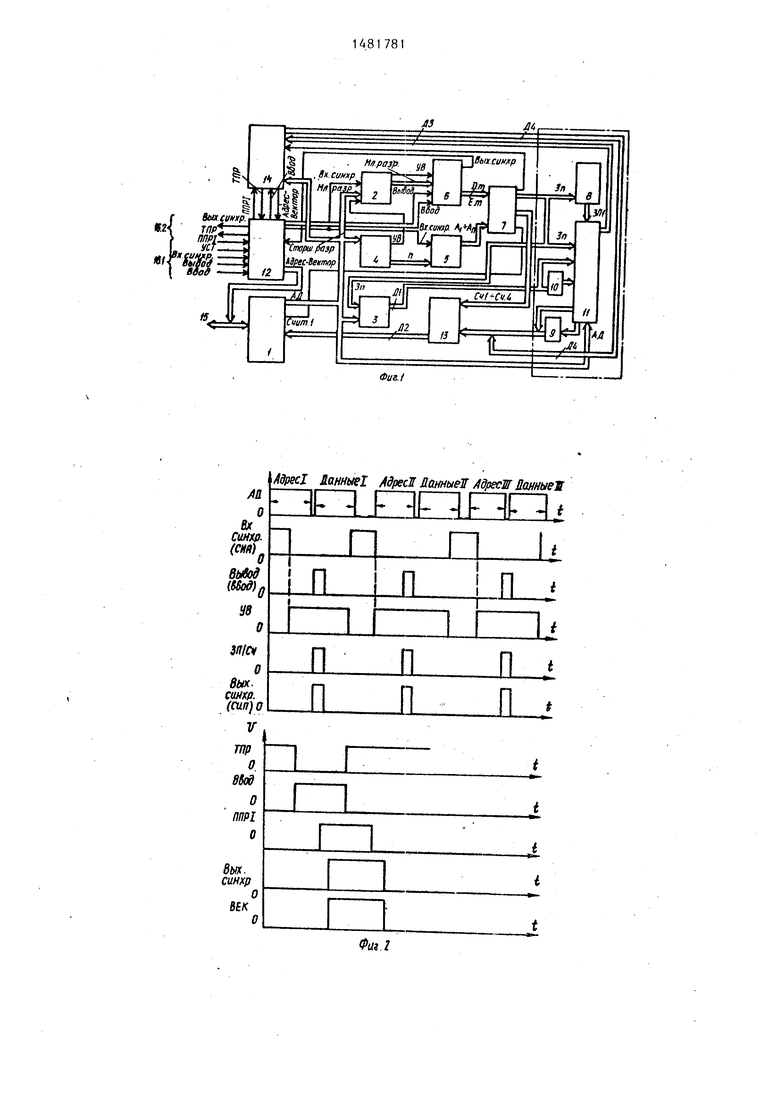

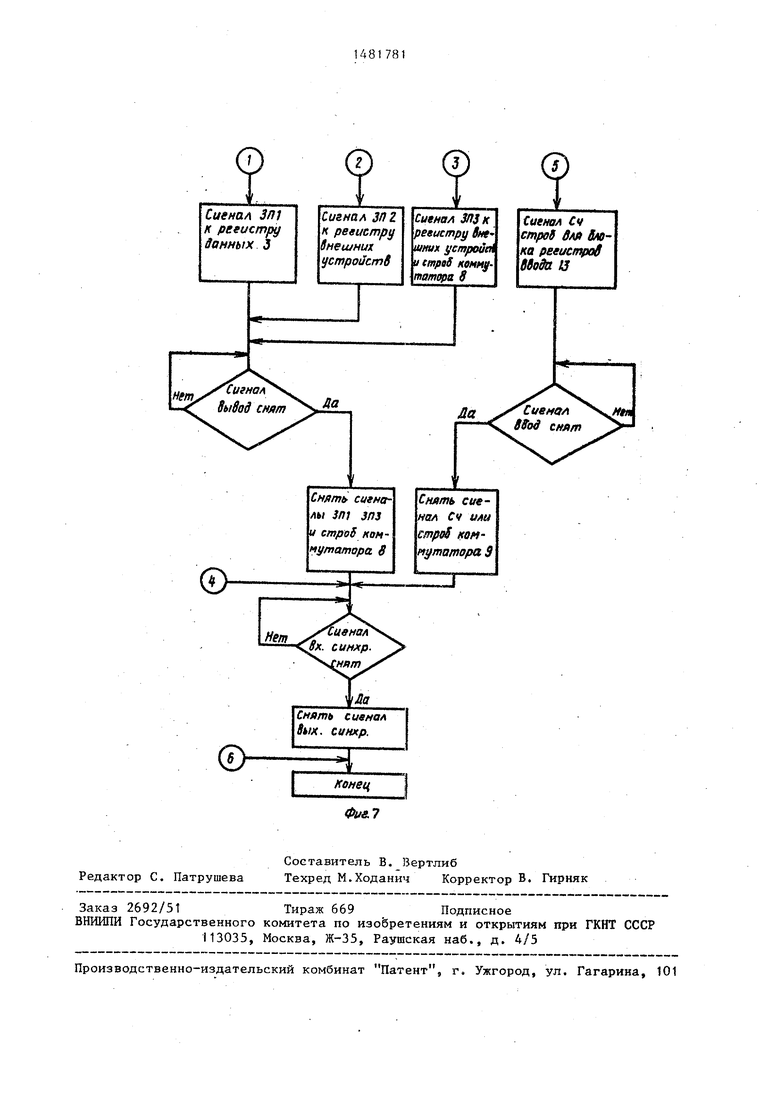

структура подключения внешних устройств} на фиг.4 - функциональная схема блока прерываний на фиг.5 - функциональные схемы дешифраторов адреса и команд и селектора операций} на фиг. 6 и 7 - блок-схемы алгоритмов работы устройства.

Устройство (фиг,1) содержит блок 1 приемопередатчиков, регистр 2 адресов, регистр 3 данных, дешифратор 4 адреса, адресный регистр 5, дешифратор 6 команд, селектор 7 операций, первый, третий и второй блоки 8, 9 и 10 гальванической развязки, группа (блок) 11 регистров внешних устройств, блок 12 усилителей, блок 13 регистров ввода, блок 14 прерываний, шину 15 адресно-информационного вхо

ас

оо

да-выхода устройства, .1 управляющего входа устройства и шину 16.2 синхронизирующих выходов устройства .

На шину 15 с внешнего процессора (не показан) подаются сигналы адреса и данных,поступающие на входы-выходы блока 1, с выходов которого эти сигналы передаются на регистры 2 и 3 дешифратор 4, на блок 14 и на блок 11 регистров внешних устройств. На входы информации блока 1 подаются сигналы с блока 13 и на вход управления сигнал Счит.1 с выхода се- лектора 7. Сигналы с выхода регистра 2 поступают на дешифратор 6, выход которого соединен с входом стро- бирования селектора 7. Сигналы записи, вырабатываемые селектором 7, по- даются на входы записи регистра 3, блока 14 прерываний, через коммутатор 8 и непосредственно на блок 11, а сигналы считывания на входы Выбор кристалла блока 13. Выход дешифра- тора 4 соединен с адресным регистром 5, выход которого соединен с адресным входом селектора 7, Выход дешифратора 4 соединен с входом информации регистра 2, вход синхронизации которого соединен с входом синхронизации адресного регистра 5 и с выходным сигналом Вх.синхр блока 12.

Регистр 2 адресов предназначен для запоминания адресов регистров устройства: дешифратор адреса формирует позиционный адрес и сигнал на линии УВ при адресах на шине 15, находящихся в диапазоне 16016-17652.

Адресный регистр 5 хранит адрес внешнего устройства.

Блоки 8,9 и 10 гальванической развязки содержат (фиг.З) оптроны 17, токоограничительные резисторы 18 и элементы НЕ 19. Блок 3 регистров данных состоит из регистров 20, формирователя 21 импульсов и элементы И-НЕ 22. Блок 13 регистров ввода содержит усилительные (буферные) элементы 23 и регистры 24.

Блок 11 внешних устройств (фиг.З) содержит регистры 25, устройства 26 индикации,устройство 27 ввода информации клавишного типа, испытательное и измерительное оборудование 28.

Блок 14 прерываний содержит (фиг. регистр 2У, триггеры 30, 31, элемент И 32, элемент И-НЕ 33, элемент НЕ 34

0

Q $ 0 5

5

0

5

0

5.

элемент ИЛИ 35, токоограничительный резистор 36.

Селектор 7 операций содержит (фиг. 5) элементы ИШ-НЕ 37, элементы ИЛИ 38, элемент Н-НЕ 39 и усилительные (буферные) элементы 40. Се- ле ктор 7 формирует сигналы записи Зп.О-Зп.З и считывания Сч.1-Сч.4 и общий сигнал Счит.1. Элементы ИЛИ-НЕ 37 и элемент 40 осуществляют одновременную запись в К регистров блока 11 .

Дешифратор 4 адреса содержит (фиг.5) элементы НЕ 41, элементы И-НЕ 42, элементы ИЛИ-НЕ 43 и элемент 44 дешифрации.

Устройство работает следующим образом.

Обмен информацией осуществляется по сигналам шин 15, 16.1 параллельным двоичным цифровым кодом под управлением внешнего процессора, подключенного к данному устройству.Каждый цикл обращения процессора состоит из 2 этапов: адресного и информационного (в рассматриваемом примере с совмещенными шинами 15 адреса и данных).

Вывод информации осуществляют за один цикл обращения процессора. При этом вывод одной и той же информации может быть осуществлен одновременно на несколько внешних устройств. Ввод информации также осуществляется за один цикл обращения.

Вывод информации из процессора на внешние устройства осуществляет- ci следующим образом.

Первая часть работы устройства начинается с этапа, когда процессор выставляет сигналы Адрес 1 на шине 15 (фиг.1 и 2), которые через блок 1 поступают на дешифратор 4 (старшие разряды адреса) и на ре- , гнстр 2 адресов (младшие разряды адреса). Одновременно процессор вырабатывает на шине 16.1 сигнал Вх. счнхр., который через усилители блока 12 поступает на управляющие входы регистров 2 и 5. По сигналу происходит запись младших разрядов Адрес 1 в регистр 2 и сигнала Устройство выбрано УВ, поступающего в регистр 2 с выхода. Эти сигналы дешифруются дешифратором 4 и в виде одного из сигналов,соответствующего адресу одного из внешних устройств, поступает по шине п на вход адресно

514

го регистра 5. Сигнал УВ на выходе дешифратора 4 будет только в том случае, если старшие разряды сигнала Адрес 1 совпадут в дешифраторе 4 с сигналами, заранее установленными в нем. В этом случае на его выходах помимо сигнала УВ будет один из п сигналов внешних устройств, который поступает на вход адресного регистра и записывается в него с помощью сигнала Вх.синхр.

На втором этапе процессор выставляет на шине 15 сигналы Данные 1, которые поступают на вход информации регистра 3 данных через блок 1.После этого процессор вырабатывает на шине 16 сигнал Вывод, который чере блок 12 поступает на вход дешифратора 6 команд, на других входах которого уже имеются сигналы УВ и младшие разряды Адрес 1, т.е. адрес регистра. Из этих сигналов вырабатывается (дешифруется) один из сигналов Дт, который поступает на входы селектора 7. На другие входы селектора 7 поступает один из сигналов А,-Аи (адреса внешнего .устройства), который записан в регистр 5 в адресной части цикла обращения процессора.

Сигнал Дт стробирует (фиг.5) элемент ИЛИ-НЕ 37.

Если на его входе имеется сигнал (Лог.О) А,-Ап, то на выходе выра

батывается один из сигналов Запись ЗпО-ЗпЗ, который поступает на вход синхронизации (записи) регистра заданных и производит запись данных в этот регистр. Одновременно записанные данные по шине Д1 с выхода регистра 3 поступают непосредственно или через блок 10 на входы внешних устройств и записывается с помощью соответствующего сигнала ЗП, поступающего с выхода селектора 7.

Для внешних устройств 26.1 этот сигнал ЗП подается по шине Зп, а для устройств 26.2, требующих развязки, по шине ЗП.1 через блок 8 (фиг-.З).

Для регистров светодиодных индикаторов 26.2 (фиг.З) и других простейших внешних устройств запись информации производится без обращения к регистру 3 данных, а непосредственно с шины АД с помощью сигнала Зп.

5

0

5

0

5

0

5

0

5

Если во время обращения процессора, сигнал УВ с выхода дешифратора 4 равен нулю, никакие сигналы на входы внешних устройств не вырабатываются.

Режим ввода информации из внешних устройств в процессор осуществляется следующим образом.

На первом адресном этапе цикла на шине 15 процессором вырабатываются сигналы Адрес 2, старшие разряды которых через блок 1 посту- Л1ают в дешифратор 4, а младшие разряды на вход регистра 2 адресов. Одновременно на шине 16.1 вырабатывается сигнал Вх.синхр., по которому производится запись младших разрядов Адреса 2 (адрес регистра внешних устройств), выходного сигнала дешиф- ратора 4 УВ и одного из п сигналов адреса соответственно в регистры 2 и 5. Эти сигналы с выходов регистров 2 и 5 подаются на входы дешифратора 6 и селектора 7.

На втором этапе режима ввода процессор вырабатывает на шине 16.1 сигнал управления вводом, который через усилители приемников блока 12 поступает на вход дешифратора 6 команд, на выходах которого вырабатывается один из сигналов Ет (фиг.5), который подается на входы селектора 7. Сигнал Ет стробирует элемент И-.НЕ 39 и элементы ИЛИ 38. В результате на выходе элементов 38 и 39 имеются сигналы Счит.1 и один из сигналов Сч.1-Сч.4, на элемент ИЛИ 38 которого подан один из адресных сигналов в адресной части цикла ввод. Сигналы Сч.1-Сч.4, на элемент ИЛИ 38 которого подан один из адресных сигналов А,-Ап в адресной части . цикла ввод. Сигналы Сч.1-Сч.4 (фиг.З) подаются на входы Выбор кристалла (ВК) регистров 24 или элементов 23 блока 13, а сигнал Счит.1 - на вход управления блока 1 для перевода при-, емопередатчиков этого блока в режим передачи (ввода) информации в процессор. Информация на входы регистров 24 и буферных элементов 23 блока 13 поступает с выходов блока 9 и внешних устройств группы 11 (фиг.1) и стробируется сигналами Сч.1-Сч.4.

В конце циклов Вывод и Ввод процессора в дешифраторе 6 команд вырабатывается сигнал Вых.синхр (фиг.5), который передается через

блок 12 в процессор, сигнализируя об окончании цикла ввод или вывод.

Так как процессор работает не только в режиме Ввод и Вывод, но и в режиме прерываний программы уп- равления,то имеется необходимость в быстром (оперативном) отключении или включении отдельных внешних устройст (таким,например, как источники питания, регуляторы температурь в камере тепла или холода) и автоматического перехода на основную программу управления. Программа, которую процессор выполняет по требованию прерывания внешнего устройства, находящегося в аварийном режиме, называется вспомогательной. В этом случае за- действуется блок 14.

В случае, когда в испытательном оборудовании (фиг.З), например,один из источников питания вышел на аварийный режим работы, (т.е. его выходное напряжение питания возросло выше допустимого) срабатывает его защита, сигнал защиты по шине ДЗ устанавливает один из триггеров регистра 30 блока 14 (фиг.4), вырабатывает на его инверсном выходе сигнал низкого уровня (запрос на прерывание),который подается на входы элемента ИЛИ 35. На другой его вход подается сигнал разрешения также низкого уровня с выхода регистра 29, который был записан в него с помощью цикла Вывод ранее. Если эти сигналы совпадают, на выходе элемента ИЛИ 35 образуется сигнал низкого уровня, который инвертируется с помощью элемента И-НЕ 33.1 и подается на вход записи триггера 31.1 и на вход элемента И 32.1. Таким образом,в триггер 31.1 производится запись сигнала требования прерывания, который через элемент И 32.1 подается на вход передатчика блока 12 и с его выхода на пину управления 16 в виде сигнала (ТПР) (фиг.26).

Процессор, принявший сигнал ТПР (низкого уровня), заканчивает текущий цикл основной своей программы, которую он выполнял и вырабатывает на шине 16.1 сигнал Ввод, который принимается приемником блока 12 и с его выхода подается в триггер 31.2 где производит запись высокого уровня.

Сигнал разрешения инверсного выхо да триггера 31.2 разрешает прием

последующего сигнала с помощью элемента И 32.2. После этого процессор вырабатывает сигнал ППР1, на шине 16, который принимается (фиг.4) приемником блока 12 и который будет принят элементом И-НЕ 33.2 и с его выхода в виде сигнала низкого уровня произведет сброс триггера 31.1 сброс реQ гистра 30 и поступит на входы передатчиков блока 12, которые выработают сигналы Вых.синхр. и Век.А. Сигнал Век.А передается передатчиками с открытым коллектором в виде

5 трех разрядного параллельного двоичного цифрового кода, который поступает на шину 15 процессора. Процессор принимает этот сигнал Век.А как адресный сигнал, для перехода

0 на вспомогательную подпрограмму обслуживания прерывания (т.е. аварийного режима источника питания). По этому адресу (Век.А) в ОЗУ процессора имеется начало вспомогательной

5 программы обслуживания прерывания. После выполнения процессором вспомогательной программы обслуживания прерывания процессор возвращается на основную свою программу, которую он вы-

0 полнил до запроса источника питания на прерывание. Регистр 30 блока 14 прерываний может принимать п 8 16 и т.д. запросов на прерывание. Приоритет этих запросов программным путем с помощью регистра 29. Если этот регистр 29 сбрасывается с помощью сигнала УСТ (сброса) через элемент И 32.3 или в него с помощью цикла Вывод записываются низкие

с. уровни, то запрос на прерывание игнорируется, т.е. не выполняется.

Блок 14 прерываний позволяет дополнительно контролировать п внешних устройств.

Сигнал Вых.синхр. блока 14 прерываний полностью аналогичен сигналу Вых.синхр., вырабатываемому устройством при циклах Вывод и Ввод. Эти сигналы суммируются по схеме монтажное ИЛИ в блоке 12 с помощью

0 схем передатчиков с открытым коллектором. Формула изобретения

Устройство для обмена информацией, 5 содержащее первый и второй блоки гальванической развязки, группы выходов которых являются соответствующими группами выходов устройства для

5

5

Подключения к первым синхронизирующим и первым информационным входам внешних устройств, третий блок гальванической развязки, группа входов которого является входом устройства для подключения к первым информационным выходам внешних устройств, регистр данных, дешифратор адреса и регистр адресов, группы информацион- ных входов которых подключены к группе выходов блока приемопередатчиков, группа входов-выходов которого является группой входов-выходов устройства для подключения к адрес- но-информационной шине ЭВМ, и блок усилителей первые группа входов и группа выходов которого являются группами входов и выходов устройства для подключения соответственно к группам синхронизирующих выходов и входов ЭВМ, а вторая группа выходов и вход соединены соответственно с

ГРУППОЙ СИНХРОНИЗИРУЮЩИХ ВХОДОВ И

выходом дешифратора команд, о т л и- чающее.с я тем, что, с целью повышения пропускной способности устройства, в него введены адресный регистр, блок прерываний, селектор операций и блок регистров ввода,при- чем первая группа выходов селектора операций соединена с группой синхронизирующих входов регистра данных и группой входов первого блока гальванической развязки и является группой выходов устройства для подключения к вторым синхронизирующим входам внешних устройств, группа выходов регистра данных соединена с группой входов второго блока гальванической развязки, группа управляющих входов блока регистров ввода соединена с второй группой выходов селектора операций, группы адресных и информационных входов которого подключены соот- ветственно к группам выходов адресного регистра и дешифратора команд, группы информационных входов которых подключены соответственно к группам выходов дешифратора адреса и регистра адресов, синхронизирующий, информационный входы и выход которого соединены соответственно с выходом блока усилителей соединенным с син- хровходом адресного регистра, выходом дешифратора адреса и разрешающим входом дешифратора команд,группы синхронизирующих входов и выходов блока прерываний соединены соответственно с третьими группами выходов и входов блока усилителей, первый и второй выходы селектора операций соединены соответственно с входами разрешения блока прерываний и блока приемопередатчиков, группа информационных вхедов которого подключена к группе выходов блока регистров ввода-вывода, группа информационных входов которого соединена с группами выходов третьего блока гальванической развязки и группой выходов хода вектора блока прерываний, группой информационных входов подключенного к группе выходов блока приемопередатчиков, группа входов запроса прерывания блока прерываний и группа информационных входов блока регистров ввода-вывода являются соответствующими группами входов устройства для подключения к выходам запроса прерывания и вторым информационным выходам внешних устройств, группы выходов регистра данных и блока приемопередатчиков являются соответствующими выходами устройства для подключения к вторым и третьим информационным входам внешних устройств, четвертая группа выходов блока усилителей является группой выходов устройства для подключения к адресно- информационной шине ЭВМ.

пг,,-гт:;1 hbi+M

ff ГГ№ 7 4

-hS:

Ј Щ

|

|VW

tOk

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1985 |

|

SU1264196A1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 1989 |

|

RU2022344C1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство для отображения информации на матричном индикаторе | 1989 |

|

SU1783573A1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

Изобретение относится к вычислительной технике ,в частности, к средствам микропроцессорного управления и может быть использовано в автоматизированных системах управления обработки информации и измерительных системах с применением микропроцессоров и/или ЭВМ. ЦЕЛЬЮ ИЗОБРЕТЕНИЯ ЯВЛЯЕТСЯ ПОВЫШЕНИЕ ПРОПУСКНОЙ СПОСОБНОСТИ УСТРОЙСТВА ЗА СЧЕТ УВЕЛИЧЕНИЯ СКОРОСТИ ВЫПОЛНЕНИЯ СИСТЕМНЫХ ОПЕРАЦИЙ. УСТРОЙСТВО СОДЕРЖИТ БЛОК ПРИЕМОПЕРЕДАТЧИКОВ, РЕГИСТР АДРЕСОВ, РЕГИСТР ДАННЫХ, ДЕШИФРАТОР АДРЕСА, АДРЕСНЫЙ РЕГИСТР, ДЕШИФРАТОР КОМАНД, СЕЛЕКТОР ОПЕРАЦИЙ, ТРИ БЛОКА ГАЛЬВАНИЧЕСКОЙ РАЗВЯЗКИ, БЛОК УСИЛИТЕЛЕЙ, БЛОК РЕГИСТРОВ ВВОДА И БЛОК ПРЕРЫВАНИЙ. ОБМЕН ИНФОРМАЦИЕЙ ОСУЩЕСТВЛЯЕТСЯ ПОД УПРАВЛЕНИЕМ ПРОЦЕССОРА, КАЖДЫЙ ЦИКЛ ОБРАЩЕНИЯ КОТОРОГО СОСТОИТ ИЗ ДВУХ ЭТАПОВ: АДРЕСНОГО И ИНФОРМАЦИОННОГО. ВВОД И ВЫВОД ИНФОРМАЦИИ ОСУЩЕСТВЛЯЮТСЯ ЗА ОДИН ЦИКЛ ОБРАЩЕНИЯ ПРОЦЕССОРА. 7 ИЛ.

18Z18VI

( Начало 3

примяты код яо teca и вх. синхр. блоками 1 и /2

Заполнить коды адреса Внешнего устройства, 8 адресном регистре 5 и 8регистре адресов 2 ..

щрес бнешнеео Устройства совпадает с у/форма шеи на выходе Ьяокс

Выработать сигнал УВ S дешифраторе адреса и запомнить адрес внешнеео устройства и его регистра S адресном регистре 5 и регистре адресов

Выбирать сигналы йых синхр. и ЗП1 ЗПИ

Перевести приемопередатчики 8 рб- яим передачи

выработать cuttta- w вых. cutfxp- и счет J

Фиг. 6

Снять сигналы зт зпз и строй коммутатора 8

Снять с ив нал 8ш. синхр.

Сиенал Сч строб влл Клока регистров Mo fa 13

fttn

Снять сие- нал Сч ила строй коммутатора 3

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1985 |

|

SU1264196A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-09-25—Подача