(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

| Запоминающее устройство | 1983 |

|

SU1149316A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство с обнаружением многократных ошибок | 1982 |

|

SU1156143A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

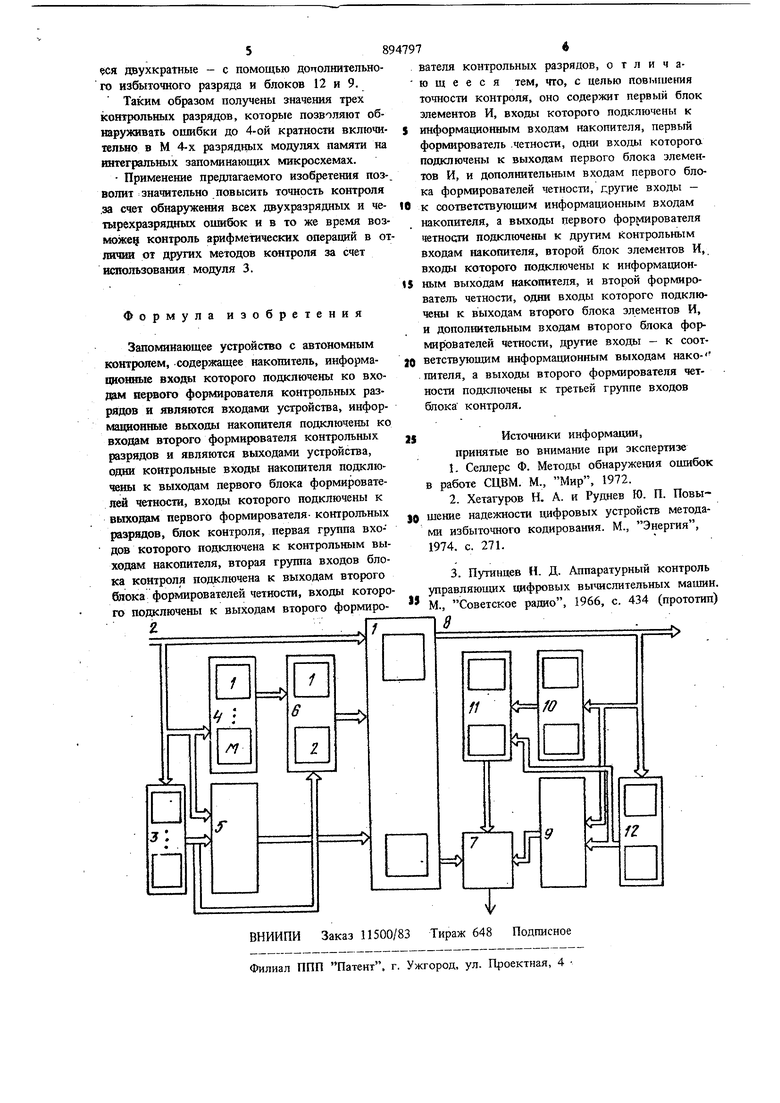

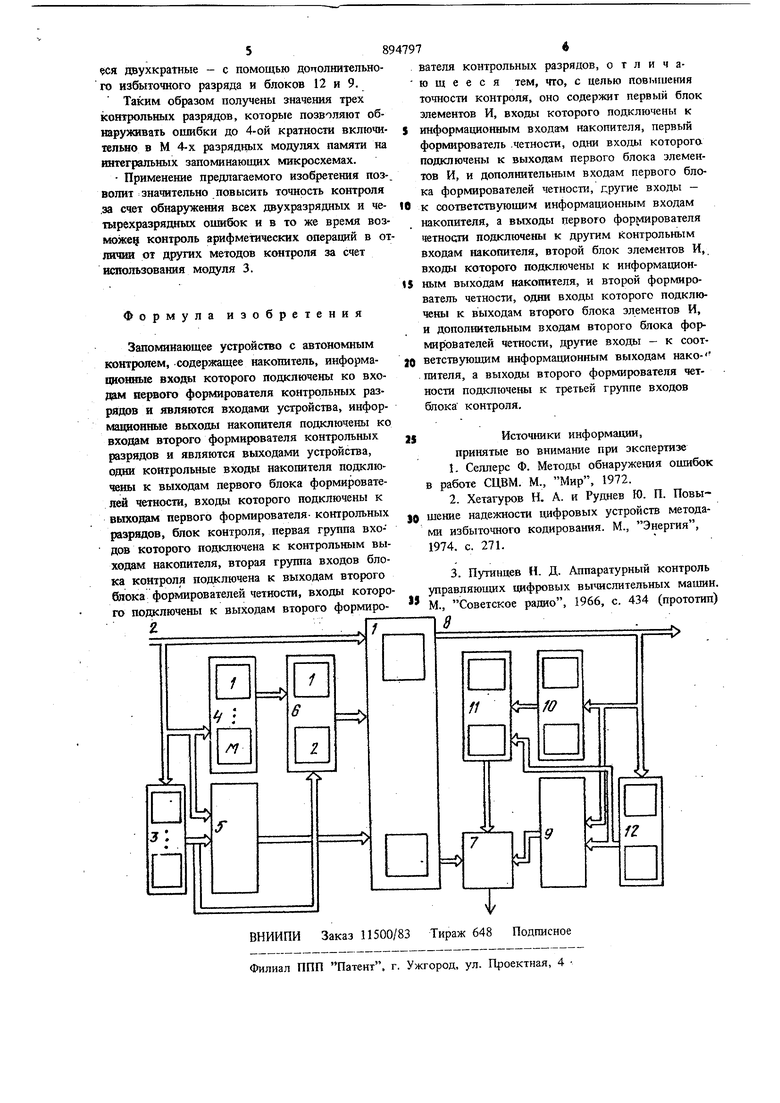

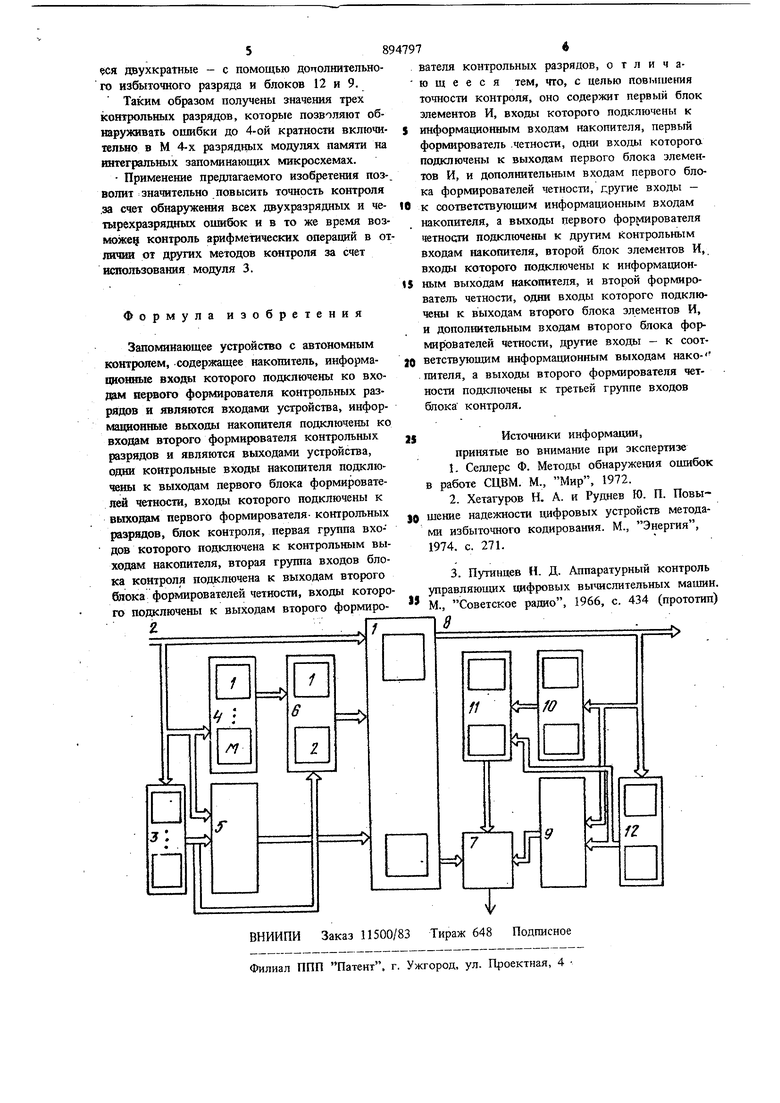

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам с модульной структурой и схемами обнаружения многократных ошибок. Известны запоминающие устройства с обнаружением ошибок и контролем арифметических операций на основе числового контроля по модулю 3, содержащие блок памяти с .модульной структурой, блоки формирования конт рольных разрядов по модулю 3, схемы выработки ошибки и обнаруживающие: 100% однократных и трехкратных ошибок, 33,3% двукратных и 0% четырехкратных, если оижбки носят ассиметричньш и детерминированньш характер 1. Известны запоминающие устройства с обна ружением ошибок на основе использования не кольких нечетных модулей и позволяющие исправлять однократные ошибки 21. Однако для реализашш обнаружения оши.бок требуется большая избыточность. Наиболее близким по технической сущности и схемному решению к предлагаемому является запоминающее устройство с автономным контролем, основанным на сочетании числового контроля по модулю 3 и по модулю 2, содержащее 4-разрядных модулей памяти, первый и второй блоки формирователей контрольных разрядов по модулю 3, схему выработки ошибки, первый и второй формирователи четности, входные и выходные числовые шины, при этом входы модулей памяти соединены со входными числовыми шинами, соединенными также со входами первого блока формирователей контрольных разрядов по модушо 3 и входами первого формирователя четности, входы которого соединены с модулями памяти, выходы модулей памяти соединены со схемой выработки ощибки и выходными числовыми шинами, соединенными также со вторым блоком формирователей контрольных разрядов по модулю 3 и вторым формирователем четности, выходы которого соединены со схемой обнаружения ошибки, соединенной также с выходом второго блока формирователей контрольных разрядов по модулю 3 3. Недостатком известного устройства является невозможность обнаружения всех двукратных и четырехкратных ошибок, возникающих при отказах в модульных запоминающих устройствах, т.е. недостаточная точность контроля. Цель изобретения - повышение точности контроля. Указанная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее накопитель, информационные входы которого подключены ко входам перво го формирователя контрольных разрядов и яв ляются входами устройства, информационные выходы накопителя подключены ко входам второго формирователя контрольных разрядов и являются выходами устройства, одни контрольные входы накопителя подключены к выходам первого блока формирователей четности входы которого подключены к выходам перво го формирователя контрольных разрядов, блок контроля, первая группа входов которого под ключена к контрольным выходам накопителя, вторая группа входов блока контроля подклю чена к выходам второго блока формирователей честности, входы которого подключены к выходам второго формирователя контрольных разрядов, дополнительно введены первый блок элементов И, входы которого подключены к информационным входам накопителя, первый формирователь четности, ощш входы которого подключены к выходам первого блока элемен тов И, и дополнительным входам первого бло ка формирователей четности, другие вдсоды - к соответствующим информационным входам накопителя,- а выходы первого формирователя четности подключены к другим конт рольным накопителям, второй блок элементов И, входы которого подключены к информационным выходам накопителя, и второй формирователь четности, одни входы которого подключены к выходам второго блока элементов И, и дополнительным входам второго блока формирователей четности, другие входы - к соответствующим информационным выходам накопителя, а выходы второго формирователя четнос ти подключены к третьей группе входов блока контроля. На чертеже представлена блок-схема предлагаемого запоминающего устройства с автоном ным контролем. Устройство содержит накопитель 1, состоящий из М 4-х разрядных модулей памяти, числовые пшны 2, первый блок 3 элементов И первый формирователь 4 контрольных разрядов, первый формирователь 5 четности, соединенными также с выходами, первый блок 6 формирователей четности , блок 7 контроля, информащ1онные выходы 8, второй формирователь 9 четности, второй формирователь 10 контрольных разрядов, второй блок 11 форми рователей четности, а также второй блок 12 элементов И. Устройство работает следующим образом. Коды чисел, подлежащих записи в очередном цикле записи, поступают на входы накопителя 1, а также на входы первого формирователя 4 контрольных разрядов по модулю 3 и входы первого блока 3 элементов И. Блок 4 содержит М формирователей контрольных разрядов по модулю 3, каждый из которых определяет вычет своего 4-х разрядного модуля памяти. Блок 3 элементов И состоит из М элементов И и вырабатывает признаки коньюнкции для тех же модулей памяти. В первом блоке формирователей четности формируется два признака четности для всех М групп, получаемых в блоке 4 вычетов по модулю 3. При этом один из формирователей вырабатывает признак четности для разрядов с весом единица, а рруток - для разрядов с весом двойка. Ползд1енные таким образом два контрольных разряда (вычет, по модулю 3) записываются в два контрольных разряда. Это позволяет обнаруживать со 100% вероятностью однократные и трехкратные опшбки,33,3% всех двухкратных и 0% четырехкратнэ1Х. Необнаруживаемыми остаются двухразрядные и четырехразрядные оишбки, вычет которых равен 3. Чтобы выявить эти ошибки необходимо ввести третий контрольный разряд и определить его значение как (а IЛ 32 Л 3 Л 34 ) 1 мод 3 + 11 К-3 + 34 + ( Аз|-Лз4) мод2, где а, 82, Зз, - первый, второй, третий и четвертый информационные разряды в каждой группе из 4-х разрядов каждого модуля памяти. Коньюнкцию выполняют элементы И из блока 3 (по одной схеме на каждый из М модулей памяти), а формирование признака четности для каждых первого, третьего (второго, четвертого) разряда и коньюнкция производится в формирователе 5 четности, после чего полученное значение записьтается в третий контрольный разряд. В режиме считывания информации коды считьшаемых чисел поступают в выходную числовую пшну, а контрольные разряды поступают на блок 7 контроля. Аналогично работе блоков 3-6 в блоках 12, 10, 9 н И производится выработка 3-х контрольных разрядов из кодов считанных чисел, которые поступают в блок 7 контроля. При этом одноразрядные, трехразрядные и часть двухраэрядных ошибок обнаруживаются с помощью вычета по числовому модулю 3, а четырехкратные и оставщи ся двухкратные - с помощью дополнительного избыточного разряда и блоков 12 и 9. Таким образом получены значения трех контрольных разрядов, которые позволяют обнаруживать ошибки до 4-ой кратности включительно в М 4-х разрядных модулях памяти на интегральных запоминающих микросхемах.

Применение предлагаемого изобретения поз-, вояит : значительно повысить точность контроля .за счет обнаружения всех двухразрядных и четырехразрядных ошибок и в то же время возможе контроль арифметических операций в отли вга от яруткх методов контроля за счет использования модуля 3.

Формула изобретения

Запоминающее устройство с автономным контролем, содержащее накопитель, информационные входы которого подключены ко входам первого формирователя контрольных разрядов и являются входами устройства, информационные выходы накопителя подключены ко входам второго формирователя контрольных разрядов и являются выходами устройства, одни контрольные входы накопителя подключены к выходам первого блока формирователей четности, входы которого подключены к выходам первого формирователя- контрольных разрядов, блок контроля, первая группа входов которого подключена к контрольным выходам накопителя, вторая группа входов блока контроля подключена к выходам второго блока формирователей четности, входы которого подключены к выходам второго формирователя контрольных разрядов, с т л и ч аю щ е е с я тем, что, с целью повышения точности контроля, оно содержит первый блок элементов И, входы которого подключены к

информационным входам накопителя, первый формирователь .четности, одни входы которого подключены к выходам первого блока элементов И, и дополнительным входам первого блока формирователей четности, другие входы -

к соответствующим информационным входам накопителя, а выходы первого формирователя четности подключены к другим контрольным входам накопителя, второй блок элементов И, входы которого подключены к информационным выходам накопителя, и второй формирователь четности, одни входы которого подключены к выходам второго блока элементов И, и дополнительным входам второго блока формирювателей четности, другие входах - к соответствующим информационным выходам нако- пителя, а выходы второго формирователя четности подключеШ) к третьей группе входов блока контроля.

Источники информации,

принятые во внимание при экспертизе

19 М., Советское радио, 1966, с. 434 (прототип)

О

Авторы

Даты

1981-12-30—Публикация

1980-04-04—Подача