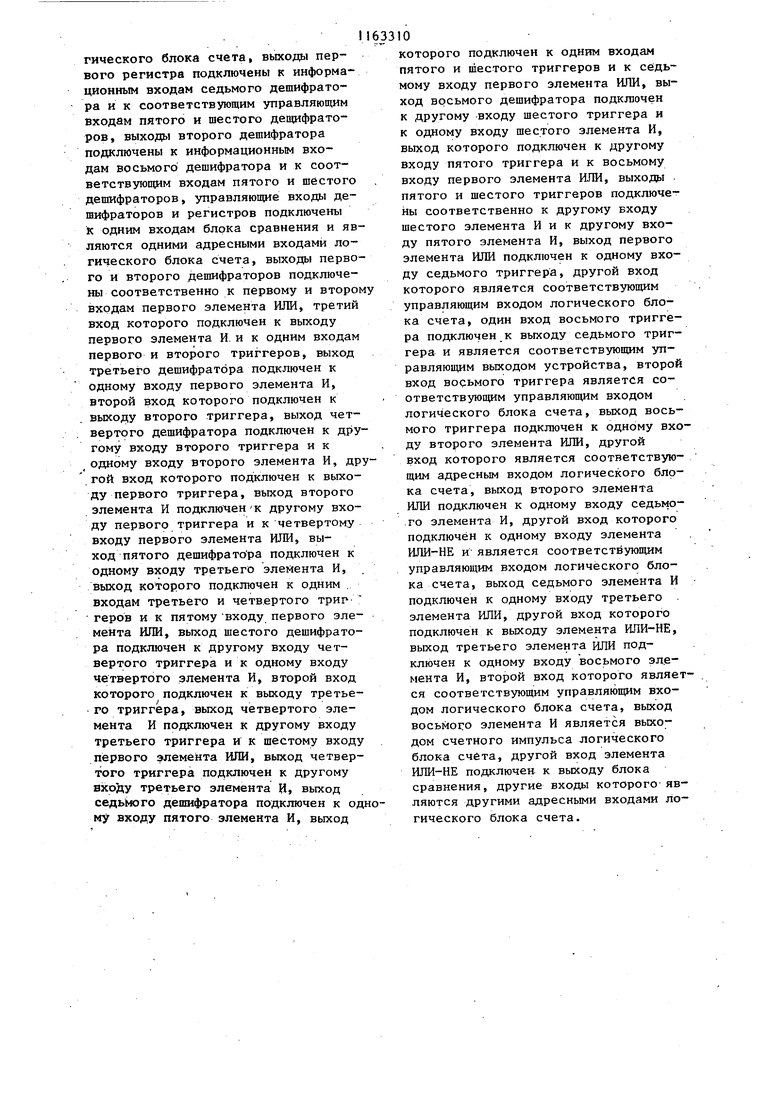

гического блока счета, выходы первого регистра подключены к информационным входам седьмого дешифратора и к соответствующим управляющим входам пятого и шестого дешифраторов, выходы второго дешифратора подключены к информационным входам восьмого дешифратора и к соответствующим входам пятого и шестого дешифраторов, управляющие входы дешифраторов и регистров подключены к одним входам блока сравнения и являются одними адресными входами логического блока счета, выходы первого и второго дешифраторов подключены соответственно к первому и второ входам первого элемента ИЛИ, третий вход которого подключен к выходу первого элемента И. и к одним входам первого и второго триггеров, выход третьего дешифратора подключен к одному входу первого элемента И, второй вход которого подключен к выходу второго триггера, выход четвертого дешифратора подключен к другому входу второго триггера и к одному входу второго элемента И, дргой вход которого подключен к выходу первого триггера, выход второго элемента И подключенк другому входу первого триггера и к четвертому входу первого элемента ИЛИ, выход пятого дешифратора подключен к одному входу третьего элемента И, выход которого подключен к одним входам третьего и четвертого триг геров и к пятому входу первого элемента ШШ, выход шестого дешифратора подключен к другому входу четвертого триггера и к одному входу четвертого элемента И, второй вход которого подключен к выходу третьего триггера, выход четвертого элемента И подключен к другому входу третьего триггера и к шестому входу первого элемента ИЛИ, выход четвертого триггера подключен к другому входу третьего элемента И, выход седьмого дешифратора подключен к одму входу пятого элемента И, выход

10

которого подключен к одним входам пятого и шестого триггеров и к седьмому входу первого элемента ИЛИ, выход восьмого дешифратора подключен к другому входу шестого триггера и к одному входу шестого элемента И, выход которого подключен к другому ВХОДУ пятого триггера и к восьмому входу первого элемента ИЛИ, выходы пятого и шестого триггеров подключены соответственно к другому входу шестого элемента И и к другому входу пятого элемента И, выход первого элемента ИЛИ подключен к одному входу седьмого триггера, другой вход которого является соответствующим управляющим входом логического блока счета, один вход восьмого триггера подключен к выходу седьмого триггера и является соответствующим управляющим выходом устройства, второй вход восьмого триггера является соответствующим управляющим входом логического блока счета, выход восьмого триггера подключен к одному входу второго элемента ИЛИ, другой вход которого является соответствующим адресным входом логического блока счета, выход второго элемента ИЛИ подключен к одному входу седьмо-го элемента И, другой вход которого подключён к одному входу элемента ИЛИ-НЕ и является соответствующим управляющим входом логического блока счета, выход седьмого элемента И подключен к одному входу третьего элемента ИЛИ, другой вход которого подключен к выходу элемента ИЛИ-НЕ, выход третьего элемента ИЛИ подключен к одному входу восьмого элемента И, второй вход которого является соответствующим управляющим входом логического блока счета, выход восьмого элемента И является выходом счетного импульса логического блока счета, другой вход элемента ИЛИ-НЕ подключен, к выходу блока сравнения, другие входь: которого-являются другими адресными входами логического блока счета.

11

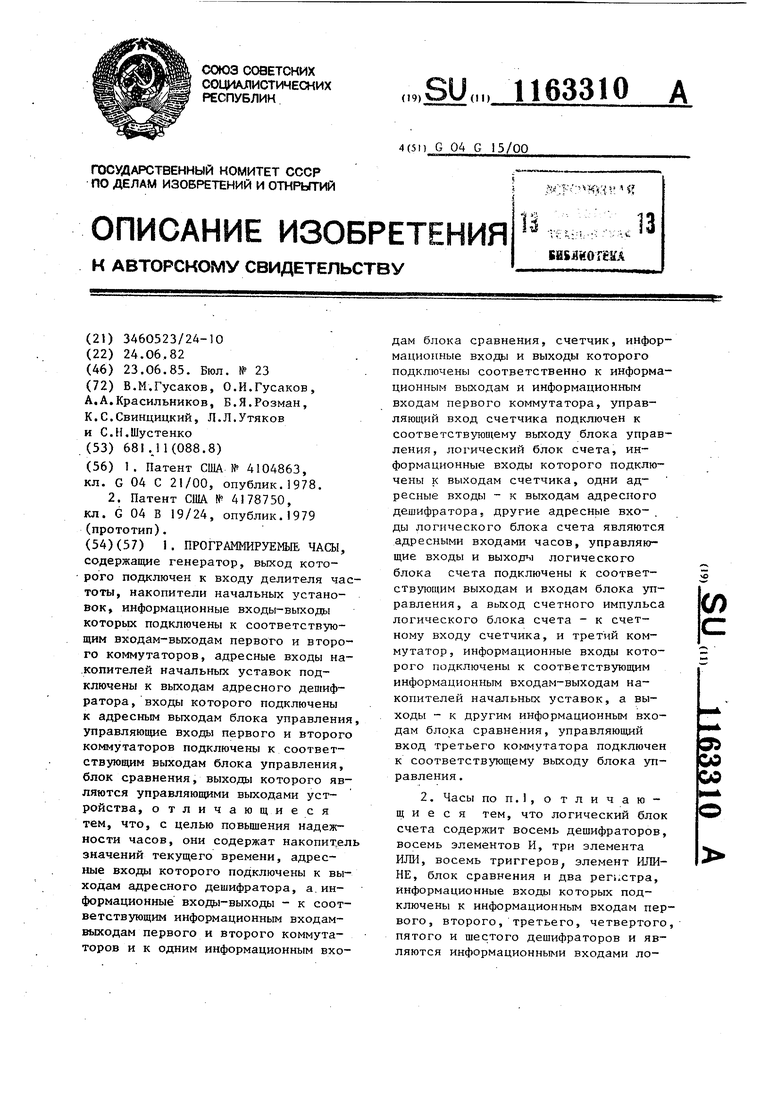

Изобретение относится к приборам измерения времени, а именно к электронным часам с программируемыми функциями.

Извест1ш электронные часы с устройством сигнализации, содержащие генератор, делитель частоты, счётчик текущего времени, схемы запоминания установленных счетчиков времени, схему совпадения и устройство выработки установленных сигналов. Сигналы от запоминающих схем и сигнал текущего времени поступают на схему совпадения. При совпадении этик сигналов на выходе появляется сигнал, который подается на вход устройства выработки установленного сигнала, например звукового сигнализатора, позволяющего aanporpaNMHpOBaTb работу часов путем занесения определенных значений начальных уставок в запо шнающие схемы l .

Недостатком таких часов является сложность из-за наличия большого числа счетчиков текущего времени и многоразрядной cxet-fbi сравнения.

Наиболее близкими по технической сущности к изобретению являются программируемые часы, содержащие генератор, делитель частоты, счетчик времени, счетчик календаря, блок сравнения, накопители начальньк уставок, элемент ИЛИ, буферный блок, мультиплексор блока индикации, блок индикации и блок-управления, причем выход генератора подключен к делителю частоты, с выхода которого сигнал поступает на последов.гтельно; соединенные счетчик времени и счетчик калеНдаря, которые и .производят отсчет текущего времени. Блок сравнения определяет момент совпадения тек пдего времени с начальными уставками, которые хранятся в накопителях, и при их совпадении вырабатб1вается сигнал, поступающий через буферный блок на вход устройства звуковой сигнализации. Мультиплексор позволяет в за- ; висимости от выбранного режима пот;- ключить к блоку индикации информацию о текущем времени либо о начальных уставках. Блок управления устройства осуществляет синхронизацию и управ ление работой блоков и узлов устройства, а также вырабатывает сигналы адресации к накопителям начальных уставок z .

33102

Недостатком известного устройства является его сложность из-за наличия большого числа счетчиков текущего времени, каждый триггер которых 5 требует больиого числа транзисторов, и многоразрядного блока сравнения. Кроне того, счетчики текущего времени предрасположены сбоям, что снижает надежность работы устройства.

Цель изобретения - упрйщение проrpavDv irjyeMbix часов и повьшение их надс:г:ногти,

1остя.вяенная цель достигается тем, что програ - 1ируемые часы, содержащие генаратор, выход которого подклю чен к входу делителя частоты, накопители начальных уставок, информацион- ные входы-выходы которых подключены к соответствующим информационным

входа - -выходам первого и второго коммутаторов,, адресные входы накопителей начальных уставок подключены к вькодам адресного дещифратора, входы которого подключены к адресным выходам блока управления, управляющие входы .первого и второго коммутаторов подключены к соответствующим выходам блока управления, блок сравнения , выходы которого являются уп0 равллющими выходами устройства, до- полг ительно содержит накопитель значений текущего времени, адреснЬю входы которого подключены к выходам адресного дешифратора, а информаци5 онные входы-выходы к соответствующим информационным входам-выходам первого и второго коммутаторов и к одним информационным входам блока сравнения, счетчик, информационные

0 входы и выходы которого подключены

соответственно к информационным выходаь и информационным входам первого коммутатора, управляющрпЧ вход счетчика подключен к соответствующему

5 выходу блока управления, логический блок счета, информационные входы которого пЪдключены к выходам счетчика, одни адресные входы - к вы-. ходам адресного дешифратора, другие

0 адресные входы логического блока счета являются адресными входами часов, управляющие входы и выходы логического блока счета подключены к соответств пощим выходам и входам

5 блока управления, а выход счетного импульса логического блока счета - к счетному входу счетчика, и третий коммутатор, информационные входы ко-toporo подключены к соответствующим информационным входам-выходам накопителей начальных уставок, а выходы к другим информационным входам блока сравнения, управляющий вход третьего коммутатора подключен к соответствующему выходу блока управления. Кроме того, логический блок Ьчета содержит восемь дешифраторов, восемь элементов И, три элемента ЩШ, восемь триггеров, элемент ИЛИ-НЕ, блок сравнения и два регистры, ин. формационные входы которых подключены к информационным входам первого, второго, третьего, -четвертого, пятого и шестого дешифраторов и являются информационными входами логи ческого блока счета, выходы первого регистра подключены к информационным входам седьмого дешифратора и к соответствующим входам пятого и шеетого дешифраторов, выходы второго де шифратора подключены к информационным входам восьмого дешифратора и к соответствующим управляющим входам пятого и шестого дешифраторов, управляющие входы дешифраторов и регистров подключены к одним входам блока сравнения-И являются одними адресными входами логического блока счета, выходы первого и второго дешифраторов подключены соответственно к первому и второму входам первого элемента ИЛИ, третий вход которого подключен к выходу первого элемента И,и к одним входам первого и второго триггеров, выход третьего дешифратора подключен к одному входу первого элемента И, второй вход которого подключен к выходу второго триггера, выход четвертого дешифратора подкгаочен к другому входу второго триггера и к одному входу второго элемента И, другой вход которого подключен к вьпсоду первого триггера, выход второго элемента И подключен к дру1ому входу пербого триггера и к четвертому входу первого элемента ИЛИ, выход пятого дешифратора подключен к одномув ходу третье го элемента И, выход которого подклю чен к одним входам третьего и четвертого триггеров и к пятому входу первого элемента ИЛИ, выход шестого дешифратора подключен к другому вхо ду четвертого триггера и к одному входу четвертого элемента И, второй вход которого подключен к выходу третьего триггера, выхоД четвертого элемента И подключен к другому входу третьего триггера и к шестому входу первого элемента ИЛИ, выход четвертого триггера подключен к другому входу третьего элемента И, выход седьмого дешифратора подключен к одному входу пятого элемента И, выход которого подключен к одним входам пятого и шестого триггеров и к седьмому входу первого элемента ИЛИ, выход восьмого дешифратора подключен к другому входу шестого триггера и к одному входу шестого элемента И, выход которого подключен к другому входу пятого триггера и к восьмому входу первого элемента ИЛИ, выходы пятого и шестого триггеров подключены соответственно к другому входу шестого элемента И и к другому входу пятого элемента И, выход первого элемента ИЛИ подключен к одному вхо- ду седьмого триггера, другой вход которого является соответствующим управляюш;им входом логического блока счета, один вход восьмого триггера подключен к выходу седьмого триггера и является соответствующим управляющим выходом устройства, второй вход восьмого триггера является соответствующим управляющим входом логического блока счета, выход восьмого триггера подключен к одному входу второго элемента ИЛИ, другой вход которого является соответствующим адресным- входом логического блока счета, выход второго элемента ИЛИ подключен к одному входу седьмого элемента И, другой вход которого под- ключей к одному входу элемента ИЛИНЕ и является соответствующим управляющим входом логического блока счета, выход седьмого элемента И подключен к одному входу третьего элемента ИЛИ, другой вход которого подключен к выходу элемента ШШ-НЕ, выход третьего элемента ИЛИ подключен к одному входу восьмого элемента И, второй вход которого является соответствующим управляющим входом логического блока счета, выход восьмого элемента И является выходом счетного импул:-са логического блока счета, другой вход элемента ИЛИ-НЕ подключен к выходу блока сравнения, другие входы которого являются другими адресными входами логического блока счета.

51

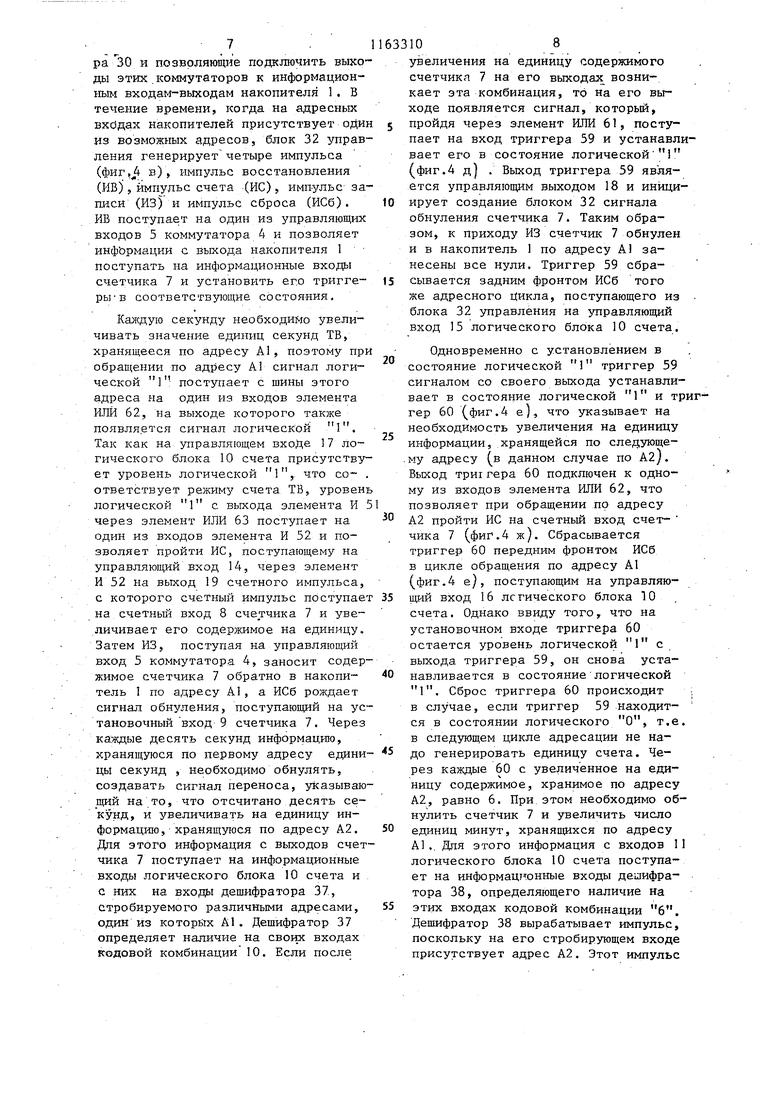

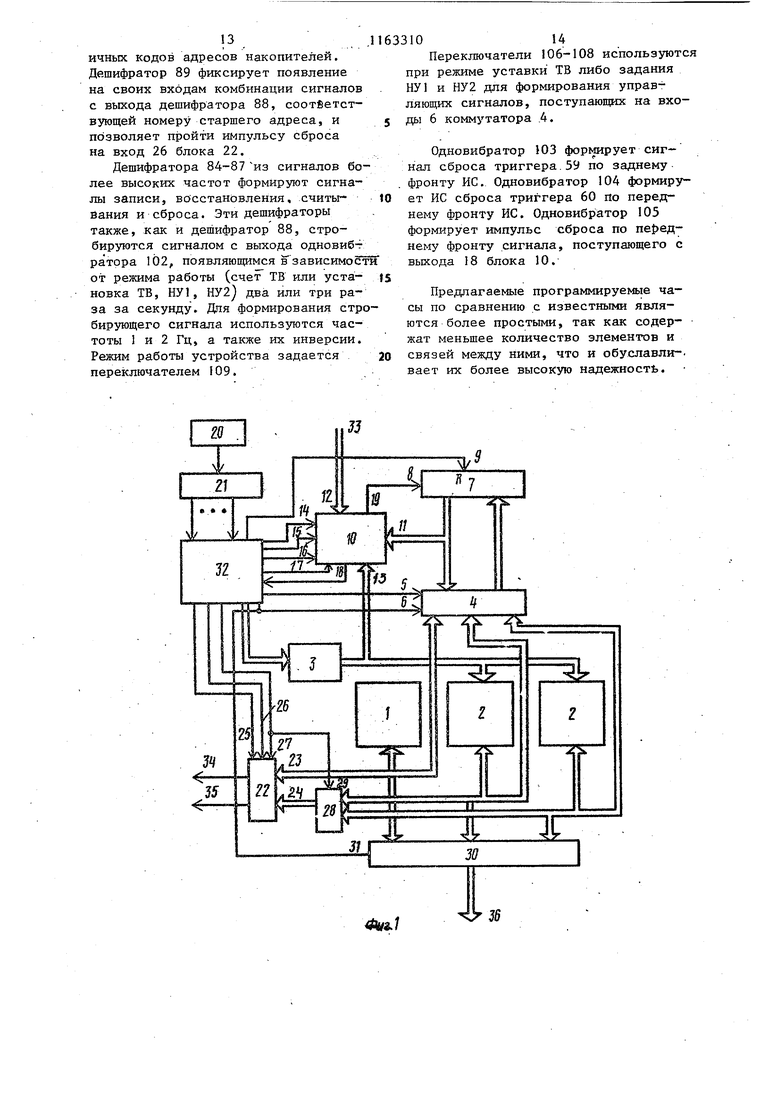

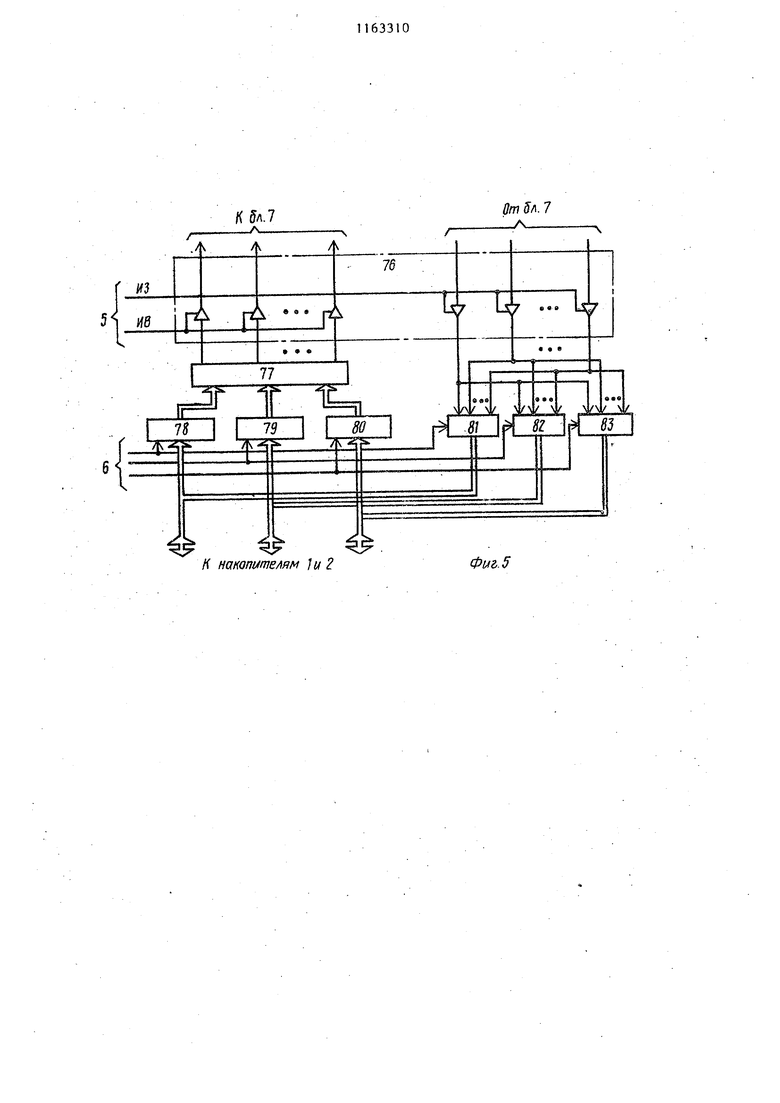

На фиг.1 представлена блок-схема программируемых часов; на фиг . 2 структурная схема логического блока счета; на фиг.З - структурная схема блока сравнения; на фиг.4 - вреMBHiibie диаграмм работы часов; на фиг.З структурная схема коммутатора; на фиг,6 - структурная схема блока упр.авления,

П{)ограммируемые часы содержат накопитель 1 значений текущего времени, накопители 2 начальньсх уставок, адресный дешифратор 3, первый коммутатор 4 с управляющими входами 5 и 6, счетчик 7 со счетнтй- 8 и 9 входами, логический блок 10 счета с информационными 11, адреспьпчи 12 и 13 и управляющими 14-17 входами, управляющим выходом 18 и выходом 19 счетного импульса, генератор 20, де- литель 21 частоты, блок 22 сравнения с информационными 23 и 24 и управляюп ми 25-27 входами, второй ко№-1утатор 28 с управляющим входом 29, третий коммутатор 30 с упрзвляюи,ими входами 31J блок 32 управления, а также адресные входы 33, управляющие выходы 34 и 35 и информационные выходы 36.

Логический блок 10 счета содержит дешифраторы 37-44, элементы И 45-52, триггеры 53-60, элементы ИЛИ 61-63, элемент ИЛИ-ИЕ 64, регистры 65 и 66 и блок 67 сравнения.

Блок 22 сравнения содержит злементы 68 сравнения, элементы И 69-7триггеры 72 и 73, счетчик 74 и дешифратор 75.

Коммутатор 4 содер--ит буферный блок 76, элемент ИЛИ 77, блоки 7883 вентилей. Блок 32 управления содержит дешифраторы 84-89, элементы И 90-95, элемент И-НЕ 96, элемент НЕ.97, элементы ИЛИ 98-101, одновибраторы 102-105,переключатели 106-1 0.

Основной режим работы програм1-1иру емых часов - режим счета текущего

;времени (ТВ. Б этом режиме происходят отсчет ТВ и выдачи его на выходы устройства для индикации. Одновременно происходит сравнение этого

отсчета с. запрограммированными начальными уставками (НУ и НУ2), хранящимися соответственно в первом и во втором накопителях 2 начальных уставок. При срабатывании блока 22 сравнения на выходе часов появляются управля1щие сигналы, которые мо6

гут ксппльзоваться внешними устройствами, например звуковым сигнализатс1)ом для организации будильника.

Кроме того, часы могут работать в pe)i;iM.e установки ТВ и программиро-яния НУ , При этом на вход уст ройсгв.л поступает информация об устаназл:1заемоь значении ТВ и НУ, заHocMcibi : в память часов, что позволяет зизуа.гптзировать процесс програм иг OiiaKi-TH .

Г; .е;. счета ТВ часы работают cne/i,:-:ji;:i м образом. Каждую блок 3/: управления формирует последова 1 е;.ьность управляющих и пульсон синхро: изт1р 1ощих работу всех узлоё. Для птого он использует импульсы, пос гуг аюиие с различной частотой с вытсодов делителя 21 частоты, которы делит частоту высокочастотного кварцевого геператора 20. В течение каждой секулды (фиг.) блок 32 травлеп;.я двалсды генерирует серию управлчющих импульсов. Первая серия на- 1инаегся по переднему фронту Секундной метки, а вторая - через О,25 с (фиг,4г) .

В каждой серии блок 32 управления вырабатывает ряд последовательных адресов, в данном случае от А1 до А10 (фиг.4,б), которые через адресный дешифратор 3 поступают на адресные входы накопителей Г и 2. Такиь: образом, происходит поеледо-. вательное обращение к информационньш словам, хранящимся в накопителя В каждом из накопителей хранится по десять для данного случая) информационных слов, которые либо определяют текущий временной отсчет (для накопителя l),.либо значения запрограммированных НУ (для накопителя 2) По первому адресу (А1) накопителей хранится значение единиц секунд, по второму (А2) - десятков секунд, по третьему (A3) - единиц минут, по четвертому (А4) - десятков минут по пятому (А5) - единиц часов, по шестому (А6) - десятков часов, по седьмому (А7-) - единиц датй, по восьмому (А8) - десятков даты, по девятому (А9) - единиц номера, месяца и по десятому (АЮ) - десятков номера месяца. Блок 32 управления вырабатывает сигналы, поступающие на управляющие входы 6 коммутатора 4 и на управляющие входы 3 коммутато- 7 . paЗО и позволяющие подключить выко ды этих.коммутаторов к информационным входам-выходам накопителя 1. В течение времени, когда на адресных входах накопителей присутствует оди из возможных адресов, блок 32 управ ления генерирует четыре импульса (фиг,4 в), импульс восстановления (ИВ), импульс счета (ИС) , импульс за писи (ИЗ) и импульс сброса (ИСб). ИВ поступает на один из управляющих входов 5 коммутатора 4 и позволяет информации с выхода накопителя 1 поступать на информационные входы счетчика 7 и установить его триггеры -в соответствующие состояния, Кансдую секунду необходимо увеличивать значение единиц секунд ТВ, хранящееся по адресу А1, поэтому пр обращении по адресу А1 сигнал логической 1 поступает с шины этого адреса на один из входов элемента ИЛИ 62, на выходе которого также появляется сигнал логической 1. Так как на управляющем вхоДе 17 логического блока 10 счета присутству ет уровень логической 1,. что соответствует режиму счета ТВ, уровен логической 1 с выхода элемента И через элемент ИЛИ 63 поступает на один из входов элемента И 52 и позволяет пройти ИС, поступающему на управляющий вход 14, через элемент И 52 на выход 19 счетного импульса, с которого счетный импульс поступае на счетньш вход 8 счетчика 7 и увеличивает его содержимое на единицу. Затем ИЗ, поступая на управляюпщй вход 5 коммутатора 4, заносит содер жимое счетчика 7 обратно в накопитель 1 по адресу А1, а ИСб рождает сигнал обнуления, поступающий на ус тановочный вход 9 счетчика 7. Через каждые десять секунд информацию, хранящуюся по первому адресу едини цы секунд , необходимо обнулять, создавать сигнал переноса, указываю щий на то, что отсчитано десять секунд, и увеличивать на единицу информацию , хранящуюся по адресу А2. Для этого информация с выходов счет чика 7 поступает на информационные входы логического блока 10 счета и с них на входы дешифратора 37, стробируемого различными адресами, один из которых А1. Дешифратор 37 определяет наличие на своих входах кодовой комбинации 10. Если после 108 увеличения на единицу содержимого счетчика 7 на его выходах возникает эта комбинация, то на его выходе появляется сигнал, который, пройдя через элемент ИЛИ 61, посту пает на вход триггера 59 и устанавливает его в состояние логической (фиг.4 д . Выход триггера 59 является управляющим выходом 18 и инйциирует создание блоком 32 сигнала обнуления счетчика 7. Таким образом, к приходу ИЗ счетчик 7 обнулен и в накопитель 1 по адресу А1 занесены все нули. Триггер 59 сбрасывается задним фронтом ИСб того же адресного Цикла, поступающего из . блока 32 управления на управляющий вход 15 логического блока 10 счета. Одновременно с установлением в состояние логической 1 триггер 59 сигналом со своего выхода устанавливает в состояние логической 1 и триггер 60 (фиг.4 е), что указывает на необходимость увеличения на единицу информации, хранящейся по следующему адресу (в данном случае по А2). Выход триг гера 60 подключен к одному из входов элемента ИЛИ 62, что позволяет при обращении по адресу А2 пройти ИС на счетный вход счетчика 7 (фиг.4 ж). Сбрасывается триггер 60 передним фронтом ИСб в цикле обращения по адресу А1 (фиг.4 е), поступающим на управляющий вход 16 логического блока 10 счета. Однако ввиду того, что на установочном входе триггера 60 остается уровень логической 1 с выхода триггера 59, он снова устанавливается в состояние логической 1. Сброс триггера 60 происходит :. в случае, если триггер 59 находится в состоянии логического О, т.е. в следующем цикле адресации не надо генерировать единицу счета. Через каждые 60 с увеличенное на единицу содержимое, хранимое по адресу А2, равно 6, При этом необходимо обнулить счетчик 7 и увеличить число единиц минут, хранящихся по адресу А1 .. Для этого информация с входов 11 логического блока 10 счета поступает на информационные входы дешифратора 38, определяющего наличие на этих входах кодовой комбинации 6. Дешифратор 38 вырабатывает импульс поскольку на его стробирующем входе присутствует адрес А2. Этот импульс через элемент ИЛИ 61 поступает на вход триггера 59 и устанавливает на его выходе уровень логической 1 Дальнейшая работа устройства аналогична как и при обращении по адресу А1. Таким же образом дешифратор 37 используется для коррекции значений единиц минут (A3), единиц часов (ЛЗ единиц числа (А7) и единиц номера месяца (А9 ), а дешифратор , 38 - для коррекции десятков минут (А4). Особый случай занимает коррекция значения 24 часов. При этом необходимо обнулить информацию по адресам А5 и А6. Это достигается следующим образом, При возникновении кодовой комбинац1 и 2 при обращени по адресу А6 дешифратор 40 устанав вает триггер 54 в состояние логичес кой 1. Сигнал с выхода этого триг гера позволяет в свою очередь пройт через элемент И 45 и элемент ИЛИ 61 на установочный вход триггера 59 сигналу с выхода дешифратора 39 при появлении на его информационных вхо дах кодовой комбинации 4 и при на личии на его стробирующем входе, являющемся шиной адреса А5,. разрешающего уровня. Происходит обнулени значения единиц часов. Кроме того, сигнал с вькода элементов И 45 уста навливает триггер 53 и сбрасывает триггер 54. При этом уровень логиче кой 1 с выхода триггера 53 разрешает прохождение через элемент ИЛИ 61 на установочный вход триггера 59 импульсов с выхода дешифратора 40 при последующей адресации по адрасу А6, которым стробируется его работа, так как на информационных вхо дах дешифраторов присутствует кодовая комбинация 2. Это вызывает об нуление значения десятков часов. Кроме того, сигнал с выхода элемента И 46 сбрасывает триггер 53, тем самым подготавливая его к дальнейшей работе. I Коррекция, числа при появлении значений 29 не высокосный год), 31 и 32 проводится аналогичным образом с помощью дешифратора ц1, реализующего в зависимости от номера месяца и при обращении по адресу А на кодовые комбинации 9, и 2, и дешифратор 42, реагирующего в зависимости от ном,ера месяца и при обращении по адресу А8 на кодовые комбинаций 2 и 3. Значение номера месяца при этом поступает на управляющие входа этих дешифраторов с выходов регистров 65 и 66, причем в регистр 65 записываются едгницы номера месяца при обращении по адресу А9, а в регистр 66 десятки номера месяца при обращеНИИ по адресу А10. Триггер 57 фиксирует появление соответствующего значения десятков числа и позволяет обнулить значение единиц числа при появлении на выходе дешифратора 40 сигнал. Триггер 56 в свою очередь позволяет обнулить значение десятков . числа. . Для коррекции значения номера месяца, равного 13, используются дешифратор 43, реагирующий при обращении по адресу А9 на кодовую комбинацию 3,и дешифратор 44, реагирующий при обращении по адресу А10 на кодовую комбинацию 1. При этом триггер 58 фиксирует появление кодовой комбинации 1 десятков номера месяца и позволяет обнулить значение единиц номера месяца при появлении сигнала на выходе дешифратора 43. Триггер 57 в свою очередь позволяет обнулить значение десятков номера месяца. Одновременно со счетом ТВ, который происходит указанным способом, каждую секунду происходит сравнение значения ТВ с запрограммированными НУ. Так как в данном случае имеется два набора НУ (НУ1 и НУ2), сравнение проводится дважды: первый раз в начале каждой секунды, а второй раз через 0,25 с (фиг.4 б,в,г). При этом блок 32 управления дважды генерируют серию адресов и на выходах накопителей появляется информация, хранимая по этим адресам. С выходов накопителей 2 НУ информация поступает на входы коммутатора 28, на управляющий вход 29 которогр поступает сигнал, разрешающий прохождение на входы 24 блока 22 сравнения в первые 0,25 с от начала секзп днoй метки инфорг ации с аыхода одного накопителя 2, а во вторые 0,25 с - с выхода другогЪ накопителя 2 .4 г). На входы 23 блока 22 сравнени поступает информация с выхода накопителя 1 значе- ° НИИ ТВ. С входов 23 и 24 информация поступает на входы элементов 68

сравнения, на выходах которых при совпадении информации появляются сигналь) с уровнем логической 1. Эти сигналы поступают на входы элемента И 6, и на его выходе появляется импульс, поступающий на счетный вход счетчика 74, Если все десять информационных слов, хранящихся в накопителе 1, совпадают с десятью словами, хранящимися в соответствующем накопителе 2, то в счет,чике 74 будет код 10, который фиксируется дешифратором 75, на выходе которого появляется сигнал. Этот сигнал поступает либо через элемент И 70, либо через элемент И 71 в зависимости от уровня сигнала на управляющем входе 26 на вход либо триггера 72, либо триггера 73, которые фиксируют совпадение НУ с ТВ и выдают управляющие сигналы либо на выход 34, либо на выход 35. Эти сигналы могут использоваться в дальнейшем, например, для создания ,звуко вой индикадии. Сброс счетчика 74 про исходит ч конце каждой адресной серии импульсом, приходящим на вход 26 из блока 32 управления, а сброс триггеров 72 и 73 - импульсом приходящим на вход 25 Из блока 32 управлеНИН и инициируемым либо вручную, либо по истечении определенного времения, в зависимости от необходимости

В описываемом режиме счета ТВ на управляющие входы 31 коммутатора 3Q поступазот сигналы, позволяющие пропускать на выходы 36 информацию с выхода накопителя 1. ; Эта информация может быть использована для индикации ТВ.

Режим установки значений ТВ и . программирования НУ осуществляется следующим образом (фиг.4 и,к,л). Помимо двух адресных серий,- которые генерируются при режиме счета ТВ блок 32 управления генерирует третью серию, которая начинается через 0,5 с после второй серии. Первая адресная серия используется для счета ТВ и сравнения значения ТВ с первыми НУ1. Алгоритмы ра.&оты устройства в этом цикле аналогичны работе устройства в режиме счета ТВ.

Вторая адресная серия отличается от аналогичной серии в,режиме счета ТВ тем, что кроме сравнения значений ТВ с вторые ш НУ проводится установка содержимого соответствующего

накопителя, Дпя этого блок 32 управления подает на входы 6 коммутатора 4 управляющий сигнал и подключает входы-выходы накопителя к входам счетчика 7, а на управляющий вход 17 логического блока 10 счета уровень логического О, что отключает выход элемента И 52 от выхода 19 сченого импульса.

Изменение содержимого, хранящегося по какому-либо адресу, осуществляется с помощью адресных входов 33 на которых выставляется, например, вручную номер этого адреса. Это значение адреса пос-Тупает на входы 12 логического блока счета, а с нихна одни входы блока 67 сравнения, на другие входы которого поступает адрес, генерируемый блоком 32 управления. При совпадении значений адресов на выходе блока 67 сравнения появляется сигнал логического О, поступающий на один из входов элемента ИЛИ-НЕ 64, На выходе элемента ИЛИ-НЕ 64 появляется сигнал логической который, пройдя через- элемент ИЛИ 63, позволяет ИС пройти с входа 14 через элемент И 52 на выход 19 -счетного импульса и увеличить содержимое счетчика 7 на .единицу. .

Третья адресная серия вводится для того, чтобы повысить скорость установки ТВ и программировании НУ. При этом импульсы, изменяющие содержимое ячеек накопителя, поступают через 0,5 с, т.е. с частотой 2 Гц.

На управляющие входы 31 коммутатора 30 в этом режиме поступают сигналы, подключающие к.выходам 36 выходы соответствующего накопителя. Это-дает возможность контролировать установку TR либо программирование ну, например визуально и прерывать этот режим в необходимый момент времени.

Коммутатор 4 позволяет осуществлять двунаправленную передачу данных между счетчиком 7 и необходимым накопителем, определяемым сигналами на входах 6. Направление передачи определяется сигналами, поступающими на входы 5.

Для формирования управляющих сигналов блок 32 использует сетку частот с выхода делителя 21. Дешифратор 88 выделяет сигналы, представляющие собой последовательность дво-

ичных кодов адресов накопителей. Дешифратор 89 фиксирует появление на своих входам комбинации сигналов с выхода дешифратора 88, соотбетствующей номеру старшего адреса, и позволяет пройти импульсу сброса на вход 26 блока 22.

Дешифратора 84-87 из сигналов более высоких частот формируют сигналы записи, восстановления, считыВания и сброса. Эти дешифраторы также, как и дешифратор 88, стробируются сигналом с выхода одновиб-г ратора 102, появляющимся взависимост от режима работы (счет ТВ или уста новка ТВ, НУ1, НУ2) два или три раза за секунду. Для формирования стробирующего сигнала используются частоты 1 и 2 Гц, а также их инверсии. Режим работы устройства задается переключателем 109.

Переключатели 106-108 используютс при режиме уставки ТВ либо задания НУ1 и НУ2 для формирования управляющих сигналов, поступающих на входы 6 коммутатора .4.

Одновибратор ЮЗ формирует сигнал сброса триггера.59 по заднему фронту ИС. Одновибратор 104 формиру ет ИС сброса триггера 60 по переднему фронту ИС. Одновибратор 105 формирует импульс сброса по перецнему фронту сигнала, поступающего с выхода 18 блока 10.

Предлагаемые программируемьш часы по сравнению с известньпии являются более простыми, так как содержат меньшее количество элементов и связей между ними, что и обуславли-. вает их более высокую надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1758648A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

I. ПРОГРАММИРУЕМЫЕ ЧАСЫ, содержащие генератор, выход которого подключен к входу делителя частоты, накопители начальных установок, информационные входы-выходы которых подключены к соответствующим входам-выходам первого и второго коммутаторов, адресные входы на.копителей начальных уставок подключены к выходам адресного дешифратора, входы которого подключены к адресным выходам блока управления, управляющие входы первого и второго коммутаторов подключены к соответствующим выходам блока управления, блок сравнения, выходы которого являются управляющими выходами устройства, отличающиеся тем, что, с целью повышения надежности часов, они содержат накопит,ель значений текущего времени, адресные входы которого подключены к выходам адресного дешифратора, а. информационные входа-выходы - к соответствующим информационным входамвыходам первого и второго коммутаторов и к одним информационным входам блока сравнения, счетчик, информационные входы и выходы которого подключены соответственно к информационным выходам и информационным входам первого коммутатора, управляющий вход счетчика подключен к соответствуюп1ему выходу блока управления, логический блок счета, информационные входы которого подключены к выходам счетчика, одни адресные входы - к выходам адресного дешифратора, другие адресные вхо- . ды логического блока счета являются адресными входами часов, управляющие входы и выходы логического блока счета подключены к соответствующим выходам и входам блока упkn равления, а выход счетного импульса логического блока счета - к счетному входу счетчика, и третий коммутатор , информационные входы которого подключены к соответствующим информационным входам-выходам накопителей начальных уставок, а выходы - к другим информационным входам блока сравнения, управляющий вход третьего коммутатора подключен к соответствующему выходу блока управления. 2. Часы поп.1,отличающ и е с я тем, что логический блок счета содержит восемь дешифраторов, восемь элементов И, три элемента ИЛИ, восемь триггеров, элемент ИЛИНЕ, блок сравнения и два реПхСтра, информационные входь которых подключены к информационным входам первого, второго, третьего, четвертого, пятого и шестого дешифраторов и являются информационными входами ло

//

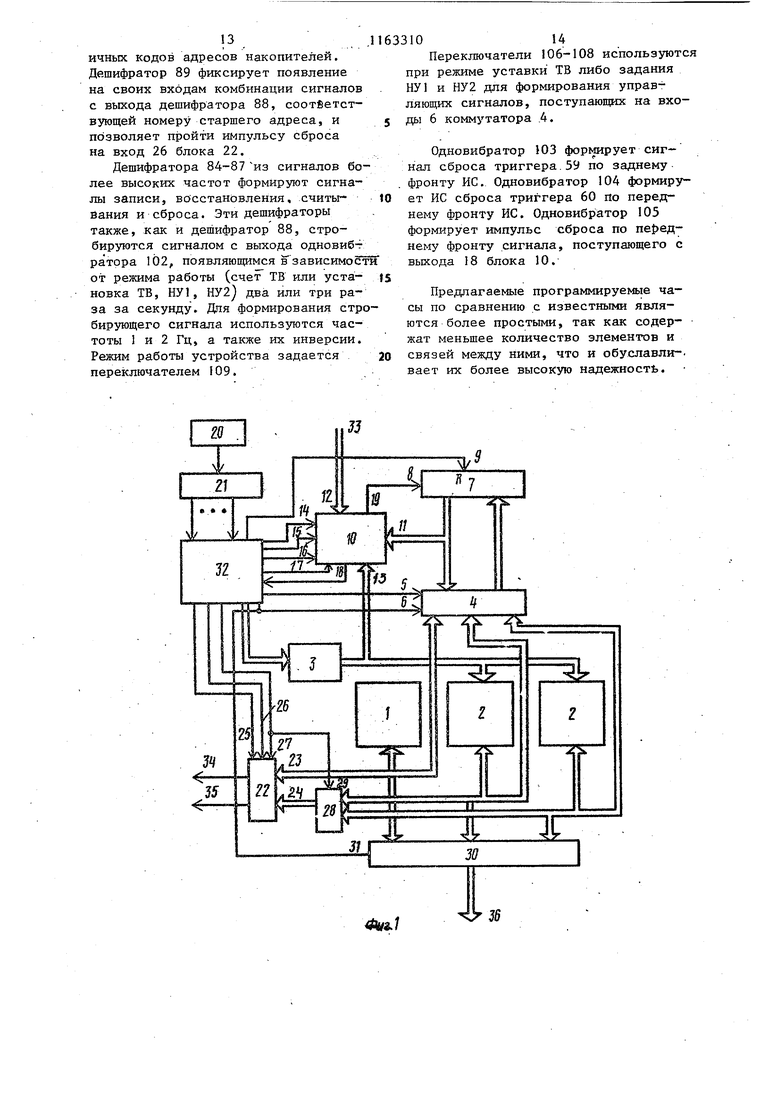

Фиг.З

/с накатите мм 1и 2

Фиг,. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4104863, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4178750, кл | |||

Авторы

Даты

1985-06-23—Публикация

1982-06-24—Подача