ел

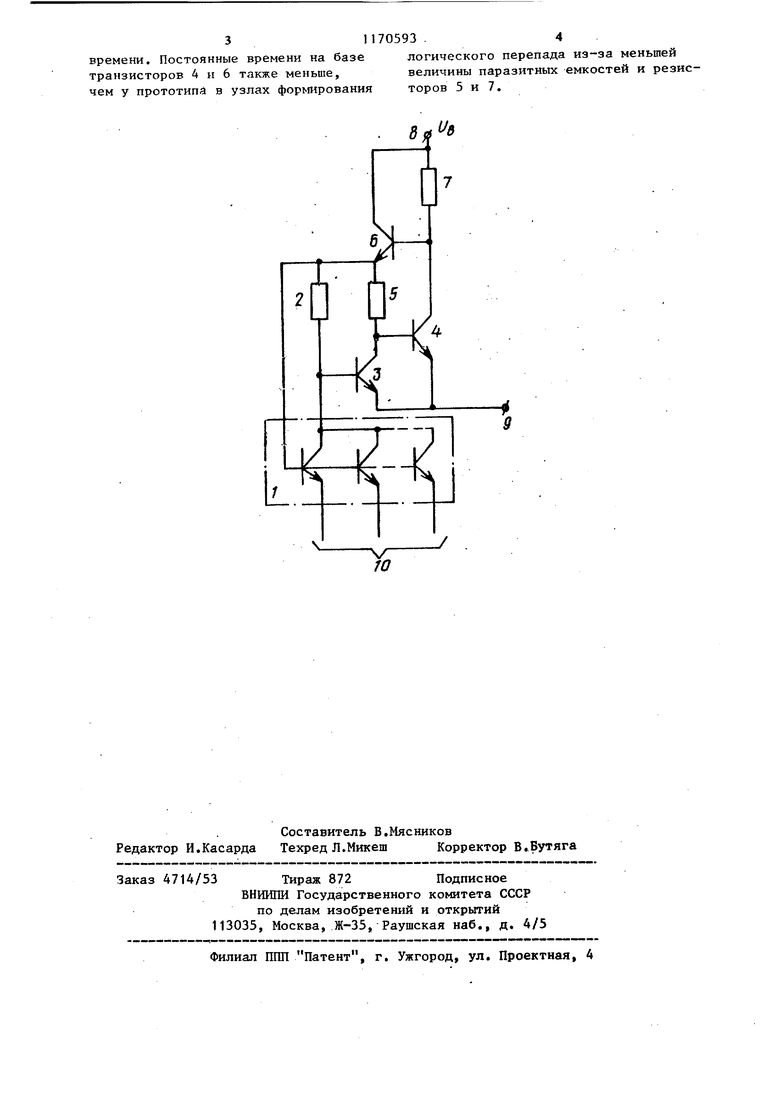

00 Изобретсние относится к вычислительной технике и может быть исполь зовано в качестве, элемента управления адресной шиной оперативного запоминающего устройства. Цель изобретения - увеличение быстродействия и уменьшение потребляемой мощности за счет уменьшения перепадов напряжений на элементах форм1-1рователя. На чертеже приведена прин1у1пиаль ная схема формирователя сигнала. Формирователь сигнала содержит п входных транзисторов 1, коллекторы которых соединены с. выводом входног резистора 2 и с базой первого транзистора 3, базы п входных транзисто ров соединены с вторым выводом вход ного резистора 2; второй транзистор 4, первьм резистор 5, а также третий транзистор 6 и второй резистор 7, причем базы п входных транзисторов 1 соединены с эмиттерами транзистора 6, которьш через первый резистор 5 соединен, с коллектором пер вого транзистора 3 и с базой второг транзистора 4, база третьего транзистора 6 соединена с коллектором второго транзистора 4 и через второй резистор 7 - с шиной 8 источни ка напряжения, с которой также соединен коллектор третьего транзистора 6, эмиттер первого транзистора 3 и э.миттер второго транзистора 4 сое динены с выходной шиной 9, выходами 10 формирователя сигнала являются эмиттеры п входных транзисторов 1. Формирователь сигнала работает следующим образом. Пусть на входы формирователя сиг нала подается такая комбинация логических сигналов, что все h входны транзисторов 1 закрыты, ток в их коллекторной цепи отсутствует и че.рез резистор 2 течет только базовый ток транзистора 3, вызванный прохож дением тока источника тока, подключенного к выходной шине 9, через эмиттер транзистора 3. За счет протекания коллекторного тока, транзистора 3 потенциал на баз транзистора 4 достаточно низкий и транзистор 4 закрыт. Через резистор 7 течет базовый ток транзистора 6. На эмиттере транзистора 6 сформирован высокий потенциал, который ниже .потенциала шины 8 на суммарную ве.личину падения напряжения на открыт переходе база-эмиттер транзистора 6 . и величину падения напряжения на резисторе 7, создаваемого за счет протекания базового тока транзистора 6. На шине 9 формирователя сигнала образован также высокий потенциал, который ниже потенциала общей шины па величину падения напряжения на открытых переходах база-эмиттер транзисторов 6 и 3 и величину падения напряжения на резисторах 7 и 2 за счет протекания базовых токов транзисторов 3 и 6. Если на входы формирователя сигнала подается такая комбинация логических сигналов, что ток протекает хотя бы в одном из п входных транзисторов 1, то за счет протекания коллекторного тока п входных транзисторов 1 в резисторе 2 потенциал на базе транзистора 3 понижается и ток В эмиттерной и ко.плекторной цепях транзистора 3 уменьшается. Потенциал на базе транзистора 4 за счет уменьшения тока в резисторе 5 повьш ается5 и транзистор 4 начинает проводить большой ток. Через его эмиттер проходит большая часть тока источника тока, подключенного к выходной шине 9. На выходе формирователя сигнала образуется низкий потенциал, который ниже потенциала на шине 8 на величину суммарного падения напряжения на резисторе 7 за счет протекания коллекторного тока транзистор. 4, падения напряжения на резисторе 5 ввиду протекания коллекторного тока транзисторов 3 и базового тока транзистора 4 и падений напряжений на переходе базагзмиттер транзисторов 4 и 6. В итоге логический перепад между состояниями выборки- и невыборки на выходной шине формирователя образует-, ся в основном на резисторе 7. В режиме переключения переход от низкого потенциала к высокому на базе транзистора 3 проходит быстрее из-за наличия указанной дополнительной цепи, так как большая часть логического перепада формируется на резисторе 7 за счет протекания тока источ- . кика тока, и только небольшая часть логического перепада формируется на резисторе 2, что дает возможность выбрать резистор 2 в 5-15 раз меньше, чем у прототипа, а это приводит к такому же уменьшению постоянной

31170593 .4

времени. Постоянные времени на базе логического перепада из-за меньшей транзисторов 4 и 6 также меньше, величины паразитных емкостей и резисчем у прототипа в узлах формирования торов 5 и 7.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигнала для выборки элементов матрицы | 1982 |

|

SU1045364A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Логический элемент | 1985 |

|

SU1285589A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| НЕСИММЕТРИЧНЫЙ ТРИГГЕР | 2020 |

|

RU2743452C1 |

ФОРМИРОВАТЕЛЬ СИГНАЛА, содержащий a входных транзисторов, коллекторы которых соединены с выводом входного резистора и с базой первого транзистора, базы /г входных транзисторов соединены с вторым выходом входного резистора, источник напряжения, отличающийся тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, в него введены второй и третий транзисторы и первьй и второй резисторы, причем базы ti входных транзисторов соединены с эмиттером третьего транзистора, который через первый резистор соединен с коллектором первого транзистора и с базой второго транзистора, база третьего транзистора соединена с коллектором второго транзистора и через второй резистор - с шиной источника наг1ряжения, с которой также соединен коллекi тор третьего транзистора, эмиттер (Л первого транзистора и змиттер второго транзистора соединены с выходной шиной.

| Способ сбора и удаления отходов из емкостей | 1986 |

|

SU1489861A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1985-07-30—Публикация

1983-10-06—Подача