Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки цифровой информации.

Целью изобретения является расширение функциональных возможностей суммирующего устройства за счет возможности определения количества единиц в двоичном коде.

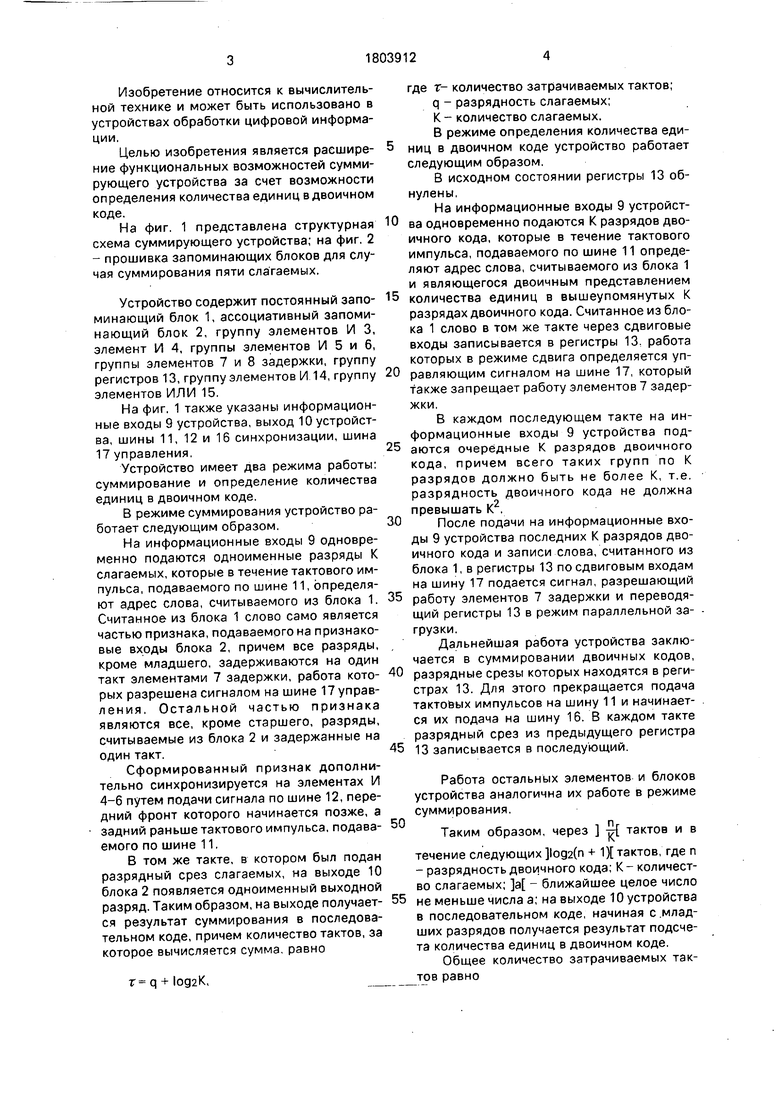

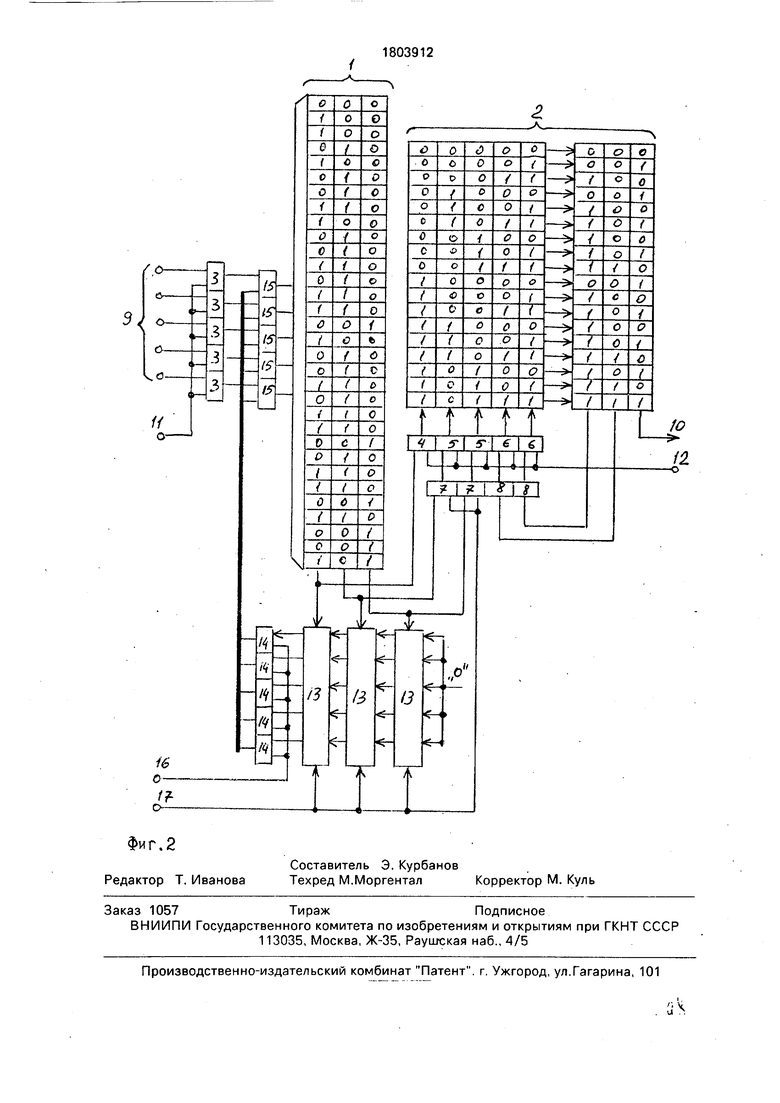

На фиг. 1 представлена структурная схема суммирующего устройства; на фиг. 2 - прошивка запоминающих блоков для случая суммирования пяти слагаемых.

Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, группу элементов И 3, элемент И 4, группы элементов И 5 и 6, группы элементов 7 и 8 задержки, группу регистров 13, группу элементов И 14, группу элементов ИЛИ 15.

На фиг. 1 также указаны информационные входы 9 устройства, выход 10 устройства, шины 11, 12 и 16 синхронизации, шина 17 управления.

Устройство имеет два режима работы: суммирование и определение количества единиц в двоичном коде.

В режиме суммирования устройство работает следующим образом.

На информационные входы 9 одновременно подаются одноименные разряды К слагаемых, которые в течение тактового импульса, подаваемого по шине 11, определяют адрес слова, считываемого из блока 1. Считанное из блока 1 слово само является частью признака, подаваемого на признаковые входы блока 2, причем все разряды, кроме младшего, задерживаются на один такт элементами 7 задержки, работа которых разрешена сигналом на шине 17 управления. Остальной частью признака являются все, кроме старшего, разряды, считываемые из блока 2 и задержанные на один такт.

Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи сигнала по шине 12, передний фронт которого начинается позже, а задний раньше тактового импульса, подаваемого по шине 11.

В том же такте, в котором был подан разрядный срез слагаемых, на выходе 10 блока 2 появляется одноименный выходной разряд. Таким образом, на выходе получается результат суммирования в последовательном коде, причем количество тактов, за которое вычисляется сумма, равно

+ log2K,

где т- количество затрачиваемых тактов; q - разрядность слагаемых; К - количество слагаемых. В режиме определения количества еди- 5 ниц в двоичном коде устройство работает следующим образом.

В исходном состоянии регистры 13 обнулены.

На информационные входы 9 устройства одновременно подаются К разрядов двоичного кода, которые в течение тактового импульса, подаваемого по шине 11 определяют адрес слова, считываемого из блока 1 и являющегося двоичным представлением

5 количества единиц в вышеупомянутых К разрядах двоичного кода. Считанное из блока 1 слово в том же такте через сдвиговые входы записывается в регистры 13, работа которых в режиме сдвига определяется уп0 равляющим сигналом на шине 17, который также запрещает работу элементов 7 задержки,

В каждом последующем такте на информационные входы 9 устройства под5 аются очередные К разрядов двоичного кода, причем всего таких групп по К разрядов должно быть не более К, т.е. разрядность двоичного кода не должна превышать К2.

0После подачи на информационные входы 9 устройства последних К разрядов двоичного кода и записи слова, считанного из блока 1, в регистры 13 по сдвиговым входам на шину 17 подается сигнал, разрешающий

5 работу элементов 7 задержки и переводящий регистры 13 в режим параллельной загрузки.

Дальнейшая работа устройства заключается в суммировании двоичных кодов,

0 разрядные срезы которых находятся в регистрах 13. Для этого прекращается подача тактовых импульсов на шину 11 и начинается их подача на шину 16. В каждом такте разрядный срез из предыдущего регистра

5 13 записывается в последующий.

Работа остальных элементов и блоков устройства аналогична их работе в режиме суммирования.

0п

Таким образом, через -гЛ. тактов и в

течение следующих 1одг(п + 1) тактов, где п - разрядность двоичного кода; К- количество слагаемых; а - ближайшее целое число 5 не меньше числа а; на выходе 10 устройства в последовательном коде, начиная с.младших разрядов получается результат подсчета количества единиц в двоичном коде.

Общее количество затрачиваемых тактов равно

}Ј + 1од2/п + 1Х.

Таким образом, предлагаемое устройство, кроме основной своей функции - суммирования, позволяет также определять количество единиц в двоичном коде, что значительно расширяет область применения устройства.

Формула изобретения

Суммирующее устройство, содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, первую и вторую группы элементов задержки, первую, вторую и третью группы элементов И и элемент И, причем первый разрядный выход ассоциативного запоминающего блока является выходом суммы устройства, остальные разрядные выходы ассоциативного запоминающего блока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первой шине синхронизации устройства, а выходы - к соответствующим входам опроса первой группы ассоциативного запоминающего блока, первые входы элементов И второй группы соединены соответственно с входами слагаемых устройства, а вторые входы - с второй шиной синхронизации устройства, первый разрядный выход постоянного запоминающего блока соединен с первым входом элемента И, второй вход которого подключен к первой шине синхронизации устройства, а выход соединен с входом опроса второй группы ассоциативного запоминающего

блока, остальные разрядные выходы постоянного запоминающего блока через соответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, вторые входы которых подключены к первой шине синхронизации устройства, выходы элементов И третьей группы соединены с соответствующими входами опроса третьей группы

ассоциативного запоминающего блока, о т- личающееся тем, что, с целью расширения функциональных возможностей путем определения количества единиц в двоичном коде, суммирующее устройство

содержит также группу регистров, четвертую группу элементов И, группу элементов ИЛИ, причем входы управления режимами работы регистров объединены с входами разрешения работы элементов задержки

второй группы и соединены с шиной управления устройства, сдвиговые входы регистров подключены к выходам постоянного запоминающего блока, на параллельные информационные входы первого регистра

подана нулевая кодовая комбинация, параллельные информационные входы каждого последующего регистра подключены к соответствующим выходам предыдущего регистра, а выходы последнего регистра соединены с первыми входами элементов И четвертой группы, вторые входы которых соединены с третьей шиной синхронизации устройства, а выходы элементов И четвертой группы соединены с первыми входами

соответствующих элементов ИЛИ группы, вторые входы которых подключены к выходам элементов И второй группы, а выходы элементов ИЛИ группы подключены к адресным входам постоянного запоминающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

Авторы

Даты

1993-03-23—Публикация

1991-02-07—Подача