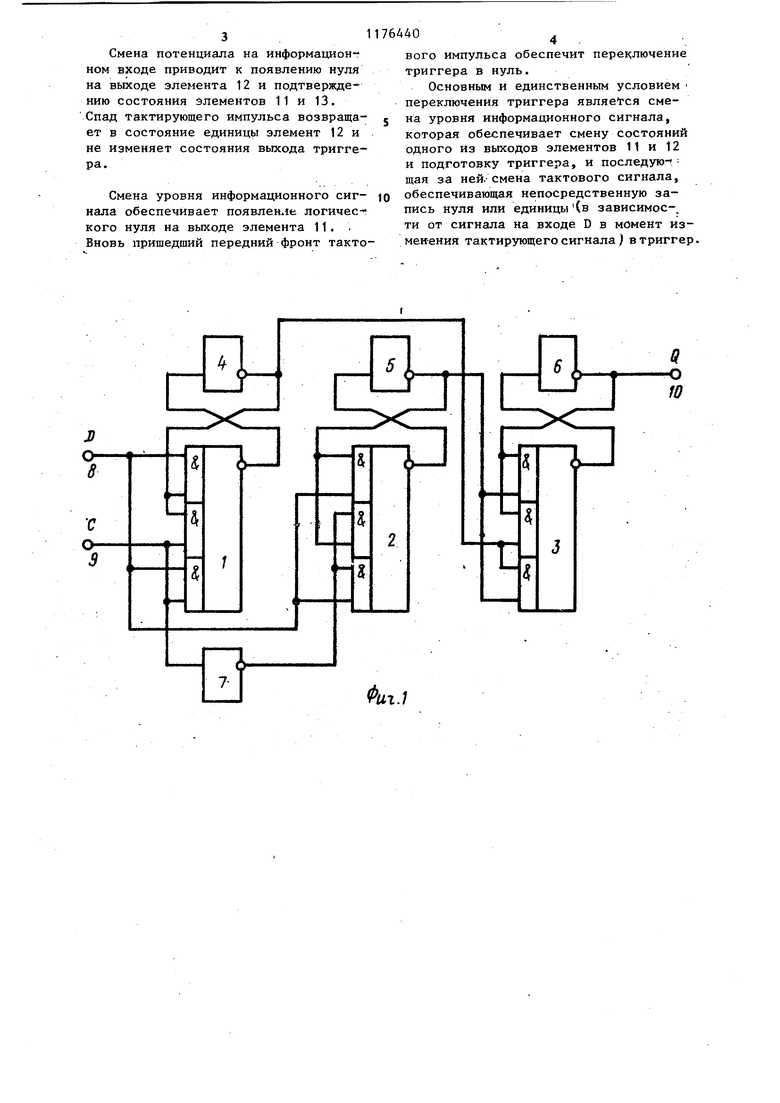

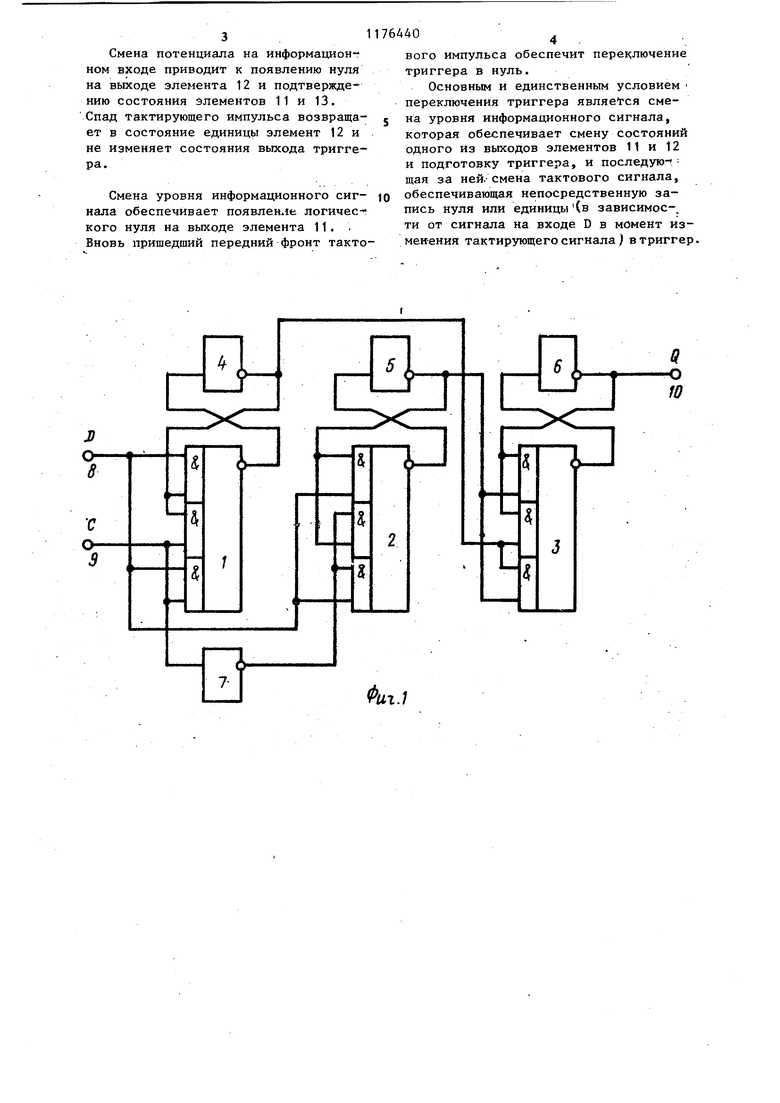

11 Изобретение относится к импульсной технике и может быть использова но при построении устройств передачи и обработки информации. Цель изобретения:- повьшение быстродействия триггера за счет обес печения записи входной информации ка по положительному, так и по отрицательному фронтам тактовых импульсов На фиг. 1 и 2 представлены схему триггера. Триггер содержит первый 1, второй 2 и третий 3 элементы И-ИСЛИ-НЕ, первый 4 второй 5, третий 6 и четвертый 7 инверторы, информационный и тактовый входы 8 и 9 и выход 10. Согласно представленной схеме логическое уравнение выхода первого инвертора (Q ) выглядит следующим образом: + + D.C, - состояние выхода перво го инвертора в момент времени t + 1; Q - то же, в момент времени t; D - состояние входа D; С - состояние входа С. Следовательно, первый элемент ИИЛИ-НЕ и первый инвертор составляют схему, эквивалентную схеме мажоритар ного элемента 2, один из входов ко торого подключен к входу D триггера, второй - к входу С, а третий - к выходу элемента. Схема, представленная на фиг. 1, эквивалентна схеме, представленной на фиг. 2, где первый мажоритарный элемент 1-1 заменяет первые инвертор и элемент И-ИЛИ-НЕ, второй мажоритар ный элемент 12 - вторые инвертор и элемент И-ИЛИ-НЕ, а третий мажоритар ный элемент 13 - третий инвертор и третий элемент И-ИЛИ-НЕ. Информационный D-вход триггера со единен с вторыми входами мажоритар- ньгх элементов 11 и 12, выходы которы по цепям обратных связей подключены к собственным третьим входам и, соот ветственно, к Первому и второму вхо дам третьего мажоритарного элемента 13, выход которого, являясь выходом Q-триггера, также поступает на свой третий вход, причем тактовый С-вход 9 триггера соединен с первым входом первого мажоритарного элемента 11 и входом инвертора 7, выход которого подключен к первому входу второго ма жоритарного элемента 12. 0 Триггер работает следующим Предположим, что в момент времени (перед появлением тактового импульса на вход С) на входе D присутствует . высокий потенциал логической единицы, тогда на выходе элемента 12 будет обеспечен уровень логической единицы за счет наличия высоких потенциалов на первом и втором входах, состояния выходов элементов 11 и 13 неопредеренны. При изменении уровня информационного сигнала по входу D-триггера на низкий уровень логического нуля на выходе элемента 11 также появится уровень логического нуля за счет низких потенциалов на входах D и С, однако и в этом случае состояние выхода триггера неопределенно, но неизменно.. С приходом фронта импульса на тактовый вход С-триггера на выходе триггера установится низкий уровень, логического нуля, обусловленный появлением нуля на выходе элемента 12 за счет нулей на первом и втором бходах этого элемента, что означает и наличие нулей на первом и втором входах элемента 13. Изменение на входе 8 уровня информационного сигнала приведет к изменению состояния выхода элемента 11, но не изменит состояния выхода триггера, так как в этом случае оно определяется обратной связью третьего элемента 13. Соответственно не изменится и состояние элемента 2. Смена потенциала на информационном входе не повлияет на состояние элементов, так как будет подтвержден низкий потенциал на выходе элемента 12, а состояния элементов 11 и 13 определяются обратными связями и не изменят-, ся. Спад импульса на входе триггера изменит состояние выхода элемента 11 на низкий, но по-прежнему не повлияет на выход триггера. Смена с низкого на высокий уровень информационного сигнала приведет к переключению в единицу выхода элемента 12, но опять-таки не изменит состояния выхода триггера, а i лишь подготовит эту смену в тот момент, когда изменится потенциал на входе 9 и появится вследствие этого логическая единица на выходе элемента 11, т.е. произойдет запись в , триггер логической едкницы. 3 Смена потенциала на информационг ном входе приводит к появлению нуля на выходе элемента 12 и подтверждению состояния элементов 11 и 13. Спад тактирующего импульса возвращает в состояние единицы элемент 12 и не изменяет состояния выхода триггера. Смена уровня информационного сигнала обеспечивает появление логического нуля на выходе элемента 11. . Вновь пришедший передний фронт такто 40 вого импульса обеспечит переключение триггера в нуль. Основным и единственным условием переключения триггера является смена уровня информационного сигнала, которая обеспечивает смену состояний одного из выходов элементов 11 и 12 и подготовку триггера, и последую- щая за ней. смена тактового сигнала, обеспечивающая непосредственную запись нуля или единицы (в зависимое-. ти от сигнала на входе D в момент измеи-ения тактирующего сигнала ) в триггер.

| название | год | авторы | номер документа |

|---|---|---|---|

| Д-триггер | 1985 |

|

SU1248034A1 |

| Устройство для сопряжения абонента с каналом связи | 1984 |

|

SU1211740A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Резервированное пересчетное устройство | 1982 |

|

SU1064475A1 |

| Трехканальное мажоритарно-резервированное устройство | 1983 |

|

SU1160616A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Устройство передачи двоичных сигналов | 1987 |

|

SU1467782A1 |

1)-ТРИГГЕР содержащий информационный вход, первый и второй элементы И-ИЛИ-НЕ, первый и второй инверторы, выходы которых подключены к первым входам первых групп по И соответствующих элементов И-ИЛИ-НЕ, выходы которых подключены к входам соответствующих инверторов, первый вход второй группы по И первого элемента И-ШШ-НЕ соединен с тактовым входом устройства,, отличающийся тем, что, с целью повышения быстродействия, в него введены третий элемент И-ИЛИ-НЕ, третий и четвертый инверторы, выход третьего элемента И-ИЛИ-НЕ соединен с входом третьего инвертора, выход которого подключен к выходу устройства и к первым входам первой и второй групп по И третьего элемента И-ИПИ-НЕ, второй вход первой группы по И которого соединен с выходом второго инвертора и с nepBtiM входом третьей группы по И третьего элемента И-ИЛИНЕ, второй вход которой соединен с вторым входом второй группы входов по и третьего элемента И-ИЛИ-НЕ и с выходом первого инвертора, выход которого соединен с вторым входом второй группы входов по И первого элемента И-ИЛИ-НЕ, второй вход первой группы входов по И которого соединен с информационным входом устройства, с первым входом третьей группы входов по И первого элемента И-ИЛИ-НЕ, (Л с вторым входом первой группы по И и первым входом третьей группы по И второго элемента И-ИЛИ-НЕ, второй вход которой соединен с первым входом второй группы входов по И второго элемента И-ИЛИ-НЕ и с выходом четвертого инвертора, вход которого подЧ ключен к второму входу третьей групгпы входов по И первого элемента И-ИЛИ-НЕ и к neJjBOMy входу его второй группы по И, причем второй вход второй, группы входов по и второго элемента И-ИЛИ-НЕ соединен с выходом второго инвертора.

|±

д

11

Аг.2

I о w

;j

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| Ребристый каток | 1922 |

|

SU121A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| D-триггер | 1980 |

|

SU930597A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-30—Публикация

1984-03-27—Подача