I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Устройство для функционального контроля логических элементов | 1984 |

|

SU1226468A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для проверки исправности многовыходных цифровых узлов. Целью изобретения является повышение достоверности контроля. Устройство содержит тактовый генератор 1, счетчик 2, дешифратор 3, коммутатор 4, преобразователь 6 формата кодов, m-входовых сумматоров 7.1-7.К по модулю два и сигнатурный анализатор 8. С помощью преобразователя формата кодов осуществляется распределение выходов контролируемого цифрового узла по К сумматорам по модулю два таким образом, чтобы взаимно инверсные выходы были подключены к разным сумматорам. 2 ил.

О

чэ ел

OJ

о

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для проверки исправности многовыходных цифровых узлов.

Цель изобретения - повышение достоверности контроля.

На фиг.1 представлена функциональная схема предложенного устройства; на фиг.2 - функциональная схема преобразователя формата кодов.

Устройство (фиг.1) содержит тактовый генератор 1, счетчик 2, дешифратор 3, коммутатор 4, контролируемый цифровой узел 5, преобразователь б формата кодов,К т- входовых сумматоров 7 по модулю два и сигнатурный анализатор 8.

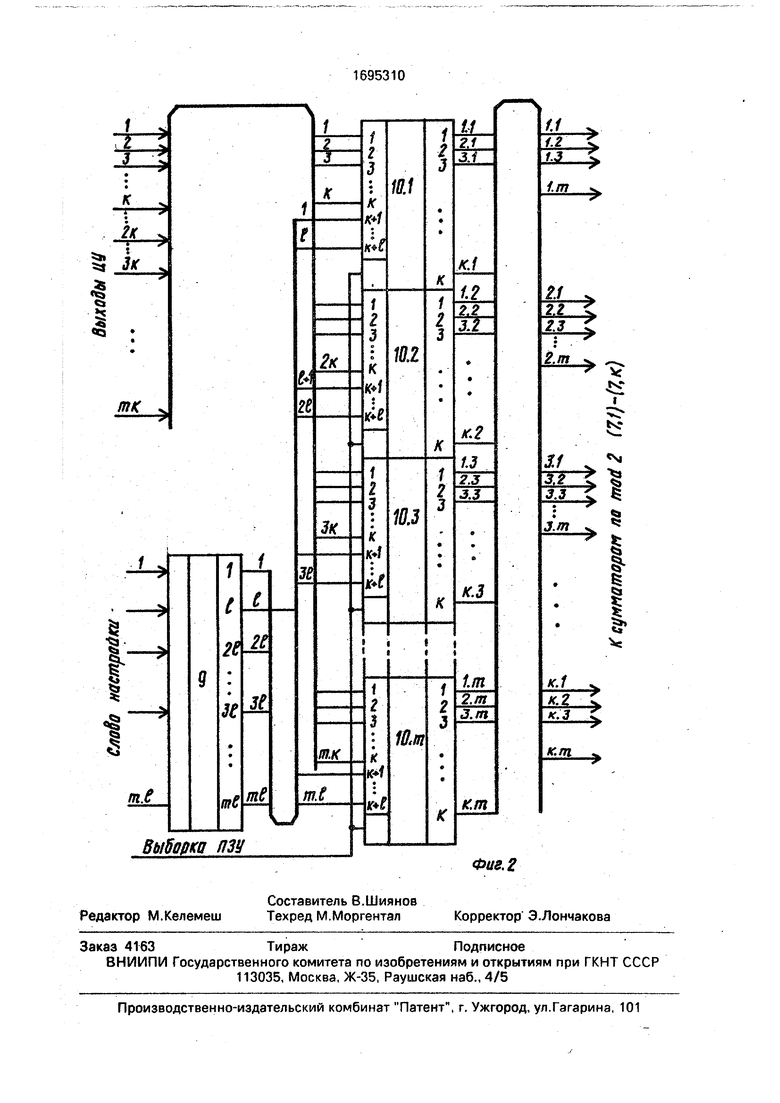

Преобразователь б форматов кодов (фиг.2)содержит mi-разрядный регистр 9 (т - количество выходов в одной группе выходов преобразователя; I - старшая часть адреса запоминающего устройства 10), m устройств 10, каждое из которых имеет (К-Н) адресных входов (К - младшая часть адреса), К информационных выходов, а также входы управления считыванием, количество которых определяется конкретным типом устройства 10.

Сущность изобретения заключается в том, что введение преобразователя б формата кодов позволяет путем его настройки под каждый тип контролируемого узла осуществить распределение выходов контролируемого узла по входам К сумматоров 7 по модулю два таким образом, чтобы избежать компенсаций, ошибок при суммировании в каждом из К сумматоров по модулю два, т.е. распределение осуществляется таким образом, чтобы выходы контролируемого узла с взаимно инверсными состояниями или с более сложными взаимозависимостями были поданы на разные сумматоры.

Устройство работает следующим образом.

Непосредственно перед контролем цифрового узла 5 в зависимости от его типа производится коммутация коммутатора 4, заключающаяся в механическом или электрическом соединении, в зависимости от конкретного выполнения коммутатора 4, группы выходов счетчика 2 с входами дешифратора 3, другой группы выходов счетчика 2 и выходов дешифратора 3 с входами узла 5, выхода старшего разряда счетчика 2 С управляющим входом Старт-стоп сигнатурного анализатора 8 и соединении выходов узла 5 с входами преобразователя 6, т.е. соединении п выходов узла 5 () с К адресными входами всех m запоминающих устройств 10 в произвольном порядке при условии, что каждый из п выходов узлов 5

соединен только с одним адресным входом только одного из m устройств 10. Одновременно с коммутацией коммутатора 4 или непосредственно за ней производится настройка преобразователя б, которая заключается в записи в регистр 9 настройки преобразователя 6 управляющего слова, разрядность которого гпМ, где m - количество запоминающих устройств 10 преобразователя 6, а I - количество адресных входов каждого устройства 10, которыми осуществляется его настройка. Управляющее слово для каждого типа у$ла 5 определяется один раз на стадии отработки методики его проверки в составе устройства контроля и может быть занесено в регистр 9 настройки с помощью поля механических переключателей, клавиатуры либо загружаются автоматически из запоминающего устройства при

использовании устройства контроля в комплексе с микроЭВМ и т.п. аппаратурой. Таким образом, после подачи слова настройки каждое устройство 10 преобразователя кодов, в зависимости от его прошивки и комбинации разрядов на I адресных входах, однозначно распределяет К сигналов с выхода узла 5, поданных на К-адресные входы по К выходам, и так как общее количество ПЗУ т, то происходит распределение К-т

выходных сигналов узла.

После настройки коммутатора 4 и преобразователя 6 под взаимодействием импульсов тактового генератора 1 счетчик 2 и подключенный к группе его выходов через

коммутатор 4 дешифратор 3 формирует тестовую последовательность, которая с другой группы выходов счетчика и выходов дешифратора 3 поступает на узел 5 через коммутатор 4. Выходные п сигналов узла 5,

являющиеся его реакциями на тестовую последовательность, через коммутатор 4 подаются на входы преобразователя 6, т.е. на К адресные входы m устройств 10, считываемая из устройств 10 информация под управлением сигнала Выборка запоминающего устройства, вырабатываемого синхронно импульсам тактового генератора по адресам, определяемым сигналами на К и I адресных входах, представляет собой

информацию, эквивалентную поданной на К адресные входы, но с измененным порядком чередования, согласно прошивке устройств 10 и управлению на 1-е части адреса.

Фазовый сдвиг между сигналами тактового генератора 1 и Выборка запоминающего устройства определяется конкретным типом устройства 10, т.е. его временем выборки адреса, максимальным циклом, считыванием и другими динамическими

параметрами. Таким образом, выходные сигналы узла 5 поступают на преобразователь 6, который в соответствии со словом управления распределяет эти сигналы на входы Km-входовых сумматоров по rfiod 2, которые осуществляют предварительную свертку параллельной mK-разрядной информации о реакции узла 5 в параллельную К-разрядную, которая затем поступает на информационные входы К-канального сигнатурного анализатора 8, который под управлением тактовых импульсов от тактового генератора 1 осуществляет окончательную свертку выходных реакций узла 5 в сигнатуру. Период контроля определяется периодом сигнала на выходе старшего разряда счетчика 2, поступающего через коммутатор 4 на вход Старт-стоп анализатора 8 и управляющего, таким образом началом и концом приема в него информации. Путем сравнения полученной в анализаторе 8 сигнатуры с эталонной для данного типа цифрового узла 5 определяется исправность проверяемого цифрового узла.

Смена тестового набора, т.е. переключение счетчика 2 в следующее состояние и синхронно с ним изменением выходного набора дешифратора 3 происходит синхронно с фронтом сигнала тактового генератора 1, а защелкивание выходной реакции узла 5 на этот тестовый набор, преобразованный в более компактную К-разрядную форму преобразователем 6 и сумматорами 7, происходит синхронно со спадом синхроимпульса генератора 1.

Длительность импульса генератора 1 для обеспечения стабильной работы устрой- свта, т.е. стабильной сигнатуры при исправном узле 5, должна быть не менее суммы

времени задержек коммутатора 4, узла 5, преобразователя 6 и сумматоров 7. Формула изобретения Устройство для контроля цифровых узлов, содержащее тактовый генератор, счетчик, дешифратор и сигнатурный анализатор, причем выход тактового генератора соединен со счетным входом счетчика и с синхровхо- дом сигнатурного анализатора, первая группа разрядных выходов является группой выходов устройства для подключения к первой группе ьходов контролируемого цифрового узла, группа выходов дешифратора является группой выходов устройства для

подключения к второй группе входов контролируемого цифрового узла, группа информационных входов дешифратора соединена с второй группой разрядных выходов счетчика, выход старшего разряда которого соединен с входом Старт-стоп сигнатурного анализатора, отличающееся тем, что, с целью повышения достоверности контроля, в него введены преобразователь формата кодов, Km-разрядных сумматоров по

модулю два (где К - количество групп выходов преобразователя формата и m - количество выходов в одной группе выходов преобразователя, причем Ют п, где п - количество выходов контролируемого цифрового узла), группа информационных входов преобразователя формата кодов является группой входов устройства для подключения к выходам контролируемого цифрового узла, К групп выходов преобразователя кодов соединены соответственно с группами входов К сумматоров по модулю два, выходы которых соединены с информационными входами сигнатурного анализатора.

Редактор М.Келемеш

Составитель В.Шиянов Техред М.Моргентал

Фиг. 2

Корректор Э.Лончакова

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических элементов | 1983 |

|

SU1182525A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1988-08-11—Подача