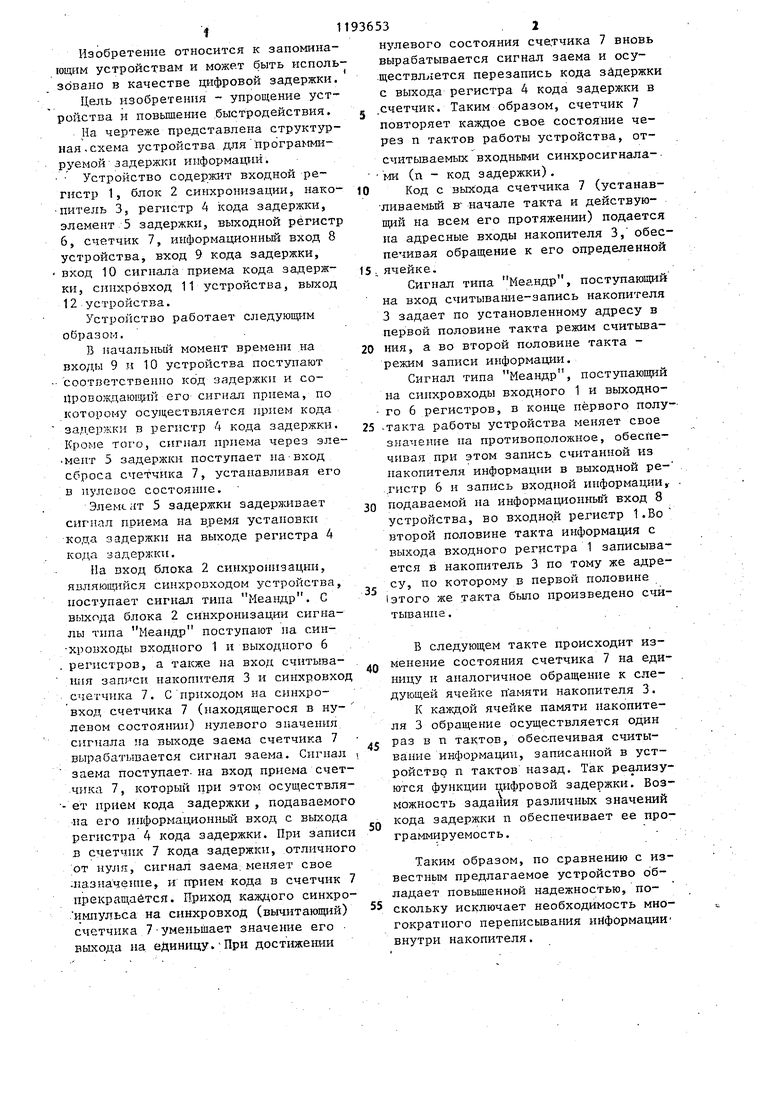

Изобретение относится к запоминающим устройствам и может быть исполь зовано в качестве цифровой задержки Цель изобретения - упрощение устройства и повьшение быстродействия. На чертеже представлена структурная -схема устройства для программируемой задержки информации. Устройство содержит входной регистр 1, блок 2 синхронизации, нако питель 3, регистр А кода задержки, элемент 5 задержки, выходной регистр б, счетчик 7, информационньш вход 8 устройства, вход 9 кода задержки, вход 10 сигнала приема кода за,держки, синхровход 11 устройства, выход 12 устройства. Устройство работает следующим образом. . В начальньй момент времени на входы 9 и 10 устройства поступают соответственно код задержки и соЦровогедаюнцй его сигнал приема, по которому осуществляется прием кода задержки в регистр 4 кода задержки. Кроме того, сигнал приема через элемент 5 задержки поступает на-вход сброса счетчика 7, устанавливая его в пулевое состояние. Элемент 5 задержки задерлшвает сигнал приема на цремя установки кода задержки на выходе регистра 4 кода задерлски, Яа вход блока 2 синхронизации, являющийся синхровходом устройства, поступает сигнал тина Меандр. С выхода блока 2 синхронизации сигналы типа Меаидр поступают на син-хровходы входного 1 и выходного 6 регистров, а также на вход считывакия записи накопителя 3 и синхровход счетчика 7. С приходом на синхровход счетчика 7 (находящегося в нулевом состоянии) нулевого значения сигнала на вькоде заема счетчика 7 вырабатывается сигнал заема. Сигнал заема поступает- на вход приема счетчика 7, который при этом осуществляет прием кода задержки , подаваемого на его информационный вход с выхода регистра 4 кода задержки. При записи в счетчик 7 кода задержки, отличного от нуля, сигнал заема: меняет свое -назначение, и прием кода в счетчик 7 прекращается. Приход каждого синхроимпульса на синхровход (вычитaющliй) сггетчика 7 уменьшает значение его выхода на единицу.-При достижении нулевого состояния сче,тчика 7 вновь вырабатывается сигнал заема и осу.ществл ется перезапись кода задержки с выхода регистра 4 кода задержки в .счетчик. Таким образом, счетчик 7 повторяет каждое свое состояние через п тактов работы устройства, отсчитываемых входными синхросигналагда (п - код задержки). Код с выхода счетчика 7 (устанавливаемьй в начале такта и действующий на всем его протяжении) подается иа адресные входы накопителя 3, обеспечивая обращение к его определенной ячейке. Сигнал типа Меандр, поступающий на вход считываш-1е-запись накопителя 3 задает по установленному адресу в первой половине такта режим считывания, а во второй половине такта режим записи информации. Сигнал типа Меандр, поступающий на сипхровходы входного 1 и выходного б регистров, в конце первого полутакта работы устройства меняет свое значение на противоположное, обеспечивая при этом запись считанной из накопителя информации в выходной ре.гистр б и запись входной информации,- подаваемой на информаидонньй вход 8 устройства, во входной регистр I.Bo второй половине такта информация с выхода входного регистра 1 записывается в накопитель 3 по тому же адресу, по которому в первой половине I этого же такта было произведено считывание. В следующем такте происходит изменение состояния счетчика 7 на единицу и аналогичное обращение к следующей ячейке Памяти накопителя 3. К каждой ячейке памяти пакопителя 3 обращение осуществляется один раз в п тактов, обес-печивая считывание информации, записанной в устройство п тактов назад. Так реализуются функции цифровой задержки. Возможность задания различных значений кода задержки п обеспечивает ее программируемость.- ; Таким образом, по сравнению с известньм предлагаемое устройство обадает повьшенной надежностью, поскольку исключает необходимость многократного переписьшания информации внутри накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программируемой задержки информации | 1986 |

|

SU1376074A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1381468A1 |

| Устройство для задержки информации | 1985 |

|

SU1287137A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Последовательное буферное запоминающее устройство | 1986 |

|

SU1332383A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

| Устройство цифровой задержки информации с контролем | 1988 |

|

SU1635225A1 |

| Блок задержки цифровой информации с самоконтролем | 1986 |

|

SU1388956A1 |

| Устройство для задержки цифровой информации с уплотнением | 1987 |

|

SU1425632A1 |

УСТРОЙСТВО ДЛЯ ПРОГРАММИРУЕМОЙ ЗАДЕРЖКИ ИЕ ФОРМАЦИИ, содержащее накопитель, адресные входы которого соединены с информационными выходами счетчика, а выходы - с информационными входами выходного регистра, выходы которого являются выходами устройства, блок синхронизации, вход которого является первым входом синхронизации устройства,а первый,второй и третий выходы блока синхронизации подключены соответственно к входам синхронизации выходного регистра, управления накопителя и синхрониза г ции счетчика, отличающеес я тем, что, с целью упрощения и повьпцения быстродействия, в него введены входной регистр, регистр кода задержки и элемент задержки, причем выход заема и вход приема данных счетчика соединены между собой, вход сброса счетчика подключен к выходу элемента задержки, а его информационные входы - к выходам регистра кода задержки, информационные входы и вход синхронизации которого, соединенный с входом элемента задержки, являются соответственно (Л входами регистра кода задержки и вторым входом синхронизации устройства, вход синхронизации входного регистра подключен к первому выходу 2 С блока синхронизации, выходы входного регистра соединены с входами накопителя, а информационные входы являются информационными входами устройстСО ва. со с СП 00

| Запоминающее устройство | 1975 |

|

SU556495A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Програгфшруемая цифровая задержка на основе ЗУПВ | |||

| Электроника, 1982, № 13, с.67. | |||

Авторы

Даты

1985-11-23—Публикация

1984-05-11—Подача