р«г/

Изобретение относится к вычислительной технике и может быть использовано в линиях задержки цифровой информации.

Целью изобретения является упрощение устройства.

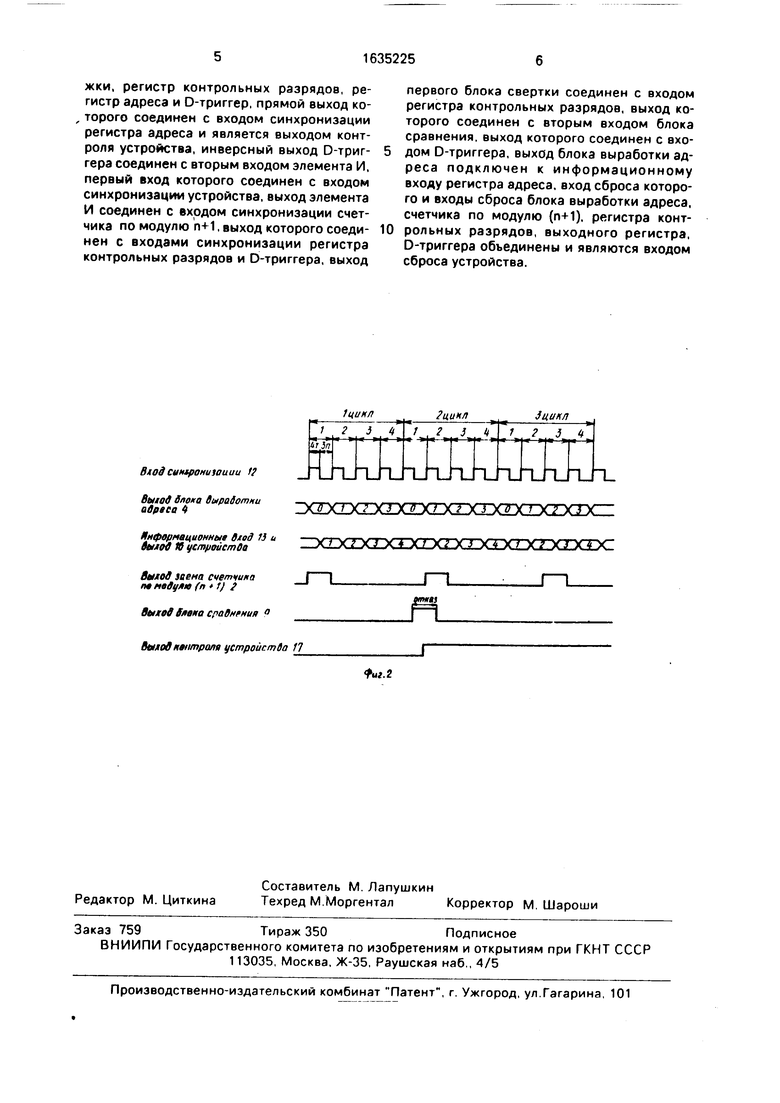

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства для , где п - величина задержки.

Устройство содержит элемент И 1, счетчик 2 по модулю (п+1), первый блок 3 свертки, блок 4 выработки адреса, накопитель 5, регистр 6 контрольных разрядов, выходной регистр 7, второй блок 8 свертки, блок 9 сравнения, D-триггер 10, регистр 11 адреса; на схеме обозначены вход 12 синхронизации устройства, информационный вход 13 устройства, вход 14 сброса, выход 15 адреса сбоя, информационный выход 16 устройства, выход 17 контроля устройства.

Устройство работает следующим образом.

В начальный момент времени происходит обнуление регистров 6, 11, триггера 10 устройства, блока 4 выработки адреса и счетчика 2 по модулю (п+1) по сигналу на входе 14 сброса.

Далее на информационный вход устройства 13 начинают поступать слова задерживаемой последовательности, сопровождаемые синхроимпульсами типа меандр на входе синхронизации устройства 12. Во время первой половины такта происходит чтение информации,записанной в данную ячейку никопителя 5 п тактов назад, а во время второй половины такта - запись в эту же ячейку входной информации, которая, в свою очередь, будет считана через п тактов. Блок 4 выработки адреса при этом последовательно перебирает адреса ячеек накопителя, обеспечивая запись очередного задерживаемого слова в следующую ячейку памяти. Величина задержки п (где п - количество ячеек) определяется коэффици ентом пересчета блока 4 выработки адреса, который является счетчиком по модулю п.

Один цикл задержки составляет п тактов. В каждом цикле задержки осуществляется сравнение контрольных разрядов, вычисленных вторым блоком свертки 8 для информации, считанной из i-й ячейки накопителя, с контрольными разрядами, вычисленными первым блоком 3 свертки для этой же информации до записи ее в l-ю ячейку накопителя в предыдущем цикле задержки. Вычисленные первым блоком 3 свертки контрольные разряды хранятся в регистре 6 контрольных разрядов. В каждом последующем цикле происходит фиксация результата сравнения для i-й ячейки и запись вычисленных разрядов для следующей (К1)-й ячейки накопителя. Таким образом, за п циклов задержки будут проверены все п ячеек накопителя.

Результат сравнения фиксируется в Dтриггере 10 на время одного цикла. Если контрольные разряды, вычисленные блоками свертки 3 и 8 как свертка по модулю т, совпали, то проверяемая ячейка накопителя

0 работает нормально и сигнал О с выхода блока 9 сравнения записывается в D-триггер 10. Если же сравнение не произошло - сбой проверяемой ячейки накопителя, то в D-триггер 10 записывается сигнал 1, кото5 рый поступает на выход контроля устройства 17 и фиксирует адрес неисправной ячейки накопителя в регистре 11 адреса. Одновременно с этим сигнал О поступает с инверсного выхода D-триггера 10 на вто0 рой вход элемента И 1, блокируя тем самым поступление импульсов синхронизации на счетчик 2. Таким образом работа системы контроля останавливается и на выходе регистра 11 удерживается адрес неисправной

5 ячейки памяти накопителя 5.

После устранения неисправности для поиска следующих неисправных ячеек необходимо вновь подать сигнал сброса на выходе 14 в начале очередного цикла задер0 жки,

Фиксация результатов сравнения и запись в регистр 6 контрольных разрядов для следующей проверяемой ячейки осуществляются по переднему и заднему фронтам

5 сигнала с выхода заема счетчика 2 по модулю (п+1) соответственно.

Формула изобретения Устройство цифровой задержки информации с контролем, содержащее блок выра0 ботки адреса, накопитель, первый и второй блоки свертки, выходной регистр, блок сравнения и элемент И, причем вход синхронизации блока выработки адреса соединен с управляющим входом накопителя и с

5 входом синхронизации выходного регистра и является входом синхронизации устройства, информационный вход накопителя соединен с входом первого блока свертки и является информационным входом устрой0 ства, выход блока выработки адреса соединен с адресным входом накопителя, информационный выход которого соединен с входом выходного регистра, выход которого соединен с входом второго блока свертки

5 и является информационным выходом устройства, выход второго блока свертки соединен с первым входом блока сравнения, отличающееся тем, что, с целью упрощения устройства, в него введены счетчик по модулю (п+1). где п - величина задержки, регистр контрольных разрядов, регистр адреса и D-триггер, прямой выход которого соединен с входом синхронизации регистра адреса и является выходом контроля устройства, инверсный выход D-триг- гера соединен с вторым входом элемента И, первый вход которого соединен с входом синхронизации устройства, выход элемента И соединен с входом синхронизации счетчика по модулю п+1, выход которого соединен с входами синхронизации регистра контрольных разрядов и D-триггера, выход

первого блока свертки соединен с входом регистра контрольных разрядов, выход которого соединен с вторым входом блока сравнения, выход которого соединен с входом D-триггера, выход блока выработки адреса подключен к информационному входу регистра адреса, вход сброса которого и входы сброса блока выработки адреса, счетчика по модулю (п+1), регистра контрольных разрядов, выходного регистра, D-триггера объединены и являются входом сброса устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки цифровой информации с контролем | 1987 |

|

SU1462424A1 |

| Устройство для задержки информации | 1985 |

|

SU1287137A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Блок задержки цифровой информации с самоконтролем | 1986 |

|

SU1368922A1 |

Изобретение относится к вычислительной технике и может быть использовано в линиях задержки цифровой информации. Целью изобретения является упрощение устройства. Устройство .содержит элемент И 1, счетчик 2 по модулю(п+1), первый з и второй 8 блоки свертки, блок 4 выработки адреса, накопитель 5, регистр 6 контрольных разрядов, выходной регистр 7, блок 9 сравнения, D-триггер 10, регистр 11 адреса. Устройство осуществляет задержку цифровой информации на величину п, где п - количество ячеек накопителя, проверяя в каждом цикле задержки по одной ячейке накопителя Таким образом, за п циклов задержки производится проверка всех п ячеек накопителя. 2 ил.

)цинл

симрониюиии 12

Выюд блока дыработни адреса 4

Информационные Оюд 13 ч былоа Ю устройства

Выход see на счетчика м падуя« (п 1) f

Выжод бяека сравнения о

1 2 3 4 1 2 3 4 1 2 5 4

гщ р г Т Т Т -DTJnJTjTJTJThj

УТУ7У7Х У7 Х Т У

Вылов явитраая устройства f

2и.

Зцикл

| Регулятор температуры прямого действия | 1985 |

|

SU1287127A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Блок задержки цифровой информации с самоконтролем | 1986 |

|

SU1368922A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-03-15—Публикация

1988-05-25—Подача