ния, один из входов блока индикации соединен с одним из выходов блока функциональной диагностики, выходы второй группы которого соединены с вторыми входами элементов ИЛИ третьей и четвертой групп, информационные входы регистров числа соединены соответственно с выходами элементов ИЛИ групп, одни из управляющих входов регистров числа соеди.нены соответственно с выходами элементов ИЛИ с второго по девятый, выход второго элемента И соединен с одними из входов элементов ИЛИ с второго по пятьй, другой адресный вход третьего постоянного накопителя управляющие входы блока постоянных накопителей, сумматора, первого и второго постоянных накопителей, счетчика, блока индикации, блока функциональной диагностики, элементов И, элементов ИЛИ с второго по девятый и другие управляющие входы регистров числа соединены с выходами блока управления,

2. Устройство по п. 1, отличающееся тем,что блок функциональной диагностики содержит груП

пы элементов И с первой по третью, группу дополнительных элементов ИЛИ, элементы НЕРАВНОЗНАЧНОСТЬ., группы блоков сравнения и элемент ЗАПРЕТ, выход которого соединен с одними из входов элементов И третьей группы и первыми входами блоков сравнения первой группы, выходы элементов И первой группы соединены с первыми входами дополнительных элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И второй и третьей групп, выходы дополнительных элементов ИЛИ группы соединены с входами элементов НЕРАВНОЗНАЧНОСТЬ, выходы которых соединены с вторыми входами блоков сравнения первой группы у первыми входами блоков сравнения второй группы,.причем входы элементов И первой и второй групп, другие входа элементов И третьей группы, входы элемента ЗАПРЕТ, третьи входы блоков сравнения первой группы, вторые и третьи входы блоков сравнения второй группы являются входами блока, выходами которого являются выходы элементов НЕРАВНОЗНАЧНОСТЬ, элемента ЗАПРЕТ и блоков сравнения групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Устройство для приема телесигналов | 1983 |

|

SU1137497A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1984 |

|

SU1215139A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее регистр адреса, оперативный накопитель и регистры числа, управлянидие входы которых соединены с одним из выходов блока управления, элементы И и блок индикации, о тличающе. еся тем, что, с целью повышения надежности устройства, в него введены сумматор, счетчик, блок функциональной диагностики, блок постоянных накопителей, группы элементов ИЛИ с первой по пятую, постоянные накопители с первого по третий, элементы ИЛИ с первого по десятый, причем информационные входы регистра адреса, входы первой группы и первые входы элементов ИЛИ первой и второй групп-подключены к шинам входной информации, выходы регистра адреса соединены с входами блока постоянных накопителей и с одМими из: входов сумматора, другие входы которого соединены с одними из выходов блока постоянных накопителей, другие выходы которых соединены с адресными входами первого и второго постоянных накопителей, выходы сумматора соединены с входами первой группы оперативного накопителя и блока индикации, выходы первого и второго постоянных накопителей соединены соответственно с входами второй группы оперативного накопителя и информационными входами счетчика, выходы которого соединены с входами первого элемента ИЛИ и одними из адресных входов третьего постоянного накопителя, выходы которого подключены к входам сдвига второго регистра числа, выход первого элемента ИЛИ соединен с одними из входов первого элемента И, блока функциональной диагностики и блока управления, выход первого элемента И соединен с вычитающим входом счетчика и управляющим входом третьего постоянного накопителя, входы третьей группы оперативного накопителя соединены с выходами элементов ИЛИ пятой группы, выходами с третьего и четвертого регистров числа и входами второй группы блока функциональной диагносСО тики, выходы оперативного накопителя ю м соединены с вторыми входами элементов ИЛИ первой и второй групп и первыми входами элементов ИЛИ третьей и четвертой групп, входы второй группы блока индикации подключены к выходам первой группы блока функциональной диагностики, входы третьей группы блока индикации соединены с шинами выходной -информации, выходами первого и второго регистров числа и входами элементов ИЛИ пятой группы, выходы второго регистра числа подключены к входам десятого элемента ИЛИ, выход которого соединен с другим входом блока управле

Изобретение относится к вычислителоной технике и может быть использовано в цифровых устройствах для хранения информации.

Цель изобретения - повышение нaдeжнOv.ти устройства.

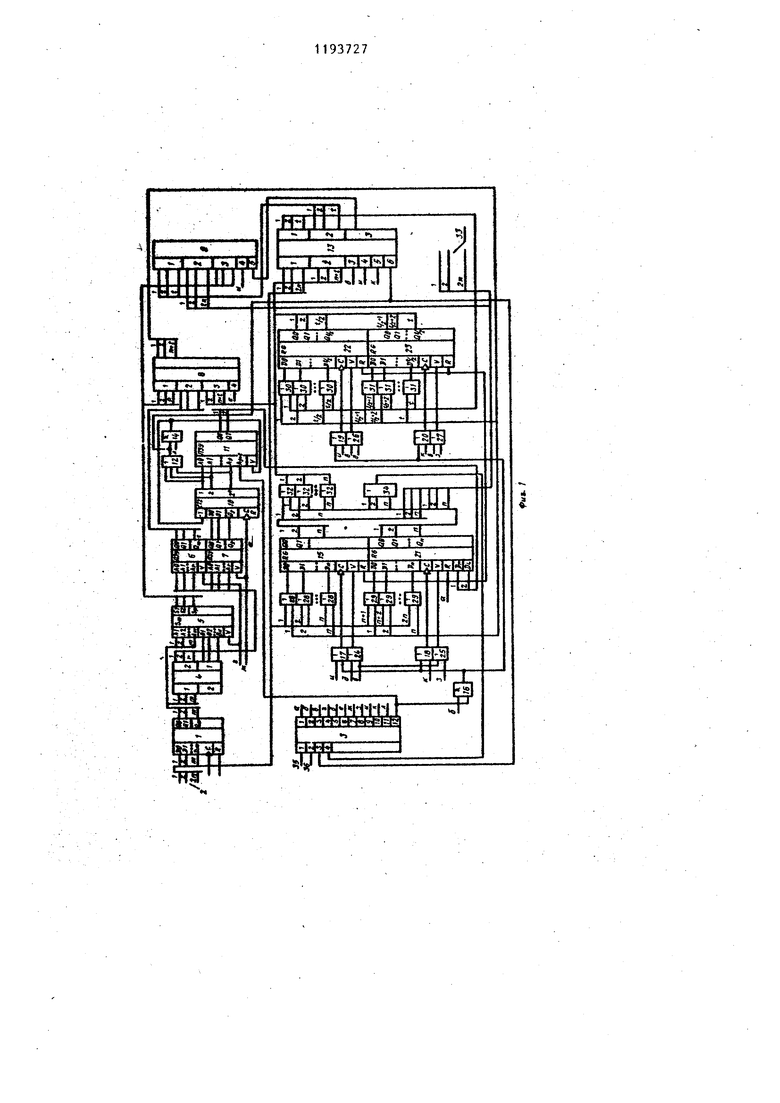

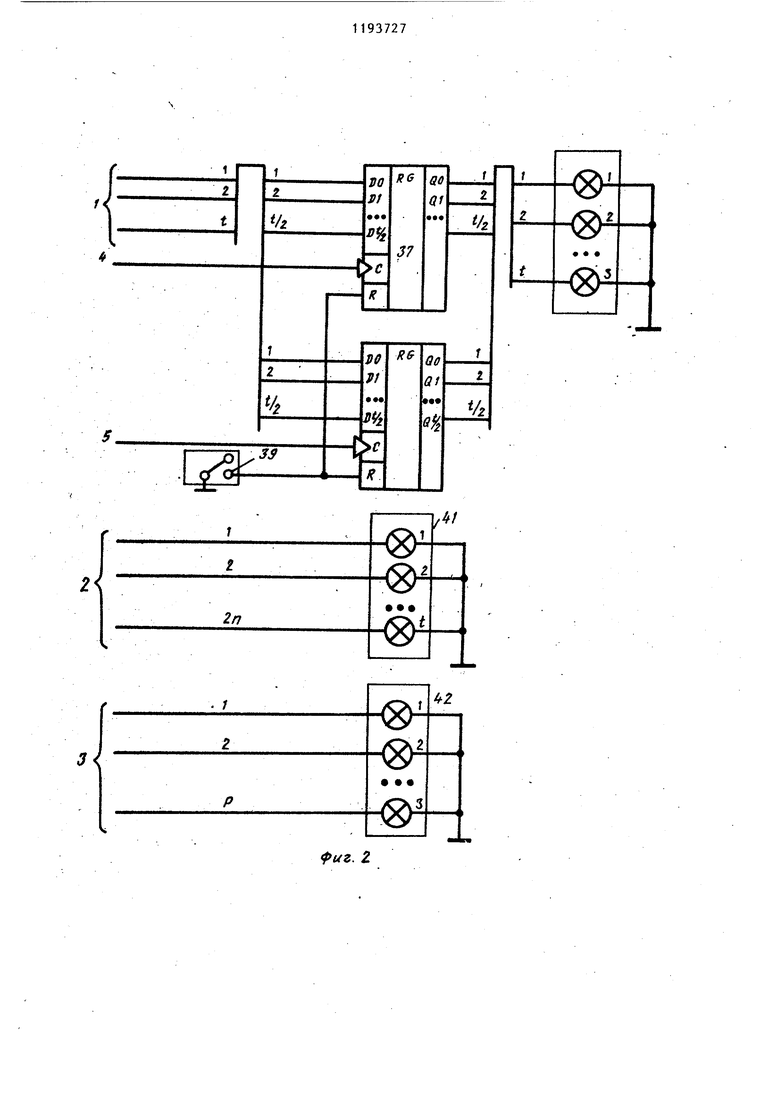

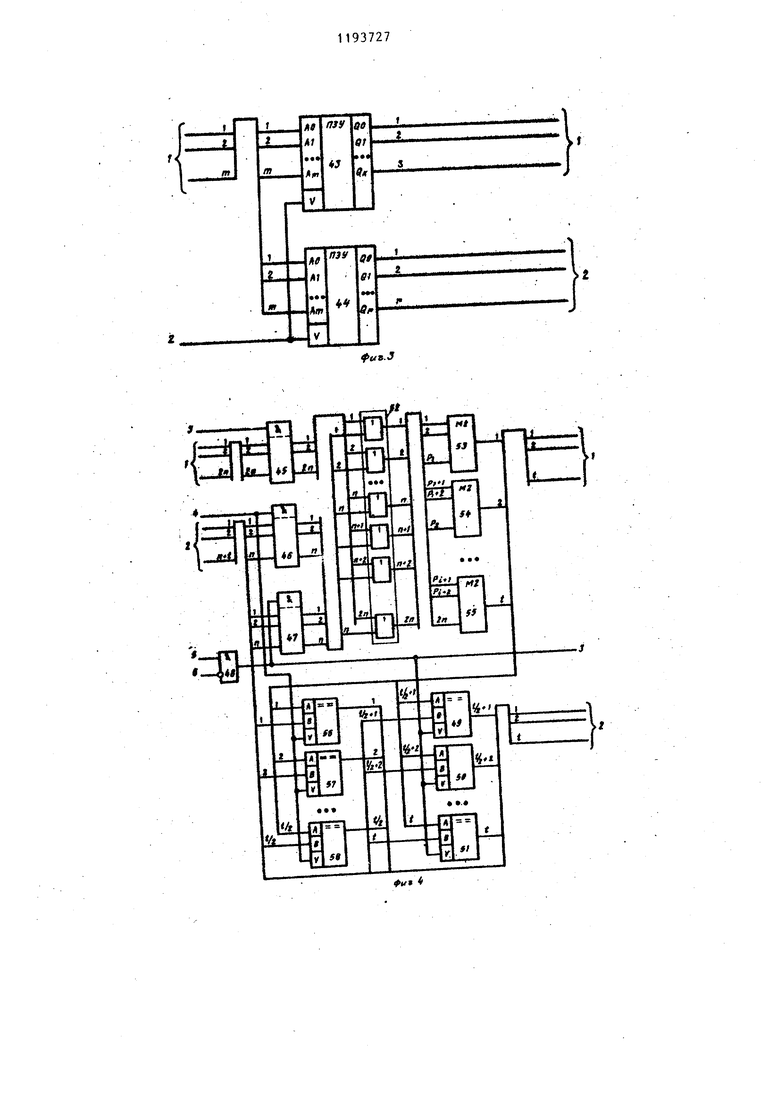

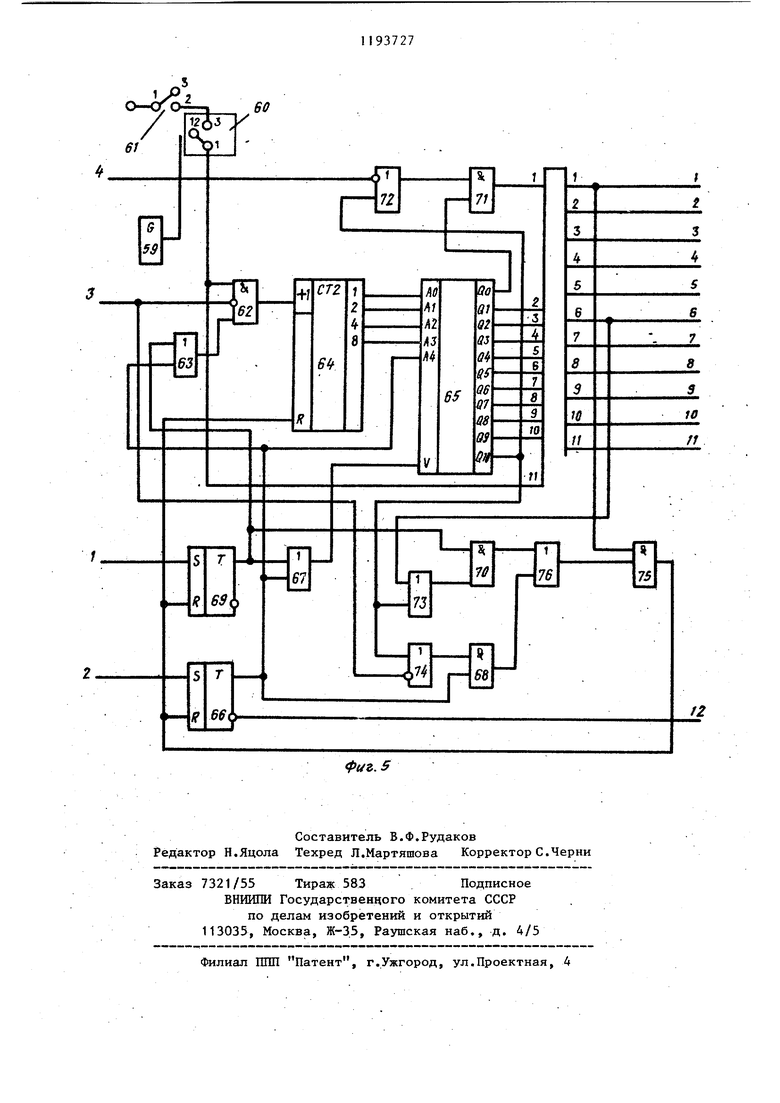

На фиг. 1 изображена структурная схема предлагаемого запоминающего устройства; на фиг. 2 - принципиальная схема блока индикации; на фиг. 3 принципиальная схема блока постоянных накопителей; на фиг. 4 - принципиальная схема блока функциональной диагностики; на ,фиг. 5 - принципиальная схема блока управления.

Запоминаняцее устройство (фиг.1) содержит регистр 1 адреса, подключенный к шинам 2 входной чгаформации, блок 3 управления, блок 4 постоянных накопителей, сумматор 5, первый и второй 7 постоянные накопители, оперативный накопитель 8, блок 9 индикации, счетчик 10, третий постоянный накопитель 11, первьй элемент ИЛИ 12, блок 13 функциональной диагностики, первый элемент И 14, первый регистр 15 числа, второй элемент И 16, элементы ИЛИ 17-20 со второго по пятый, второй 21, третий 22 и четвертый 23 регистры числа, элементы ИЛИ 24-27 с шестого по девятый, группы элементов ИЛИ 28-32 с первой по пятую, шину 38 выходной информации, десятый элемент ИЛИ 34, шину 35 сигнала Запись и шину 36 сигнала Считыв ание.

Блок 9 индикации (фиг. 2) содержит регистры 37 и 38, кнопку 39 и группы индикаторов 40-42. Блок 4 содержит (фиг. 3) постоянные накопители 43 и 44. Блок 13.функциональной диагностики (фиг. 4) содержит первую 45, вторую 46 и третью 47 группы элементов И, элемент ЗАПРЕТ 48, первую группу блоков 49-51 сравнения, группу дополнительных элементов ИЛИ 52

3

элементы НЕРАВНОЗНАЧНОСТЬ 53-55, вторую группу блоков 56-58 сравнения. Блок 3 управления содержит (фиг, 5) генератор 59 импульсов, переключатель 60, кнопку 61, элемент ЗАПРЕТ 6 элемент ИЛИ 63, счеучик 64, постоянный накопитель 65, триггер 66, элемент ИЛИ 67, элемент И 68, триггер 6 элементы И 70 и 71, элемент ИМПЛИКАЦИЯ 72, элемент ИЛИ 73, элемент ИМПЛИКАЦИЯ 74, элемент И 75 и элемент ИЛИ 76.

Предлагаемое устройство может работать в режимах Запись и Считывание.

В качестве примера, опишем работу устройства в режиме Запись, а также работу блоков 9 и 13, входящих в устройство.

Работа запоминающего устройства в .режиме Запись происходит- следующим образом. В исходном состоянии триггера счетчики и регистры, расположенные в блоках 1, 3 и 9, находятся в нулевом состоянии, а на всех выходах блока 3 присутствует сигнал О. Также в нулевом состоянии находится счетчик 10 и-регистры 2f, 15, 22 и 23. По команде Запись, поступающей по шине 35 на вход блока 3, на его выходе появляется сигнал 1, . который в качестве сигнала разрешения поступает на входы элементов ШЩ 24 - 27 и на вход бло- . ка 13. По этому сигналу блок 13.начинает выработку контрольных разрядов информационного слова. Входное информационное слово разбивается на несколько частейJ определяется количество единиц в каждой части и в зависимости от четности этого количества записьшается в контрольный разряд сигнал О - при четном значении числа и сигнала 1 - при нечетном. Выработанные контрольные слова с выходов блока 13 поступают на входы элементов ИЛИ 30 и 31. Далее по программе работы блока 3 на его выходе появляется сигнал 1, который поступает на вход регистра 1 адреса и на вход элемента И 16. Происходит запись в регистры 21, 15, 22 и 23, с целью предбарительного. хранения кодов, поступивших на входы элементов ИЛИ 28 - 31.

С появлением единичного сигнала на одном из выходов блока 3 управления на управляющие входы сумматора 5 и накопителя 6 поступает сиг937274

нал разрешения подачи кода адреса с выхода регистра 1 адреса на входы подачи первого слагаемого сумматора 5. В результате на его выходах появляется заданный код адреса, который далее поступает на первый вход накопителя 8. На выходах регистров 21 и 22, а затем на выходах элементов ИЛИ 32 появляется код информаци Q онного слова с приписанными к нему контрольными разрядами. В это же время с выходов накопителя 6 на вхо ды накопителя 8 поступает сигнал общего разрешения записи. Блок 3

15 управления санкционирует запись информационного слова в накопитель 8. Таким образом происходит запись слов, разрядность которых совпадает с разрядностью накопителя В. .

Если разрядность информационного слова больше разрядности накопите- ля 8, но меньше или равна удвоенной разрядности информационного слова,

25 то процесс записи на описанном не кончается, .поскольку с выхода элемента ИЛИ 34 на вход блока 3 управления , поступает блокиру яций lio- .тенциал, благодаря чему блок 3 продолжает вьщачу синхроимпульсов в со0ответствии с программой его работы. С выхода блока появляется разрешающий потенциал, который поступает на вход блока 4 и управляющие входы накопителя 7 и счетчика Ю.Разрешающий потенциал с выхода блока 3 управления поступает на управляющие входы сумматора 5 и накопителя 6. От блока 3 поступает сигнал разрешения на входы элементов ИЛИ 25 и 27,

0 а также сигнал на вход блока, на его первых выходах появляется код переадресации, а на вторых выходах код адресов распределения. Так как в это время на управляюпщх входах

сзтматора 5, счетчика 10 и накопителей 6 и 7 действуют сигналы от блока 3, то код переадресации, поступающий на входы второго слагаемого сумматора 5, приводит к формированию

0 на его выходах выработанного адреса. Вьфаботанный адрес с выхода сумматора 5 поступает на входы накопителя 8. Одновременно с вторых выходов блока 4 код адреса распределения поступает

5 на адресные входы накопителей 6 и 7. С выходов накопителя 6 код распределения поступает на управляющие входы накопителя 8.

51

По сигналу с элемента ИЛИ 12

блок 3 управления приостанавливает вмдачу синхроимпульсов, сохраняя на управляющих выходах предыдущее состояние. В то же самое время тактовые импульсы, поступающие на вход элемента И 1А, на выходе накопителя 11 формируют импульсы сдвига, которые начнут поступать на вход сдвига вправо регистра 21. Выдача импульсов сдвига продолжается до момента поступления с выхода элемента ИЛИ 12 на вход блока 3 управления разрешения на выдачу синхроимпульсов. Далее происходит запись остатка информационного слова вместе с контрольными разрядами в накопитель 8 .в соответствии с кодом распределения по новому адресу. Затем по программе работы блока 3 управления на его выходе появляется ригнал общего сброса, который приводит устройство в исходное состояние. На этом цикл Записи заканчивается, и устройство оказывается подготовленным к любому другому циклу работы.

Работа блока индикации 9 происходит следующим образом.

На первые входы блока 9 с выходов бл )ка 13 поступает код ошибок, обнаруженный в контрольных разрядах в процессе вьтолнения режима считывания. На информационные входы регистра 37 поступает код ошибок в основной части информационного слова. Запись в регистр 37 происходит при поступлении на его командный вход сигналаС входа блока 9 соответствующего сигнала. При наличии ошибки поступает сигнал 1, при отсутствии - сигнал О. С выходов регистра 37 код ошибки поступает на индикаторы 40 и отображается в форме доступной оператору.

Аналогично код ошибки остатка информационного слова с первых входов блоки 13 поступает на информационные входы регистра 38, в котором записывается при появлении сигналов разрешения на входе блока 9. С выхода регистра 38 код ошибки также поступает на индикаторы 40. С помощью кнопки 39 оператор осуществляет сброс контрольных разрядов путем установки в начальное состояние регистров 37 и 38 после визуального считывания с индикаторов 40 и анализа ошибки.

37276

В режиме контроля информационное

слово поступает на вторые входы блока 9 и отображается непосредственно на индикаторах 41. Аналогично код адреса поступает на третьи входы блока 9, где также непосредственно отображается индикаторами 42.

Работа блока 13 функциональной диагностики происходит следующим

Q образом.

В режиме записи с первых входов блока 13 информационное слово поступает на вторые входы элементов И 45. При появлении на третьем входе блока 13 сигнала разрешения информационное слово поступает на вторые входы элементов И 45. При появлении на третьем входе блока 13 сигнала разрешения информационное слово с выQ ходов элементов И .45 поступает на первые входы элементов ИЛИ 52. С выходов же элементов И.46 и 47.будут поступать сигналы О, так как в это время отсутствуют сигналы разрешения

5 на четвертом, пятом и шестом входах блока 13. Поэтому поступившее на первый вход информационное слово поступает на входы элементов суммирования по модулю два НЕРАВНОЗНАЧНОСТЬ

0 53-55. При поступлении на элементы 53-55 четного количества единиц на выходе элемента появляется сигнал О, а при нечетном числе сигнал 1. Благодаря этому на первых выходах блока 13 появляются

выработанные контрольные разряды.

В режиме считывания на вторые входы блока 13 сначала поступает основная часть информационного слова вместе со своими Контрольными разрядами. Одновременно на четвертый вход блока 13 поступает сигнал разрешения, поэтому основная часть информационного слова с выходов элементов И 46 поступает на вторые входы элементов ИЛИ 52. Так как в это время нет сигнала разрешения на третьем, пятом и шестом входах блока 13, то на первые входы элементов ИЛИ 52 и на вторые входы второй половины элементов ИЛИ 52 поступают сигналы 6 с выходов элементов И 45 и 47. Поэтому основная часть информационного слова поступает на входы элементов НЕРАВНОЗНАЧНОСТЬ 53-55. В результате на их выходах появляются контрольные разряды основной части информационного слова, которые посту7

пают на первый выход блока 13 и на первые входы блоков 56-58. На вторые входы этих блоков со вторых входов блока 13 поступают контрольные разря ды основной части информационного слова, выбранные из накопителя 8 и временно хранимые в регистрах 15 и 21 - 23. Так как с четвертого входа на управЛякяций вход блоков 56-58 действует сигнал разрешения, то на выходе этих блоков появляется код ошибок в основной части информационного слова (наличие ошибки - сигнал 1, отсутствие - сигнал О). Этот кед ошибок с выходов блоков 5658 поступает на вторые выходы бло1са 13 и далее на первые входы блоfca 9.

Когда на вторые входы блока 13 .поступает остаток информационного слова вместе со своими контрольными

937278

разрядами, то при наличии сигналов на пятом и шестом входах на выходах элементов И А7 появляется остаток информационного слова, который через , элементы ИЛИ 52 поступает на входы элементов НЕРАВНОЗНАЧНОСТЬ 53-55. Выработанные на их выходах контрольные разряды поступают на первые входы блоков 49-51, на вторые входы

to которых со вторых входов блока 13 поступают контрольные разряды остатки информационного слова. Вследствие того, что при наличии сигналов t на пятом входе- и сигнала О на

15 шестом элемент ЗАПРЕТ 48 вырабатыет разрешакиций сигнал, поступающий на третий выход блока 13 и на управляющие входы блоков49-51. На их выходах формируется код

20 ошибок, который поступает.на вторые выходы блока 13 и далее на первые входы блока 9.

. /

иг. 2

f

m

.Ш

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU427379A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1978 |

|

SU781974A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| / | |||

Авторы

Даты

1985-11-23—Публикация

1983-10-27—Подача