Изобретение относится к вычислительной технике и может быть исгюльзовано в интегральном полупроводниковом МДП запоминающем устройстве.

Целью изобретения является повышение надежности усилителя считывания.

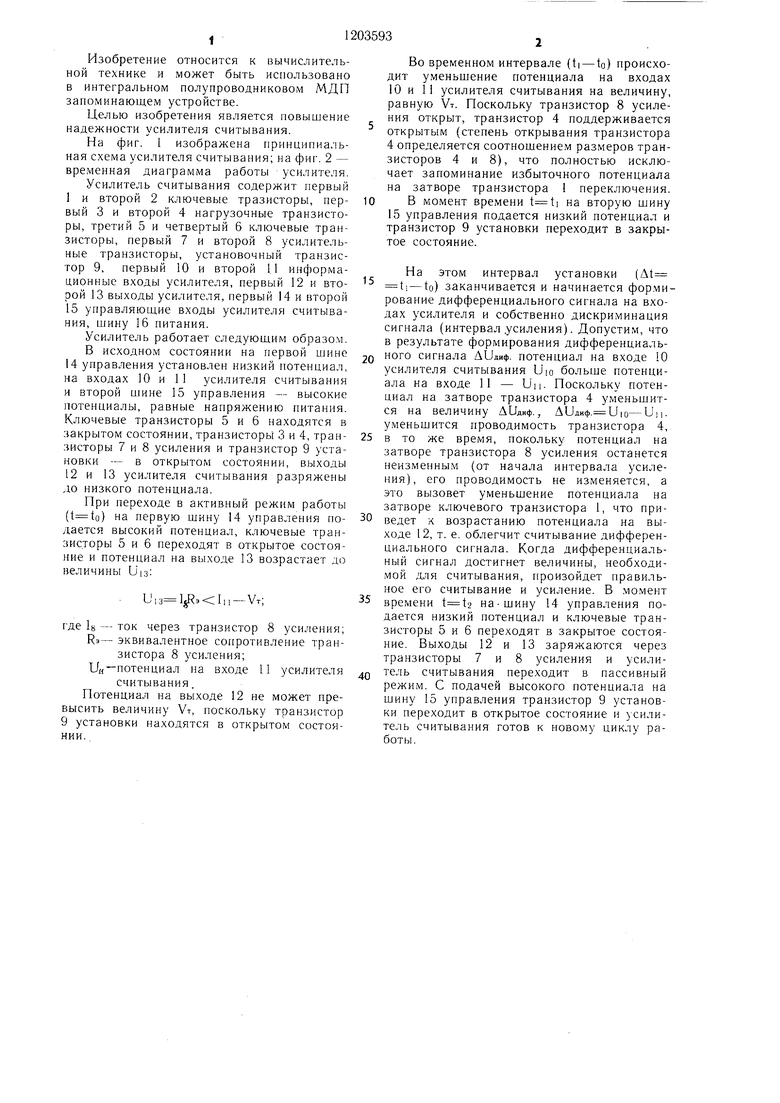

На фиг. 1 изображена принципиальная схема усилителя считывания; на фиг. 2 - временная диаграмма работы усилителя.

Усилитель считывания содержит первый 1 и второй 2 ключевые тразисторы, пер- вый 3 и второй 4 нагрузочные транзисторы, третий 5 и четвертый 6 ключевые транзисторы, первый 7 и второй 8 усилительные транзисторы, установочный транзистор 9, первый 10 и второй 11 информационные входы усилителя, первый 12 и второй 13 выходы усилителя, первый 14 и второй 15 управляющие входы усилителя считывания, тину 16 питания.

Усилитель работает следующим образом.

В исходном состоянии на первой шине 14 управления установлен низкий потенциал, на входах 10 и 11 усилителя считывания и второй щине 15 управления - высокие потенциалы, равные напряжению питания. Ключевые транзисторы 5 и 6 находятся в закрытом состоянии, транзисторы 3 и 4, тран- зисторы 7 и 8 усиления и транзистор 9 установки - в открытом состоянии, выходы 12 и 13 усилителя считывания разряжены до низкого потенциала.

При переходе в активный режим работы () на первую щину 14 управления подается высокий потенциал, ключевые транзисторы 5 и 6 переходят в открытое состояние и потенциал на выходе 13 возрастает до величины Uis:

,,-VT;

г де Ig - ток через транзистор 8 усиления; Rs- эквивалентное сопротивление транзистора 8 усиления; U/f-потенциал на входе 11 усилителя

считывания.

Потенциал на выходе 2 не может превысить величину VT, поскольку транзистор 9 установки находятся в открытом состоянии.

Во временном интервале (ti - to) происходит уменьщение потенциала на входах 10 и 11 усилителя считывания на величину, равную VT. Поскольку транзистор 8 усиления открыт, транзистор 4 поддерживается открытым {степень открывания транзистора 4 определяется соотношением размеров транзисторов 4 и 8), что полностью исключает запоминание избыточного потенциала на затворе транзистора 1 переключения.

В момент времени на вторую щину 15 управления подается низкий потенциал и транзистор 9 установки переходит в закрытое состояние.

5

5

0

0

0

На этом интервал установки (At ti - to) заканчивается и начинается формирование дифференциального сигнала на входах усилителя и собственно дискриминация сигнала (интервал .усиления). Допустим, что в результате формирования дифференциального сигнала ДОдиф. потенциал на входе 10 усилителя считывания Lj io потенциала на входе 11 - Un. Поскольку потенциал на затворе транзистора 4 уменьшится на величину ЛОдиф., Дидиф. и|о-Ыц. уменьшится проводимость транзистора 4, в то же время, покольку потенциал на затворе транзистора 8 усиления останется неизменным (от начала интервала усиления), его проводимость не изменяется, а это вызовет уменьшение потенциала на затворе ключевого транзистора 1, что приведет к возрастанию потенциала на выходе 12, т. е. облегчит считывание дифференциального сигнала. Когда дифференциальный сигнал достигнет величины, необходимой для считывания, произойдет правильное его считывание и усиление. Б .момент 5 времени на-шину 14 управления подается низкий потенциал и ключевые транзисторы 5 и 6 переходят в закрытое состояние. Выходы 12 и 13 заряжаются через транзисторы 7 и 8 усиления и усилитель считывания переходит в пассивный режим. С подачей высокого потенциала на шину 15 управления транзистор 9 установки переходит в открытое состояние и сили- тель считывания готов к новому циклу работы.

%

z

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Усилитель считывания на КМДП транзисторах | 1986 |

|

SU1376117A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель записи-считывания для запоминающего устройства на дополняющих мдп-транзисторах | 1977 |

|

SU739643A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Uio

Uii

Ufo

идиф

%

ue

Фиг. г

| Патент США № 4223394, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-04—Подача