(54) УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАИЦЕГО УСТРОЙСТВА НА ДОПОЛНЯЮЩИХ МДП-ТРАНЗИСТОРАХ

,.

Изобретение относится к вычислительнсй технике и может быть использовано при построении микромощных запоминающих устройств на дополняющих МДП-транзисторах.

Известны усилители записи-считывания, построенные на основе ключа или триггера, в которых перед считьтванием выходы и Екоды закорачиваются С помощью специального транзистора tl и 2 .,о

Недостатком схемы таких усилителей является сложность управления ее работой и критичность к фазовым соотношениям между управляющими сигналами.

Наиболее близким техническим реше- is нием к данному является усилительзаписи считывания для запоминающего устройства на дополняющих МДП-транзисторах, содержащий четыре усилительных транзис тора, включенных по триггерной схеме, два 20 нагрузочных транзистора, истоки которых подключены к шине питания и к истокам Двух установочных транзисторов;, стоки ко

торых соединены с соответствующими сто- ками усилительных транзисторов и со сто ками двух транзисторов сброса, истоки ко торых подключены к щине нулевого потенциала и к истокам одних усилительных транзисторов, стоки нагрузочньрс транзисторов соединены с истоками других усилительных транзисторов, и две шины управления, соединенные с затворами установочных транзисторов и с затвором дополнительного транзистора 3 .

Недостатком известного усилитоля записинсчнтывания является большое число транзисторов в нем, сложность схемы, большая площадь на кристалле и нешасокое быстродействие в режиме записи.

Целью изобретения является увеличение быстродействий и упрощение усилителя.

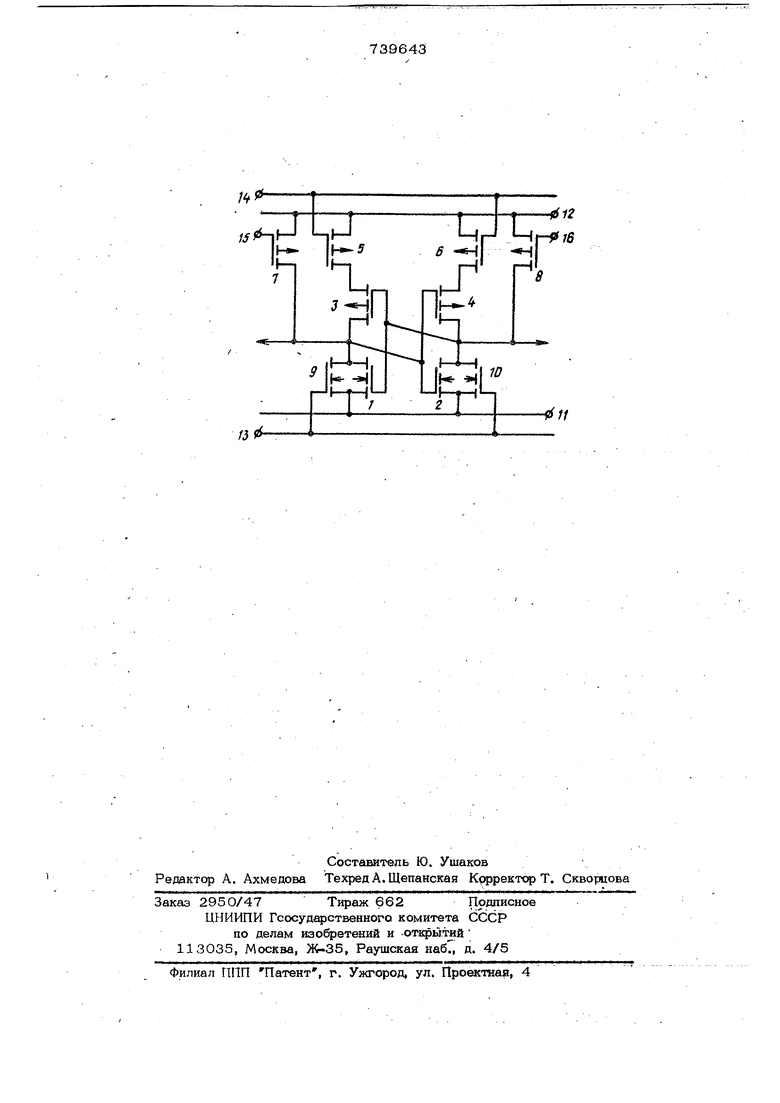

Поставленная цель достигается тем, что в усилителе записи-считывания первая щина управления подключена к затворам транзисторов сброса, вторая - к затворам нагрузочных транзисторов, а затворы уста3.7 новочных транзисторов соединены соответс венно со входом установки и со входом сброса усилителя. Схема усилителя записи-считывания npefri ставлена на чертеже и содержит усилитель ные транзисторы 1-4, нагрузочные транзисторы 5 и 6, установочные транзисторы 7 н 8, транзисторы 9 и 10 сброса, шины 11 нулевого потенциала, питания 12, первую 13 и вторую 14 управления, а также IS установки и 16 сброса. Усилитель записи-считывания работает, следующим образом. В режиме хранения напряжение на шинах 13-16 соответствует уровню логичеокой единицы, так что транзисторы 9 и 10 открыты, а транзисторы 5-8 закрыты, и на выходах усилителя поддерживается напряжение логического -нуля... В режиме считывания транзисторы 7 и 8 остаются закрытыми. Первоначально сигнал логического нуля подается на шину 13,запирая транзисторы 9 и 10. Узлоъые емкости на выходах триггера изолированы от источников питания и одна из них начинает заряжаться током считывания от выбранной ячейки памяти, которая через дополнительные транзисторы в памяти под ключена к выходам усилителя записи-считывания. После того как напряжение на одном из выходов усилителя превысит некоторую величину (разбаланс усилителя), на,вторую шину 14 управления подается сигнал логического нуля и открываются нагрузочные транзисторы 5 и 6. После этого начинается форсированные заряд емкостей на выходах усилителя через последовательно соединенные транзисторы 3,5 или 4, 6 и регенеративный процесс, обеспечивающий в случае предварительного установления на выходах необходимого разбаланса, быстрое переключение триггера в требуемое состояние. После окончания считывания сначала запираются тран зисторы 5 и 6, а затем о-тираются транзисторы 9 и 10, обеспечивая установку .усилителя в исходное состояние. В режиме записи запираются транзисто ры 9. и 10 и отпирается один из транзиоторов 7 Или 8 подачей сигнала логического нуля на один из входов 1,5 или 16 в зависимости от кода записываемой инфорг 43 шины 14 в режиме замации. Состояние писи безразлично. В случае, если размеры,,,,. транзисторов 7 и 8 имеют достаточную величину, происходит принудительная установка усилителя в требуемое состояние и последующая запись этой информациии в выбранную ячейку памяти. В ряде случаев, при незначительном раэбросе параметров транзисторов и строгом соблюдении фазовых соотношений между управляющими сигналами,допускается объединять шины 13 и 14. Предлагаемый усилитель записи-считывания имеет на два транзистора меньше и проще, чем известный усилитель. зобретения Формула Усилитель записи-считывания для запоминающего устройства на дополняющих МДП-транзисторах, -содержащий четыре усилительных транзистора, включенньгх. по триггерной схеме, два нагрузочных транзистора, истоки которых подключены к Ш№не питания и к истокам двух установочных транзисторов, стоки которых соединены с соответствующими стоками усилительных транзисторов и со стоками двух транзио- торов сброса, истоки которых подключены, к шине нулевого потенциала и к истокам одних усилительных транзисторов, стоки нагрузочных транзисторов соединены с истоками других усилительных транзисторов, и две шины угфавления, отличающийся тем, что, с целью увеличения быстродействия и упрощения усилителя, первая шина управления подключена к затворам транзисторов сброса, вторая к затворам нагрузочных транзисторов, а затворы установочных транзисторов соединены соответственно со входом установки и со нходом сброса усилителя. Источники информации, принятые во внимание при экспертизе 1.Патент Франции № 2317497, кл. а 11 С 11/40, 1974. 2. 3. oi etale ., SC 5, 1976, .3. Электроника, 1975, № 15, пер. с нгл., с. 47-53 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

Авторы

Даты

1980-06-05—Публикация

1977-11-02—Подача