Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения пре- образователей для вычислительных и измерительных устройств.

Цель изобретения - упрощение преобразователя.

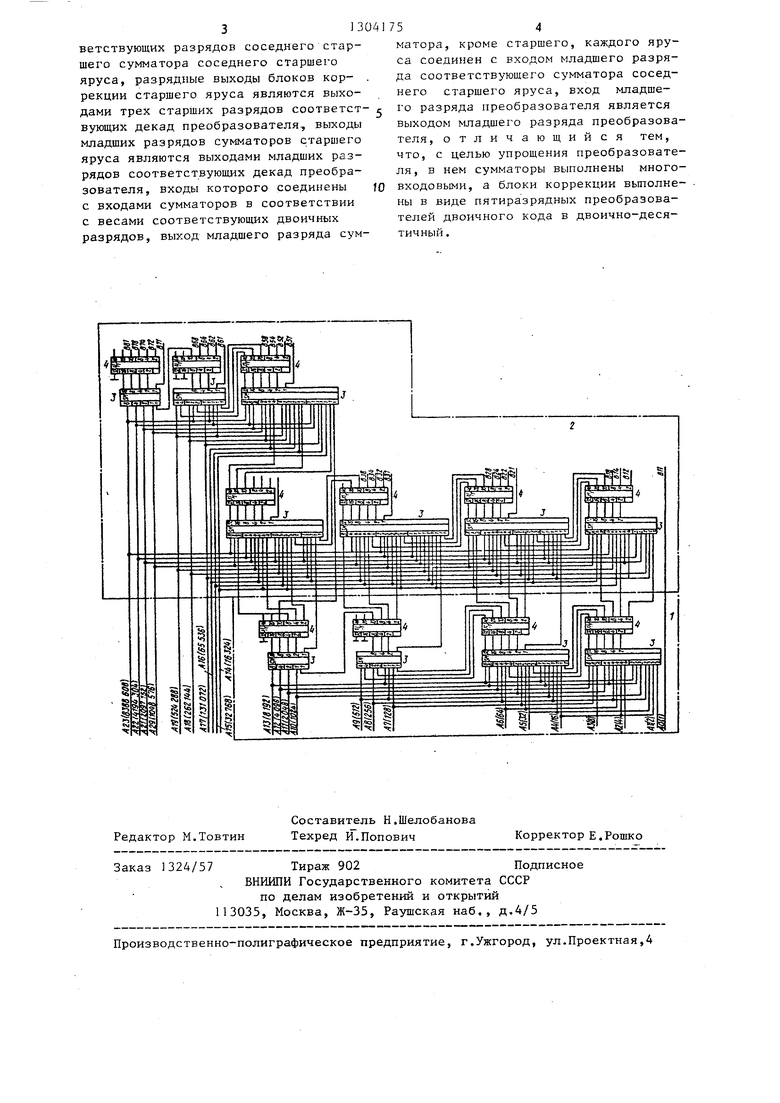

На чертеже представлена блок-схема предлагаемого преобразователя 24-разрядного двоичного кода«

Преобразователь содержит суммирующие ярусы 1 и 2, каждый из которых состоит из сумматоров 3 и блоков 4 коррекциио

Первый ярус Содержит-декады, в каждую из которых входит 4-разрядный многовходовой сумматор, выходы которого подключены к соответствующим входам преобразователя двоичного кода в двоично-десятичный данной декады 1-2-4-8. Разрядность по входу таких преобразователей равна 6. Младший разряд изменений не претерпевает. К входам сумматоров каждой декады первой ступени подключены ответвления младших 14-разрядных входов двоичного кода. Разветвления сделаны в соответствии с весами двоичных разрядов.

Для преобразования разрядов с 14-го по 23-й входного двоичного ко- да используется второй ярус преобразования. Он состоит из 4-х декад, в каждую из которых также входит 4- разрядный многовходовой сумматор, выходы которого подключены к соответствующим входам преобразователей кода данной декады. К входам сумматора подключены ответвления разрядных входов и выходы преобразователей кода, соответствующих декад первого яруса. Таким образом разводкой разрядных входов достигается преобразование веса каждого двоичного разряда в дво- ично-десятичньй код, при этом ответвления группируются по декадам, Двоичные коды внутри каждой декады суммируются на двоичном сумматоре, выходной код которого вновь подвергается двоично-десятичному кодированию на преобразователе кода данной декады. Старшие разряды преобразователя кода имеют вес 10 и переносятся на сумматор последующей , Млад10

15

20

используемых преобразователей кода в каждой декаде.

Построение многовходовых сумматоров выполнено на основе 2- и 4-разрядных сумматоров. При этом используется следующее соответствие между входными и выходными разрядами сумматоров :

35,4., 3S, +2S, - для 2-разрядного сумматора;

S,+S,j+S,+S4+S 5 - для 4-разрядного сумматора,

где S; 2 .

Тогда например, для второй декады преобразователя сумматоры вводятся следующим образом:

7S, +

5S,j MS, +284 +38 +683+28

S, +282+7834-284

n

8,+28 +38 +284+85J2

25 S,+28,+8,+8 +285-i 8, +8,+8 +84+85+8.

В каждой из трех декад допустима замена пары 2-разрядных сумматоров на один 4-разрядный. При этом схема

30 предлагаемого преобразователя содержит такое же количество интегральных схем, что и схема известного, однако йместо интегральных схем преобразователей кода используют более простые

эг и дешевые интегральные схемы 2-разрядных сумматоров.

Формула изобретения

Q Преобразователь двоичного кода в

двоично-десятичный, содержащий груп- . пу упорядоченных по старшинству суммирующих ярусов возрастающей разрядности, каждый из которых содержит iT

45 группу сумматоров и группу блоков коррекции, входы которых соединены с выходами всех разрядов, кроме младшего, соответствующих сумматоров, разрядные выходы блоков коррекции соединены

50 с входами соответствз ющих разрядов сумматора соседнего старшего яруса, а выходы переноса блоков коррекции, кроме последнего, в каждом суммирующем ярусе соединены с входами соот- шие разряды 1-2-4-8 являются выходным 55 ветствующих разрядов соседнего стар- кодом данной, декады. Второй ярус поз- шего сумматора того же яруса, выходы воляет провести преобразование 10 переноса старшего блока коррекции, старших разрядов двоичного кода при каждого кроме последнего, суммирую- сохранении ограниченной разрядности щего яруса соединены с входами соот

используемых преобразователей кода в каждой декаде.

Построение многовходовых сумматоров выполнено на основе 2- и 4-разрядных сумматоров. При этом используется следующее соответствие между входными и выходными разрядами сумматоров :

35,4., 3S, +2S, - для 2-разрядного сумматора;

S,+S,j+S,+S4+S 5 - для 4-разрядного сумматора,

где S; 2 .

Тогда например, для второй декады преобразователя сумматоры вводятся следующим образом:

7S, +

5S,j MS, +284 +38 +683+28

S, +282+7834-284

n

8,+28 +38 +284+85J2

25 S,+28,+8,+8 +285-i 8, +8,+8 +84+85+8

В каждой из трех декад допустима замена пары 2-разрядных сумматоров на один 4-разрядный. При этом схема

30 предлагаемого преобразователя содержит такое же количество интегральных схем, что и схема известного, однако йместо интегральных схем преобразователей кода используют более простые

эг и дешевые интегральные схемы 2-разрядных сумматоров.

Формула изобретения

Q Преобразователь двоичного кода в

двоично-десятичный, содержащий груп- . пу упорядоченных по старшинству суммирующих ярусов возрастающей разрядности, каждый из которых содержит iT

45 группу сумматоров и группу блоков коррекции, входы которых соединены с выходами всех разрядов, кроме младшего, соответствующих сумматоров, разрядные выходы блоков коррекции соединены

50 с входами соответствз ющих разрядов сумматора соседнего старшего яруса, а выходы переноса блоков коррекции, кроме последнего, в каждом суммирую313041

ветствующих разрядов соседнего старшего сумматора соседнего старшего яруса, разрядные выходы блоков кор- . рекции старшего яруса являются выходами трех старших разрядов соответст- вующих декад преобразователя, выходы младших разрядов сумматоров старшего яруса являются выходами младших разрядов соответствующих декад преобразователя, входы которого соединены fo с входами сумматоров в соответствии с весами соответствующих двоичных разрядов, выход младшего разряда сум754

матора, кроме старшего, каждого яруса соединен с входом младшего разряда соответствующего сумматора соседнего старшего яруса, вход младшего разряда преобразователя является выходом младшего разряда преобразователя, отличаюш,ийся тем, что, с целью упрощения преобразователя, в нем сумматоры выполнены много- входовыми, а блоки коррекции выполнены в виде пятиразрядных преобразователей двоичного кода в двоично-десятичный .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501277A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении вычислительных и измерительных устройств. Цель изобретения - упрощение преобразователя. Поставленная цель достигается тем, что комбинационный преобразователь содержит группу суммирующих ярусов, в каждый из которых входит группа многовходовых сумматоров и группа блоков коррекции, причем блоки коррекции -выполнены на 5-разрядных преобразователях двоичного кода в двоично-десятичный, 1 ил. 00 о СП

Редактор М.Товтин

Составитель Н.Шелобанова Техред и. Попович

Заказ 1324/57

Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Е.Рошко

| Авторское , свидетельство СССР № 960794, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3705299, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-29—Подача