Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислителях для определения величины амплитуды и фазы сигнала, представленного его квадратурными сосТав ляющими.

Цель изобретения - повьшение быстродействия вычисления амплитуды и фазы за счет табличной организации величины второго этапа при реализации рекуррентных соотношений по алгоритму Волдера и расширение функциональных возможностей за счет возможности вычисления фазы, на всем диапазоне ее представления.

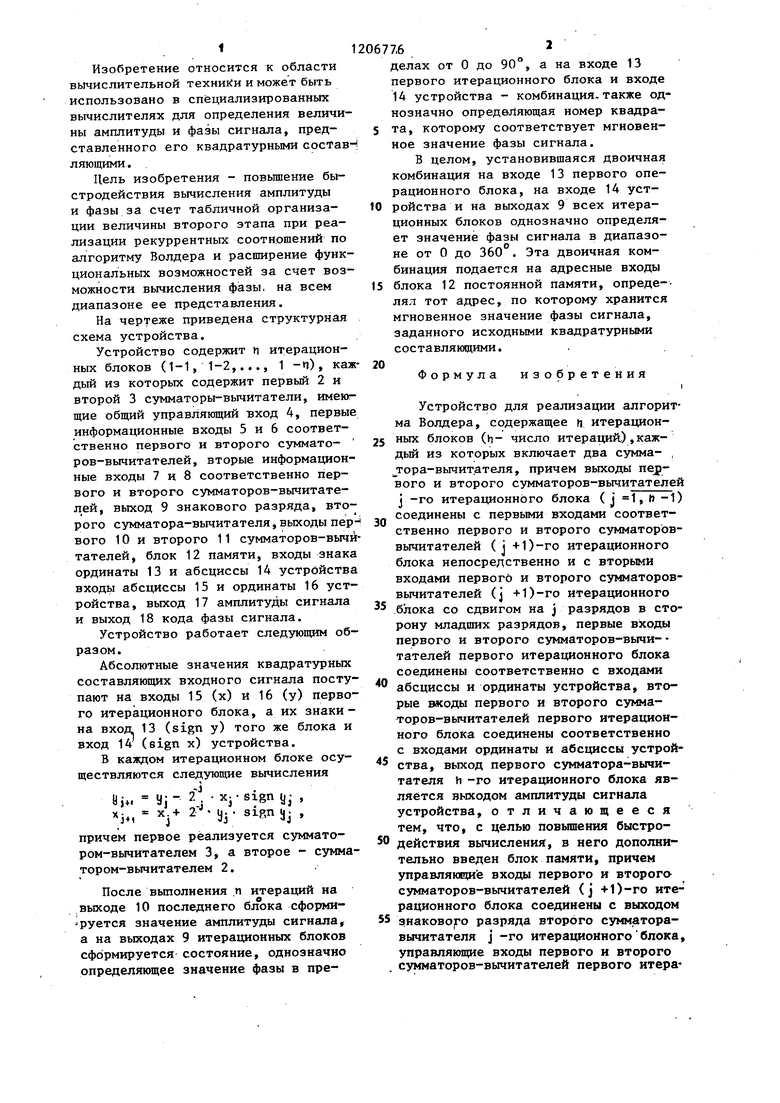

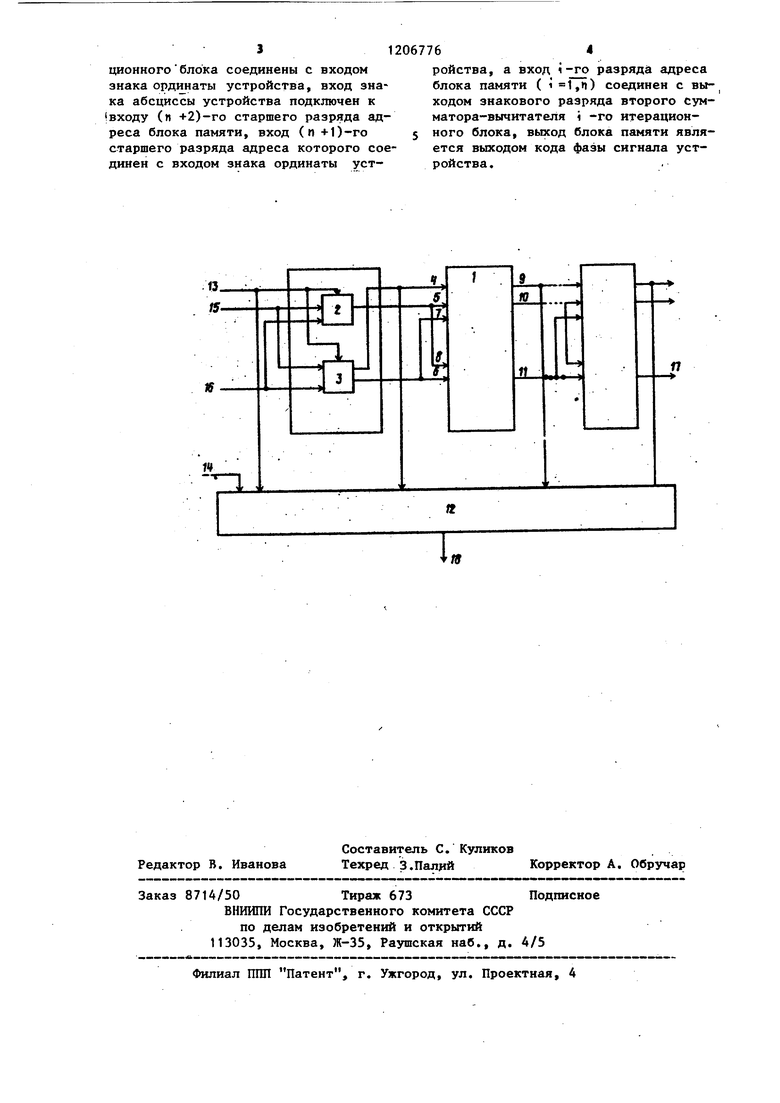

На чертеже приведена структурная схема устройства.

Устройство содержит h итерационных блоков (1-1, 1-2,..., 1 -п), каждый из которых содержит первьш 2 и второй 3 сумматоры-вычитатели, имеющие общий управляющий вход 4, первые информационные входы 5 и 6 соответственно первого и второго суммато- ров-вычитателей, вторые информационные входы 7 и 8 соответственно первого и второго сумматоров-вычитате- лей, выход 9 знакового разряда, второго сумматора-вычитателя, выходы пер вого 10 и второго 11 сумматоров-вьий тателей, блок 12 памяти, входы знака ординаты 13 и абсциссы 14 устройства входы абсциссы 15 и ординаты 16 устройства, выход 17 амплитуды сигнала и выход 18 кода фазы сигнала.

Устройство работает следующим образом.

Абсолютные значения квадратурных составляющих входного сигнала поступают на входы 15 (х) и 16 (у) первого итерационного блока, а их знаки- на вход 13 (sign у) того же блока и вход 14 (sign х) устройства.

В каддом итерационном блоке осуществляются следующие вычисления

И. У|- 2j -x.-signi,- , и. j- 2 ;Uj- siRnijj , причем первое реализуется суммато- ром-вычитателем 3, а второе - сумма- тором-вычитателем 2.

После вьгаолнения п итераций на выходе 10 последнего блока сформи- Руется значение амплитуды сигнала, а на выходах 9 итерационных блоков сформируется состояние, однозначно определяющее значение фазы в пре

5

0

5

делах от О до 90 , а на входе 13 первого итерационного блока и входе 14 устройства - комбинация-также однозначно определяющая номер квадра- та, которому соответствует мгновенное значение фазы сигнала.

В целом, установившаяся двоичная комбинация на входе 13 первого операционного блока, на входе 14 устройства и на выходах 9 всех итерационных блоков однозначно определяет значение фазы сигнала в диапазоне от О до 360 . Эта двоичная комбинация подается на адресные входы блока 12 постоянной памяти, опреде-- лял тот адрес, по которому хранится мгновенное значение фазы сигнала, заданного исходными квадратурными составляющими.

Формула изобретения

I

Устройство для реализации алгоритма Болдера, содержащее ц итерационных блоков (h- число итераций),каждый из которых включает два сумма- , .тора-вьиитателя, причем выходы первого и второго сумматоров-вычитателей j -го итерационного блока (j 1,ft -1) соединены с первыми входами соответственно первого и второго сумматоров- вычитателей (j +1)-го итерационного блока непосредственно и с вторыми входами первого и второго сумматоров- вычитателей ( -н1)-го итерационного блока со сдвигом на j разрядов в сторону младших разрядов, первые входы первого и второго сумматоров-вычи-- тателей первого итерационного блока соединены соответственно с входами абсциссы и ординаты устройства, вторые входы первого и второго сумматоров-вычитателей первого итерационного блока соединены соответственно с входами ординаты и абсциссы устройства, выход первого сумматора-вычитателя h -го итерационного блока является выходом амплитуды сигнала устройства, отличающееся тем, что, с целью повьшения быстродействия вычисления, в него дополнительно введен блок памяти, причем управляющие входы первого и второго- сумматоров-вычитателей (j )-го итерационного блока соединены с выходом знакового разряда второго сумматора- вычитателя j -го итерационного блока, управляющие входы первого и второго сумматоров-вычитателей первого итера0

5

0

5

0

5

ционного блока соединены с входом знака ординаты устройства, вход знака абсциссы устройства подключен к ОБХОДУ (п +2)-го старшего разряда адреса блока памяти, вход (п +1)-го старшего разряда адреса которого соединен с входом знака ординаты уст

Редактор В. Иванова

Составитель С. Куликов

Техред 3.Палий Корректор А. Обручар

8714/50Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Филиал ПШ1 Патент, г. Ужгород, ул. Проектная, 4

12067764

ройства, а вход (-го разряда адреса блока памяти ( i 1,п) соединен с выходом знакового разряда второго сум- матора-вычитателя i -го итерацион- 5 ного блока, выход блока памяти является выходом кода фазы сигнала устройства.

Т,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для реализации алгоритмаВОлдЕРА | 1978 |

|

SU813421A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для вычисления функций вида @ и @ @ | 1984 |

|

SU1249511A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

Устройство относится к области вычислительной техники и позволяет сократить время вычисления амплитуды и фазы за счет табличной организации величины второго этапа при реализации рекуррентных соотношений по алгоритму Волдбра, при этом фаза вычисляется во всем диапазоне ее представления. Устройство содержит и итерационных блоков, каждый из которых содержит два сумматора-вычита- теля и блок памяти. После выполнения м итераций на выходе первого сумматор а-вычитателя итерационного блока сформируется значение амплитуды сигнала, на выходах знакового разряда итерационных блоков сформируется состояние, однозначно определяю- :щее значение фазы от О до 90, а код на входах ординаты и а бсциссы определяет номер квадранта. 1 ил. IND о О) ч1 Од

| Балков В.Д., Смолов В.Б | |||

| Аппаратурная реализация элементарных, функций в ЭВМ, Л.: изд-во ЛГУ, 1975, с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Устройство для реализации алгоритмаВОлдЕРА | 1978 |

|

SU813421A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-23—Публикация

1984-08-28—Подача