Изобретение относится к вычислатель- ной технике и может быть использовано Для вычисления элементарных функций, отображаемых с помощью итерационных алгоритмов Волдера. Известны устройства для вычисления элементарных функций, реализующие алгоритмы Волдера, содержащие комбинационные сумматоры-вычитатели, регистры;памяти и узлы управления и синхрсии- аации i и 2 . Наиболее близким аналогом является устройство для реализация алгоритма Волдера, содержащее блоки управления tt памяти, сумматоры-вьгаигатеяи, узлы сдвига, регистры и коммутаторы р. Недостатком этого устройства является сложная структура, обусловленная не, однородностью входящих в него узлов и потребностью в синхронизации для реали зации многотактного вычислительного процесса. Время вычисления (Т) в таком устройстве определяется не .только време нем такта суммирования ( t ), но и потерями времени на пересылку результатов каждого такта суммирования в соответствующие регистры и обращение к памяти (1ц ), т.е. (Vtn), где п - колкчестао тактов (итераций). Цель изобретения - псюышение & 1стродействия в однородности структуры устройства. Оля достижения поставленной цели устройство построено в виде п последовательно соединенных итерационных блоков, каждый из которых содержит три сумматоравычитателя и коммутатор, при этом управляющие входы сумматоров-ВЁпитателей каждого итерационного блока подключены к выходу коммутатора, выходы первого и второго сумматора-вычитателей ( -го итерационного блока ( 1,...,п -1) соединены с Первыми входами, с.оответственно первого и второго сумматоров-вычитате- лей (i +1)-го итерационного блока непосредственно, а со вторыми входами соотвегсгвенно второго и первого сумматсроввычитателей (i+1)-го итерационного блока - со сдвигом на i разрядов, первые входы первого и второго сумматоров-вычитателей первого игерадионного блрка соединены соответственнс с первым и вторым, а вторые входы соответственно

со вторым и первым информационными входами устройства, первый вход третьего сумматора-вычйтателя первого итерационного блока соединен с третьим информационным входом устройства, выход третьего сумматора-вычитателя каждого i -го итерационного блока соединен с первым входом третьего сумматора-вычитатепя (-i+1)-го. итерационного .бвока, выходы знаковьрс разрядов второго и третьего сумматоров-вычитателей каждого -i -го итерационного блока соединены с инфqэмaциoнными входами ком мутатора ()-ro итерационного блока, управляющий вход коммутатора каждого j -го итерационного блока { j 1,,.,п ) соединен с управляющей шиной устройств второй вход третьего сумматора-вычитагеля j -го итерационного блока подключен к соответствующему входу константы устройства, входы коммутатора первого v тepaциoннoгo блока соединены со знаковыми входами устройства, выходы сумматоров-вычйтателей п -го итерационного блока с информационными выходами устройства.

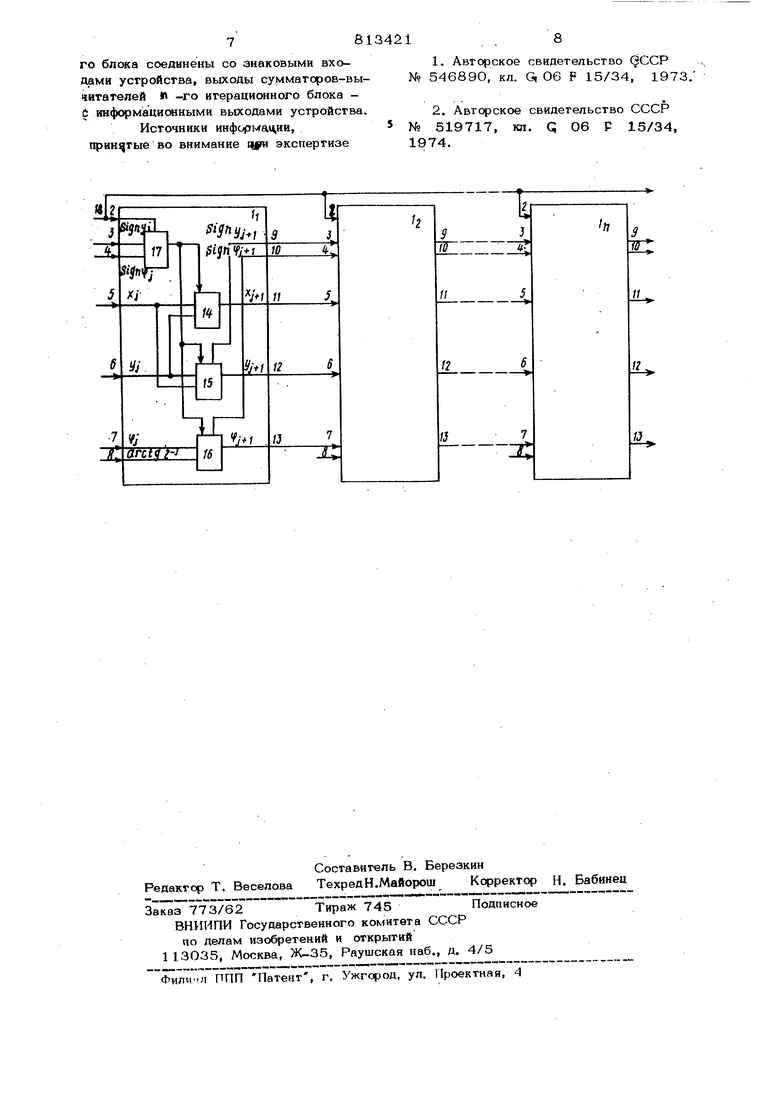

На чертеже представлена схема устройства для реализации алгоритма ВолДера.

Устройство содержит п итерационHbtx. блоков 1(1, 1,,,.., l), каждый из которых имеет входы 2-8 и выходы 9-13, В состав каждого итерационного блока 1 входят сумматоры-вычитатепи 14-15 и коммутатор 17, Ко входам 2 всех блоков 1 подключена управляющая шина 18 устройства.

На входы 3 и 4 каждого j го итерационного блока 13 подаются значения Y- и SicrnYj (входы 3 и 4 первого итерацисиного блока 1-,, на которы подаются значения s-intr -, подключены к знаковым входам устройЬтва, а входы 3 н 4 всех последующих итерационных блоков 1 соединены с выходами 9 и 10 соответственно предыдущих итерационных блоков 1). Со входов 3 и 4 каждого блока 1 значения .; . и Чз поступают на информационны входы коммутатора 17 данного блока 1 На входы 5-7 каждого блока if поступают значения Xj , 4.J и Ч ., (входы 57 блока 1 , на котфые поступают начальные значения Х , и 4L :;оединены с информационными в:;:одами устройства, а входы 5-7 всех последующих итерационных блоков 1 соединены с выходами 11-13 соответственно предыдущих итерационных блоков 1). Вход 7 каждого блока 1 j , на который подается значение константы arc-ts l , подключен к соответствующему входу константы устройства. Выходы 11-13 каждого блока 1-J , на которых образуются

+ 1 и 4j- +1 соезначения Xj +1, Y

динены с выходами сумматоров-вычйтателей 14-16, входящих в данньй блок 1, а выходы 9 и 10 (на котсрых образуются значения Siflf п У +1 и +1)с выходами знаковых разрядов суммагоров-вычитателей 14 и 15. Выходы 1113 блока 1. соединены с информационными выходами устройства.

Рассмотрим работу устрсйства на примере вь числения тригонометрических, фунций sin Ч и 0054

Вычислительный процесс определяется .системой итерационных уравнений З..- ЗЦпЧ,oirctcg ;

., ..

lX.,-,-Xj 5icjn4., , . (lj где 1 - 1,2,.,., V .

Начальными условиями для j -го итерационного блока 1j для вычисления ( 3+1)-го шага процесса (1) явл$потся: на входе 1 - сигнал, обеспечиваюший пропускание на выход KOMMyTaTqaa 17 сигнала ./; кэ входе 5 -

код )(.j8 поступающий на вход 5 каждого блока Л. 4. начиная со второго с . выхода сумматора-вычитателя 14 предыдущего блока Ij., на вход 15 первого блока 1 код X -J поступает с первого информационного входа устройства; на входе 6 - код Yj , поступающий на вход 6 каждого блока Ij, начиная со второго, с выхода сумматора-вычитателя 14 предыдущего блока lj на вход 6 первого блока 1-, код Y. поступает со второго информационного входа устройства; на входе 4 - сигнал Vj , поступающий на вход 4 каждого блока 1 j , начиная со второго, с выхода знакового разряда сумматора-вычятателя 16, предыдущего блока (T а на вход 4 первого блока 1 - со знакового входа устройства; на входе 7 - код , поступающий на вход 7 каждого блока l-j , начиная со второго, с выхода сумматора- вычигателя 16 предыдущего блока lj--( а на вход первого блока 1 с третьего информационного входа устройства; на входе 8 - код константы arciqj 2.Код Xj со входа 5 блока Ij поступает на вход сумматора-вычитателя 14 непосредственно, а на вход сумматора-вычитателя 15 - со сдвигом на 1 .-1 раз рядов, т.е. умноженный на.2 . Код j со входа 6 блока 1 поступает на вход сумматора-вычитателя 15 непосредственно, а на вход сумматфа- ычитателя 14- со сдвигом на j --i разрядов, т.е. умноженный на 2 Коды jf и drctqj (юступают на входы сумматора-вычнтателя 16 непосредственно. Наличие сигнала О на выходе комму татора 17 ( SiOjn/Pj +1) обеспечивает настррйку сумматоров-вычитатепей 15 и 16 на выполнение операции вычитания, а сумматора-вычитателя 14 на выполнение операции сложения. Наличие сигнала 17 на выходе коммутатора 17 Ы( -1) обеспечивает противоположную постройку. Таким образом, сумматор-вычитатель 14 вычисляет выражение «)sHocr..3r, сумматор-вычитатель 15 - выражение Г Я Г сумматор-вычитатель 16 - вьфажение ,Vj.-si i«tf-arttcc а -. После поступления на информационные jBJcpnbi устройства начальных значений У , и з. иа выходах каждого j блока :« по окончании переходных процессов в сумматорах-вьиигателях 14- 16 сформируются значенияXvjjY. . Количество блоков 1 устройства h равно числу требуемых шагов итерацнониого процесса (1). ЗначенияХ«, Чпчч с Выходов 11-13 п -го блока 1 j, выводятся на инфсрмационные выходы устрсйства. Привычислениифункции Klfx и ( взаимодействие блоков устрсйства аналогично вышеописанному, и на настройке сумматоров-вычитателей 14-16 осуществляется величиной sicQn Yj-в соответствии с вьшажениями J i -s4« va -i: ,.,.. X,-. j Общее время вычислений в данном уст ройстве равно To -n-tj. и определяется 8 16 Для каждого блока 1 только временем сукп ирования (tc ). Особенностью предлагаемого устройства является полное отсутствие элементов синхронизации, что определяется исключением элементов памяти. Таким образом, предлагаемое устройство однородно по структуре, содержит только комбинационные схемы и обладает более быстродействием по сравнению с ii3Beetным. Формула изобретения Устройство для реализации алгоритма Волдера, содержащее сумматоры-вычитатели и коммутаторы, отличающееся тем, что, с целью повышения быстродействия и однородности структуры устрсЛства, оно состоит из « итераци(жных блоков (п -количество итераций гфи вычислениях), каждый из которых содержит три сумматора-вычитателя и коммутатор, причем управляющие входы сумматоров-вьиитателей подключены к выходу коммутатора, выходы первого и второго сумматора-вычислителен i -го итерационного блока ( i 1,..,| ri -1) соединены с первыми входами соответственно первого и второго сумматоров-вы- читателей (i +1)го итерационного блока непосредственно, а со вторыми входами соответственно второго и первого сумматоров-вычитателей (+1)-го итерационного блока - со сдвигом на т разрядов, первые входы первого и второго сумматоров-вычитателей первого итерацйоннс1го блока соедянены соответственно с первым и вторым, а входы соответственно со вторым и первым ннформационнымн входами устройства, первый вход третьего сумматора-вычитателя первого итерационного блока соединен с третьим информационным входом устройства, выход третьего сумматора-вычитателя каждого i -го итерационного блока соединен с первым входом третьего сумматора-вычислителя{1 +1)-го итерацисиного блока, выходы знаковых разрядов второго и. третьего сумматоров-вычитатолей каж- дого i -го итерационного блока соединены с информац-ионными входами коммутатора ( i+ )-го итерационного блока, управляющий вход коммутатора каждого j -го итерационного блока ,...,h) соединен с управляющей шиной устройства, второй вход третьего сумматора-вычитателя j -го итерационного блока подключен к соответствующему- входу константы устройства, входы коммутатора первого итерационного блока соединены со знаковыми входами устройства, выходы сумматоров-вы|{итателей Л -го итерационного блока С информационными выходами устройства.

Источники информации, прин1}тые во внимание turn экспертизе

1.Авторское свидетельство QCCP

№ 546890, кл. GI 06 F 15/34, 1973.

2.Авторское свидетельство СССР

№ 519717, кл. q 06 Р 15/34, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для вычисления функций вида @ и @ @ | 1984 |

|

SU1249511A1 |

| Устройство для реализации алгоритма Волдера | 1984 |

|

SU1206776A1 |

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

.,

w

Sijn Xj

s

1Г

yj

12

J

VI

/J

JL

grcf у /--f

n

3 ЖГ

9 Г7Г

12

n

7

13

/J -X

Авторы

Даты

1981-03-15—Публикация

1978-09-06—Подача