Предлагаемое изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой фильтрации сигналов при реализации алгоритмов дискретного нреобразования Фурье или быстрого преобразования Фурье.

Целью изобретения является повышение быстродействия устройства.

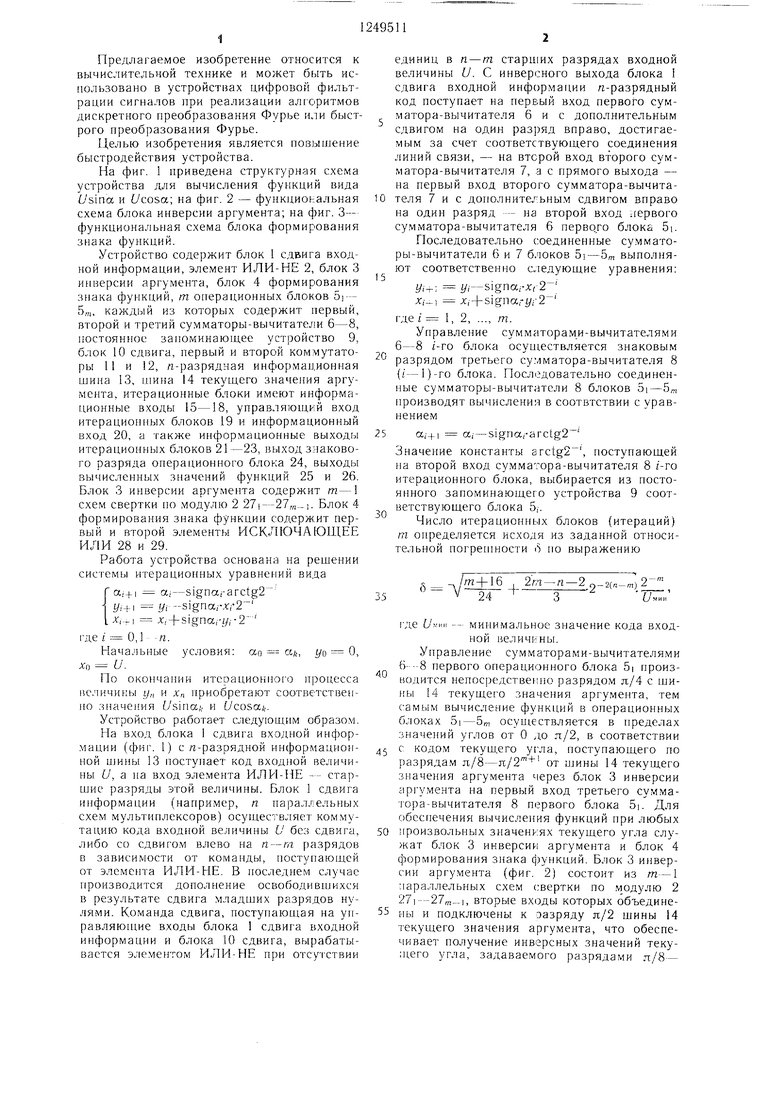

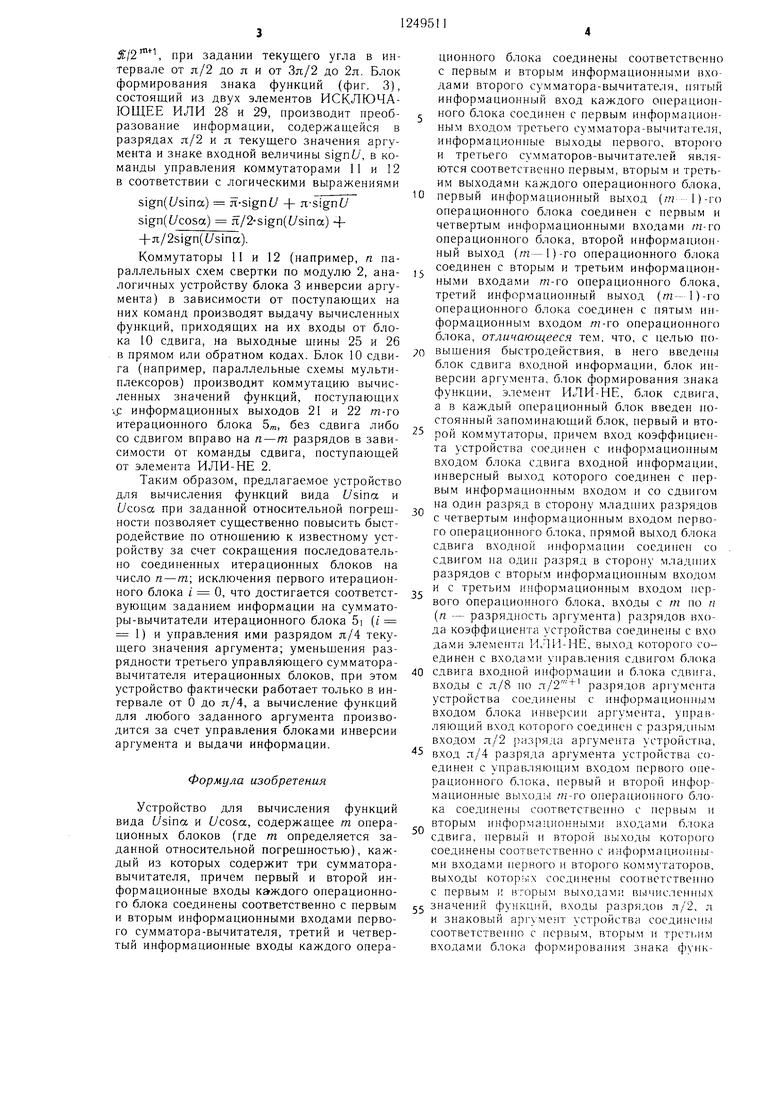

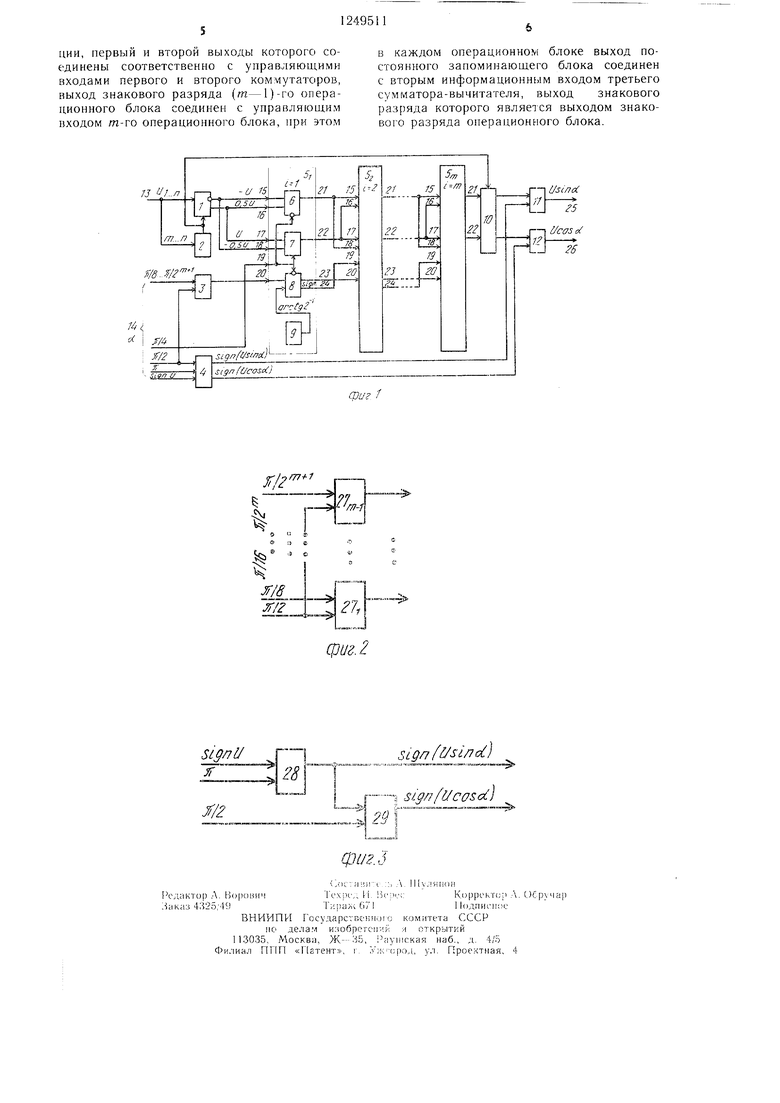

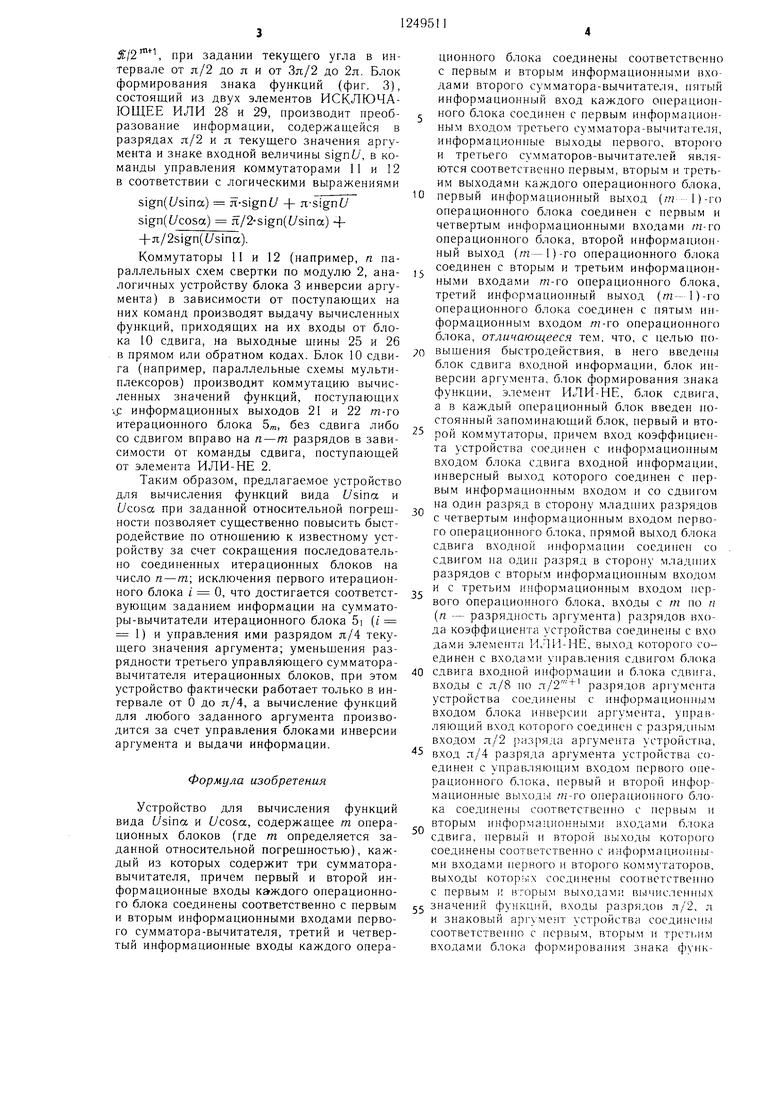

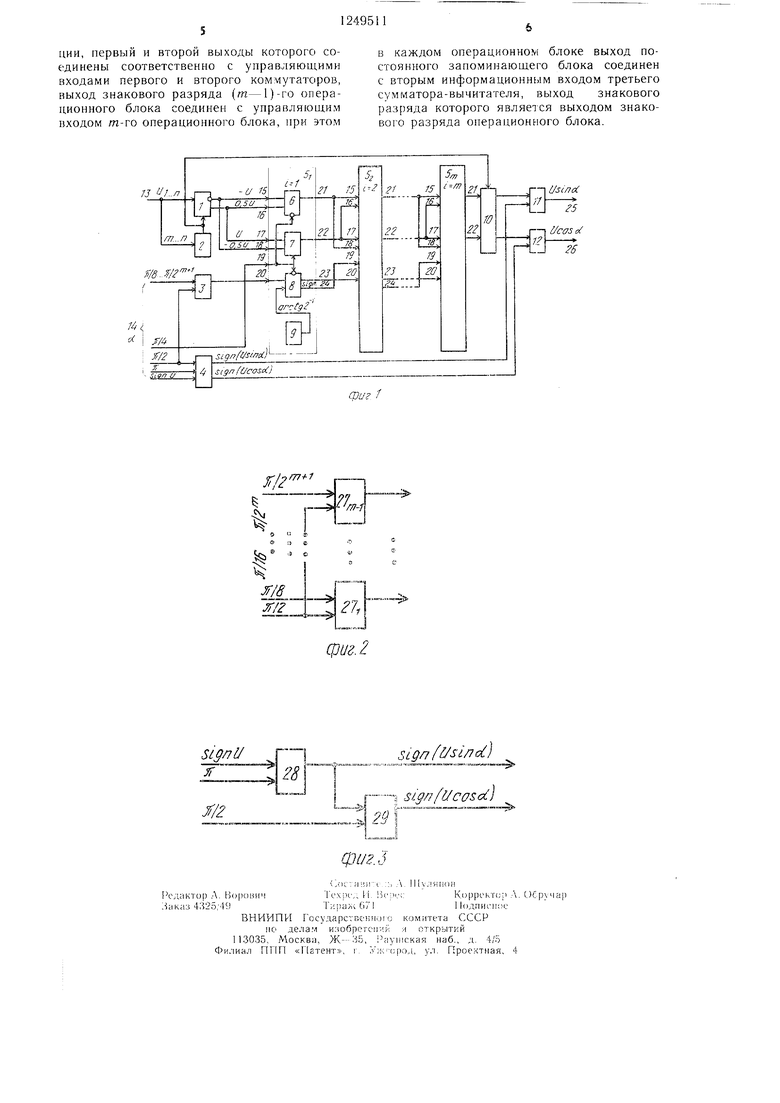

На фиг. 1 нриведена структурная схема устройства для вычисления функций вида L sina и Ucosa; на фиг. 2 - функциональная схема блока инверсии аргумента; на фиг. 3- функциональная схема блока формирования знака функций.

Устройство содержит блок 1 сдвига входной информации, элемент И.ЛИ-НЕ 2, блок 3 инверсии аргумента, блок 4 формирования знака функций, т операционных блоков 5i - 5,,j, каждый из которых содержит первый, второй и третий сумматоры-вычитатели 6-8, постоянное запоминающее устройство 9, блок 10 сдвига, первый и второй коммутаторы 1 и 12, п-разрядная информационная шина 13, пшна 14 текущего зпаче1.;ия аргумента, итерационные блоки имеют информационные входы 15-18, управляюплкй вход итерационных блоков 19 и информационный вход 20, а также информационные выходы итерационных блоков 21-23, выход знакового разряда операционного блока 24, выходы вычисленных значений функций 25 и 26. Блок 3 инверсии аргумента содержит т-1 схем свертки по модулю 2 271-27, Блок 4 формирования знака функции содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 28 и 29.

Работа устройства основана на решении системы итерационных уравнений вида

a. + i а.:-signararctg2 №-f-i У --signa,-. A-,-,.i z,4-signaryr2

где / 0,1 -п.

Нача. ИзНые условия: ао а, уо О, А о и.

По окончании итерационного процесса .чичины у,| и Хп приобретают соответственно .значения (/sina и UcosakУстройство работает следующ.им образом.

На вход блока 1 сдвига входной информации (фиг. 1) с п-разрядной информационной 13 поступает код входной величины и, а на вход элеме та ИЛР1-НЕ - - старшие разряды этой величины. лок 1 сдвига информации (например, п парал.пельных схем мультиплексоров) осун1.еств;1яет коммутацию кода входной величины U без сдвига, либо со сдвиго.м влево на п - т разрядов в зависимости от команды, поступающей от элемента ИЛИ-НЕ. В последнем случае производится дополнение освободив пихсн в результате сдвига младших разрядов нулями. Команда сдвига, поступающая на управляющие входы блока 1 сдвига входной информации и блока 10 сдвига, вырабатывается элементом ИЛИ-НЕ при отсутствии

единиц в п - т старших разрядах входной величины и. С инверсного выхода блока 1 сдвига входной информации «.-разрядный код поступает на первый вход первого сум- матора-вычитателя бис дополнительным сдвигом на один раз)яд вправо, достигаемым за счет соответствующего соединения линий связи, - на второй вход второго сум- матора-вычитателя 7, а с прямого выхода - на первый вход второго сумматора-вычита- теля 7 и с дополните/ ьным сдвигом вправо на один разряд - на второй вход первого сумматора-вычитателя 6 перво.го блока 5i. Последовательно соединенные сумматоры-вычитатели 6 и 7 блоков выполняют соответственно следующие уравнения:

у, + ; у,-signar r2 z,- X,- -signar

где г 1, 2, ..., т.

Управление сумматорами-вычитателями 6-8 /-го блока осуп1ествляется зпаковым разрядом третьего сумматора-вычитателя 8 (i-1)-го блока. Последовательно соединенные сумматоры-вычитатели 8 блоков 5i-5m производят вычисления в соотвтствии с уравнением

а,-+1 а, - signa,-arctg2

Значение константы arctg2 , поступающей па второй вход сумматора-вычитателя 8 /-го итерационного блока, выбирается из постоянного запоминающего устройства 9 соответствующего блока 5,.

Число итерационных блоков (итераций) rti онределяется исходя из заданной относительной погрепиюсти о по выражению

л - T/2L±1 д (п-т) V 24 3

( мни

где fy vui, -- минимальное значение кода входной величины.

Управление сумматорами-вычитателями 6- -8 первого операционного блока 5| нроиз- водится пеносредственпо разрядом я/4 с шины 4 текущего значения аргумента, тем самым вычисление функций в операционных блоках 5i-5„ осуществляется в пределах значений углов от О до л/2, в соответствии

5 с кодом текуш,его угла, поступающего по разрядам л/8-я/2 + от шины 14 текущего значения аргумента через блок 3 инверсии аргумента на первый вход третьего сум.ма- тора-вычитателя 8 первого блока 5|. Для обеспечения вычисления функций при любых

0 произвольных значениях текущего угла служат блок 3 инверсии аргумента и блок 4 формирования знака функций. Блок 3 инверсии аргумента (фиг. 2) состоит из т-1 :1араллельных схем свертки по модулю 2 27i-27ш и, вторые входы которых объедине5 ны и подключены к оазряду л/2 шины 14 текущего значения аргумента, что обеспечивает получение инверсных значений текущего угла, задаваемого разрядами л/8-

SJ2

m+i

при задании текущего угла в интервале от л/2 до л и от Зл/2 до 2л. Блок формирования знака функций (фиг. 3), состоящий из двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 28 и 29, производит преобразование информации, содержащейся в разрядах л/2 и л текущего значения аргумента и знаке входной величины signt/, в команды управления коммутаторами 11 и 12 в соответствии с логическими выражениями

sign(L sina) л-signt/ + лsigп6 sign(/ycosa) n/2-sign((ysina) -f- -л/2sign(L sina).

Коммутаторы 11 и 12 (например, п параллельных схем свертки по модулю 2, аналогичных устройству блока 3 инверсии аргумента) в зависимости от поступающих на них команд производят выдачу вычисленных функций, приходящих на их входы от блока 10 сдвига, на выходные пшны 25 и 26 в прямом или обратном кодах. Блок 10 сдвига (например, параллельные схемы мультиплексоров) производит коммутацию вычисленных значений функций, поступающих ,с информационных выходов 21 и 22 т-го итерационного блока 5т, без сдвига либо со сдвигом вправо на п-т разрядов в зависимости от команды сдвига, поступающей от эле.мента ИЛИ-НЕ 2.

Таким образом, предлагаемое устройство для вычисления функций вида f/sina и Ucosa при заданной относительной погрещ- ности позволяет существенно повысить быстродействие по отношению к известному устройству за счет сокращения последовательно соединенных итерационных блоков на число п - т; исключения первого итерационного блока / О, что достигается соответствующим заданием информации на суммато- ры-вычитатели итерационного блока 5 (i 1) и управления ими разрядом л/4 текущего значения аргумента; уменьшения разрядности третьего управляющего сумматора- вычитателя итерационных блоков, при этом устройство фактически работает только в интервале от О до л/4, а вычисление функций для любого заданного аргумента производится за счет управления блоками инверсии аргумента и выдачи информации.

Формула изобретения

Устройство для вычисления функций вида Us ina и Ucosa, содержащее т операционных блоков (где т определяется заданной относительной погрешностью), каждый из которых содержит три сумматора- вычитателя, причем первый и второй информационные входы каждого операционного блока соединены соответственно с первым и вторым информационными входами первого сумматора-вычитателя, третий и четвертый информационные входы каждого опера5

ционного блока соединены соответственно с первым и вторым информационными входами второго сумматора-вычитате.мя, пятый инфор.мационный вход каждого онерационного блока соединен с первым информационным входом третьего сумматора-вычитате.чя, информационные выходы первого, второго и третьего сумматоров-вычитателей являются соответственно первым, вторым и третьим выходами каждого операционного блока,

первый информационный выход (т 1)-го операционного блока соединен с первым и четвертым информационными входами /п.-го операционного блока, второй информационный выход (т-1)-го операционного блока соединен с вторым и третьим информационными входами т-го операционного блока, третий информационный выход (т- 1)-го операционного блока соединен с пятым информационным входом т-го операционного блока, отличающееся тем, что, с целью ноО вышения быстро;1ействия, в него введены блок сдвига входной информации, блок инверсии аргумента, блок формирования знака функции, элемент ИЛИ-НЕ, блок сдвига, а в каждый операционный блок введен постоянный запоминающий блок, первый и вто5 рой коммутаторы, причем вход коэффициента устройства соединен с информационным входом блока сдвига входной информации, инверсный выход которого соединен с первым информационным входом и со сдвигом на один разряд в сторону младших разрядов с четвертым информационным входом первого операционного блока, прямой выход блока сдвига входной информации соединен со сдвигом на один разряд в сторону младн1их разрядов с вторым информационным входом и с третьим информационным входом первого операционного блока, входы с т но п (п - разрядность аргумента) разрядов входа коэффициента устройства соединены с вхо дами элемента ИЛИ-НЕ, выход которого соединен с входами управления сдвигом блока

0 сдвига входной информации и блока сдвига, входы с л/8 по + разрядов apryMcirra устройства соединены с информациошн ш входом блока инверсии аргумента, управляющий вход которого соединен с разрядным входом л/2 |)нзряда apryNsenTa устройства,

5 вход л/4 разряда аргумента устройства соединен с управляющим входом первого операционного блока, первый и второй информационные выходы , /г-го операционного блока соединен1 1 соответственно с первым и вторым информационными входами б.юка сдвига, первый и второй выходы которого соединены соответственно с информационными входами первого и второго комм) таторов, выходы которь;х соединены соответственно с первым и вторым выходами вычисленных

5 значений функций, входы разрядов л/2, л и знаковый аргумент устройства соединены соответственно с первым, вторым li трет1ли1 входами блока формирования знака функ0

5

0

НИИ, первый и второй выходы которого соединены соответственно с управляющими входами первого и второго коммутаторов, выход знакового разряда (т-1)-го операционного блока соединен с управляющим входом т-го операционного блока, при этом

в каждом операционном блоке выход постоянного запоминающего блока соединен с вторым информационным входом третьего сумматора-вычитателя, выход знакового разряда которого является выходом знакового разряда операционного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для реализации алгоритма Волдера | 1984 |

|

SU1206776A1 |

| Устройство для реализации алгоритмаВОлдЕРА | 1978 |

|

SU813421A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Вычислительное устройство для поворота вектора | 1982 |

|

SU1109742A1 |

Изобретение относится к вычислительной технике и нредназначено для вычисления понарных нроизведений функций вида Uslna и Ucosa по алгоритму Волдера. Устройство содержит т последовательно соединенных итерационных блоков, состоящих из трех сумматоров-вычитателей и ПЗУ, блок сдвига входной информации, элемент ИЛИ-НЕ, блок инверсии аргумента, блок формирования знака функций, блок сдвига, первый и второй блоки выдачи информации и соответствующие связи. При этом блок инверсии аргумента состоит из т-1 параллельных схем свертки по модулю 2 и соответствующих связей. Кроме того, блок формирования знака функций содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующие связи, в данном устройстве повышение быстродействия осуществляется за счет сокращения на (п - т) последовательно соединенных итерационных блоков. Предлагаемое устройство может быть использовано в устройствах цифровой фильтрации при реализации алгоритма Волдера. 3 ил. sg (Л Ю 4 СО ел

7/77

1

I rci

фиг. 2

stgnU

УГ

28

т

V .о; : fi ни I. :: , . I Ч лянон

Релакто|) А. В()|К)вичТехрс,, 5c:ir;:Коррокт(;р Л. С.)

-5г1Каз 432о;4, Г;;)ал; 671I ioArinoiiiie

ВНИИПИ Государствеин.;) о комитета СССР

по делам и.чобретсник и откр:ыткй

113035, Москвп, Ж-Н5, 1 ау1пская наб., Д- 4/5

Филиал П11П «Патент, i У:к ч;рол, ул. Проектная, 4

stgr/J JfijT j

. ,..т „Л1 аг;;Е ттз1т.таэ™-.аг...лл±-|Т1Г1|Г,| I lijj.

-d signfUcosd

| Устройство для вычисления элементарных функций | 1973 |

|

SU546890A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации алгоритмаВОлдЕРА | 1978 |

|

SU813421A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1984-07-20—Подача