Изобретение относится к вычигии - ::о1.; ;е-;ь: ка i.;xo.ie 27, ::- r;:;i:i ) 3

гельной технике и может быть исаоль-ni:/-гпг,ка обра деилк ,ч намят: уст -зова}Ю для юстроения оиератнвньпс01Т.стьа на isxoiie 2В, с

за1юмина ся11,их устройстп ;;г дикзк-гчес- И1,;ч;;,11е три r,iT-;i:ia 2i, гт

ких элементах памяти, для ксторь;х;: р,;: :j--:ci;ie :K;i оГ;ра:; лМ1;;я -к ламя ;, необходима периоякчестоя per : г:о ;ства Нс: ныхс,ч,,: ,, с;;:: i-ia;i 56

iJfiH хранящейся ИНфОрмац1,И, напр,-:мер ; Чт DOO :к;/ч1т, jJj; :;in)) ;-::;о;;;; :;:к;

8 CHCTCNiax yiipaaneifflH fyitAKS.mi , ро- M--, И 25„ . ,,(ipoii liXfv: ia); :-;io-

ботамИ; устройствам-; машкннсй г;;;;а-- , ,-, .:nrT--. n. гчтгиат ; ,;,,:а 29, г:и,г::.о-;; :;7 vpp р,,;и;ака ,

Целью изобретения является ,аог Ы--пе:и::-ма на в,ыходе злемента 9,

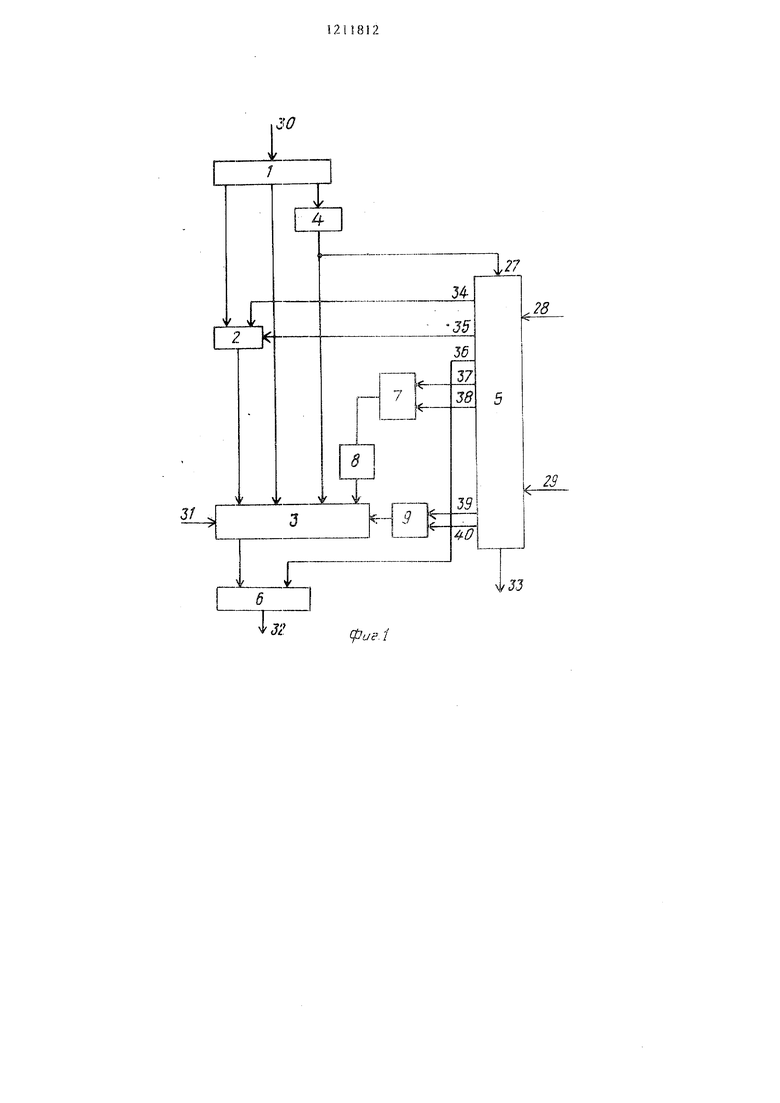

пение быстродействия устройства,г:г -;ял 53 оаз-лнкеиил яаанги п с-чит ;)Па фиг,1 представлена фуякииондл -;;;)н:,я ка пыхопг фсимироаато-)я Н, сиг

ная схема лредатагаёмого устройсгва; . 59 Зг есение к оегистр цанна фиГе 2 - фз кклиоН Зльная схемаi,, :.,,,, ,,„ ir-аа: У ;:ХИ

элока управления;, наиболее ппедпоч- , Ч1;,-;ка w-yii vvrrp j; -r,ixo-ii Т,

гительный вариант выполнения; на::., фм г , : , бо-;-а : ;/,:- сН -фиг. 3 временные диагсаг-п-гЫ:- пояс- ,,,,,-,,,,, ,,,,,q,,,„,|.J,i:|J-,, пб ) : ч/:-,-,; -

няюшие работу устрой :тл;1.

Устройство содержит (Фиг ,, li ре- - -:

гнстр a,peca5 мульти:п,11ексср 2, блок 3 ламяти, дешифратор 4, бпок :: унравлениЯз регистр о данные:,; элемент ИЛИ-НЕ 7,, фор1 шровате,л1Е 8 сил- налов „ : лемент И-НЕ Э,- -

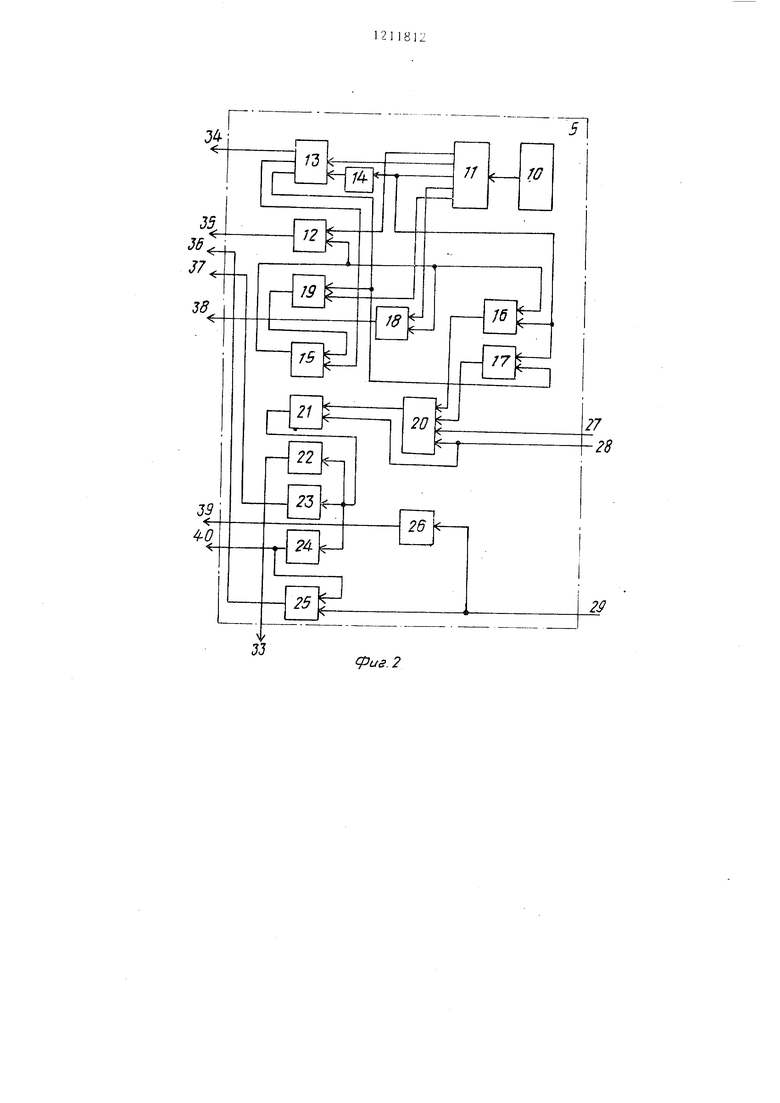

5 yiipa aneiKiK о,рер:;Ес ;т ( фкг ,/, i генерато : Ш и-П1ульсов„ форг:ирава -,,,,,,,, ,

тель i i синхроимл:/,1;ьсов , 3j:,:Me;: T i

И 2„ J 3,, o,ri:::veHT

триггер 15; з,{еме,ить И -И ; icr-ZG;

триггер 21 J форнировй)-е,г:11 22-2ч- :мт;

ротких импу,льсоз ; ;:)(ei,;:rh -i 2,5 и НЕ 26.

блока Ь унраБлен:- :-.. улоэ,

входы 28 i-i 29; ap;peci n--ii n:fnL- 30,,

инфорь ан,т-1онаь;е Bxo,i 3 и .::о,ц 3/. :„

управлкюяий зы:;сол, 33 j :: i rofsc ,fTia ,

, ij

выходы 34-40 блока ,5 - ::: -iiji cпик ..

Блох 3 намят:1:1 может :-и :троаи

на динаг.ическкх эле мен:; ах ла,мяти

,Ъ I I I IV 1 .т

емкостью 4096 бит со ,::;еч::,;чг уп-, , ,

равления нг микросхе-., i-iin::, i , , i

кр5б5 уь. ,„ ,,,, „;;

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1594609A1 |

| Динамическое полупроводниковое запоминающее устройство | 1987 |

|

SU1439680A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Устройство для регенерации динамической памяти со свободными зонами | 1989 |

|

SU1672529A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1374280A1 |

| Устройство для регенерации информации | 1984 |

|

SU1238151A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

жит для разре-яг 14:( ре --анератшт1 н:; вьжоде 38, слгна,:; ЧЬ Стар:г :1еГ:, на пь:скоде счетчика 13 пс ст-чки:,- ш,ие на входь :злеме1)ТС|Л И-JiK : / : 19s сигнал 47 ТРГ на сыходс три:;--ч ра 15. cnr Haj:, 43 Ввод ло : :

с:-,г ка,л -; :vi i

на э;:1емента 5/, скг - i

;е---II

, 1т

3

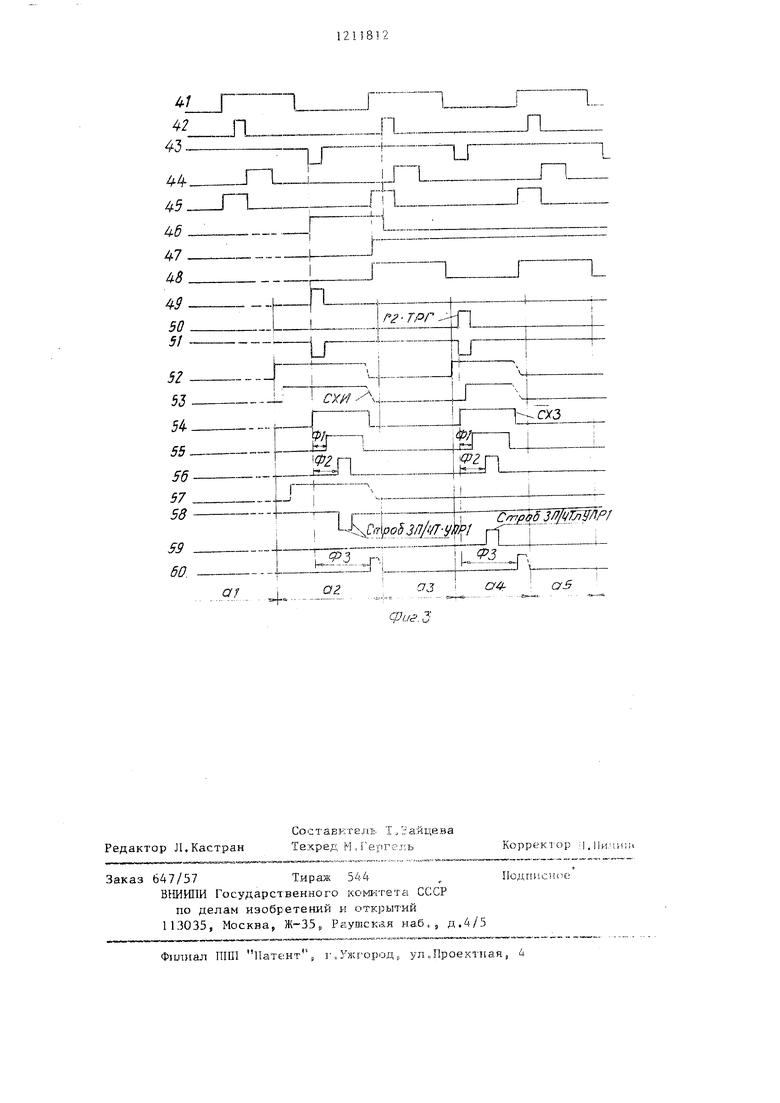

При отсутствии обращения в момент импульса 4 и включенного тригге- ра 15, т.е. при наличии сигнала 47, формируется сигнал 48 управления мутиплексором 2 для пропускания адреса регенерации, а импульс 44 через элемент ИШ-НЕ 7 и формирователь 8 формирует разрешающий сигнал СЕ н входе блока 3,

Обращение к памяти в режиме регенерации реализуется всегда за счет того, что запуск триггера 21 осущесвляется только в момент импульса 43.

Благодаря связи между выходом дешифратора 4 и входом 27 блока 5, сигнал 52 Выбор микросхемы поступает в блок 5, где происходит раздельное формирование сигнала разрешения СЕ для режима обращения к памяти сигнала 55 СЕМП и для режима регенерации СЕРГ, т.е. сигнала 44. Это позволяет реализовать операцию обращения к блоку 3 в любой момент времени независимо от операции регенерации, за счет чего сокращается время обращения к динамическому устройству.

.В вычислительных системах, где происходит согласование двух независимых синхронизации, как правило, существует пассивный отрезок времени вхождение одной синхронизации в другую, соизмеримый с периодом наибольшей частоты синхросигнала. Для обеспечения более надежного режима обращения к блоку 3 и максимальной частоты обращения к нему в период регенерации за такт до начала цикла регенерации, начинакнце- гося с началом сигнала 46 Старт.

124

per., обращение разрешается также в момент импульса 49 фиг.З). Это преимущество устройства особенно важно при применении его в вы- числительных системах типа дисплей- ных контролеров, где обращение к устройству для регенерации отображаемой информации должно быть с максимально возможной частотой с равномерным (без перерывов) периодом (не-более 1,0-;2 мкс) цикла считывания на динамический элемент памя- ти,

Формирование сигнала 51 включе-

ния триггера 21 осуществляется эле- NKHTOM И-НЕ 20. Сигнал с выхода триггера 21 поступает на входы формирователей 22, 23 и 24, где формируются сигнал 55 СЕМП (на выходе 37)и сигнал 58 Запись или чтение на выходе 40, котот ые осуществляют управление блоком 3 с частотой импульсов, генерируемых генератором 10. Длительности и периоды

следования сигналов управления (.фиг .З)формируются в соответствии с техническими условиями на применяе- №1й динамический элемент памяти.

При обращении вне периода регенерации заданный режим осуществляется без синхронизации с режимом регенерации.

Таким образом, происходит обращение к блоку 3 в любой момент времени независимо от операции регенерации. Это позволяет обеспечить минимальное время обращения к динамической памяти, определяемое только временными соотношениями при 1еняемо-.

го элемента динамической памяти.

2

31

f

-

Ijl

л.

Ж

37

.28

23

-I ,-

т

33

.ue. /

Редактор Л.Кастран

Составитель I,гакцева Техред М,Гергель

Заказ 647/37Тираж 544

ВНИИШ Государственного ком1-гт-ата СССР

по делам изобретений и отк1зытий 113035, Москва, Ж-35 ,, Раушская наб „, д. 4/5

Ф5шпал mill Пат€:нт % г,Ужгород, ул „Проектная, 6

иё.:5

Корректор М.Пилит

Подписное

| Оперативное запоминающее устройство на динамических элементах памяти | 1981 |

|

SU982089A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-01—Подача