Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на полупроводниковых микросхемах памяти динамического типа.

Целью изобретения является повышение быстродействия устройства за счет сокращения времени, затраченного на регенерацию памяти.

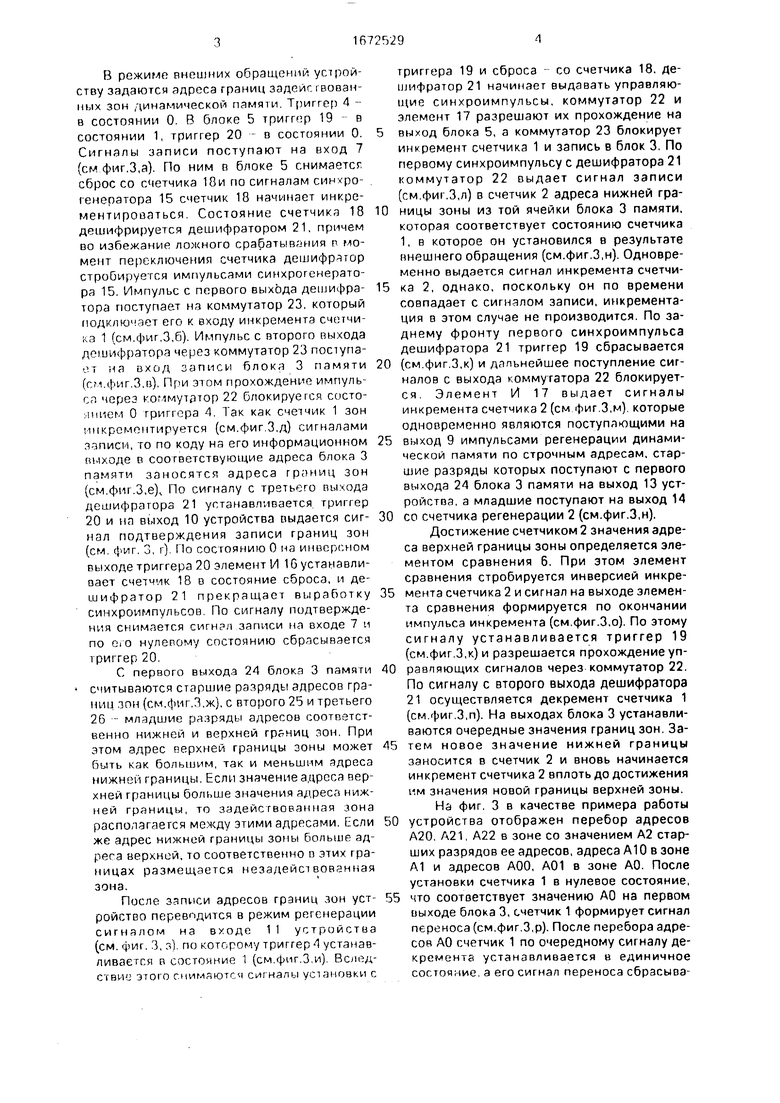

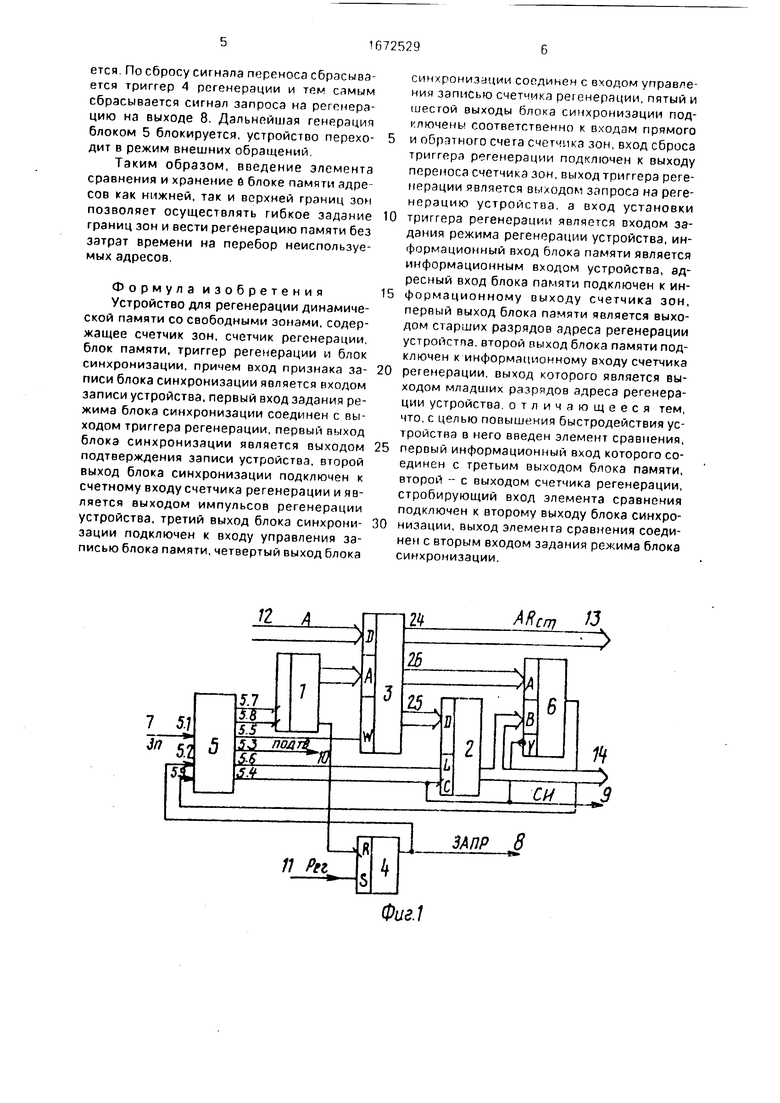

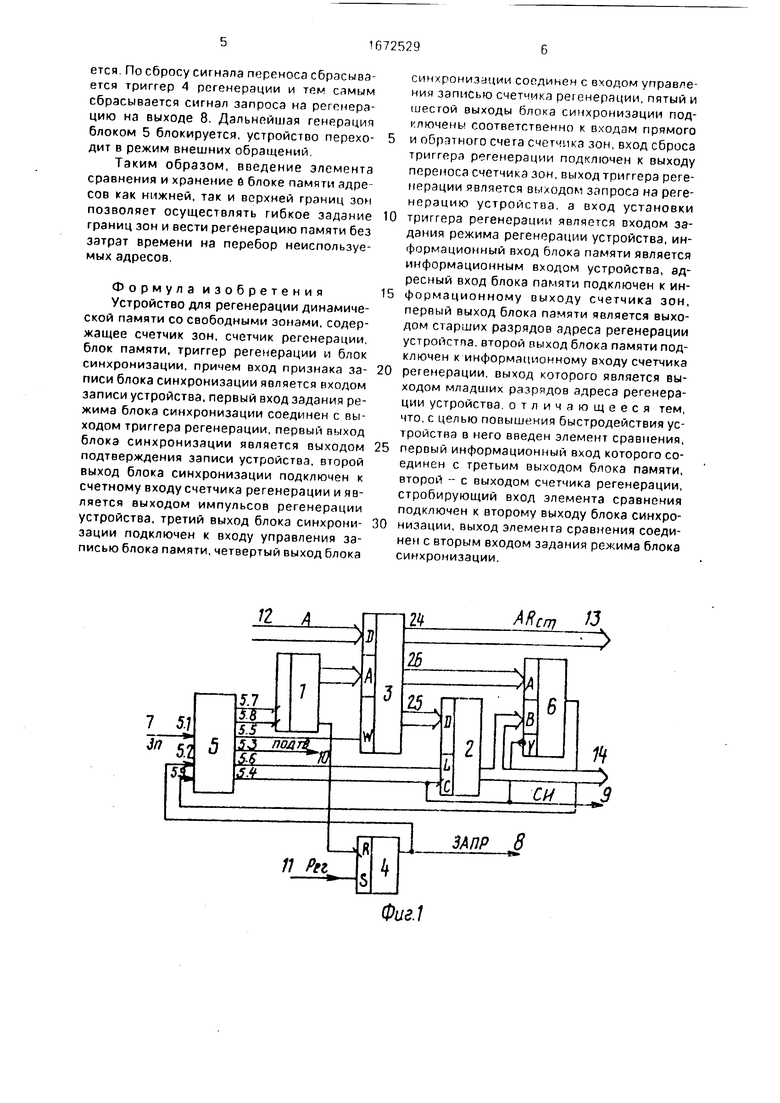

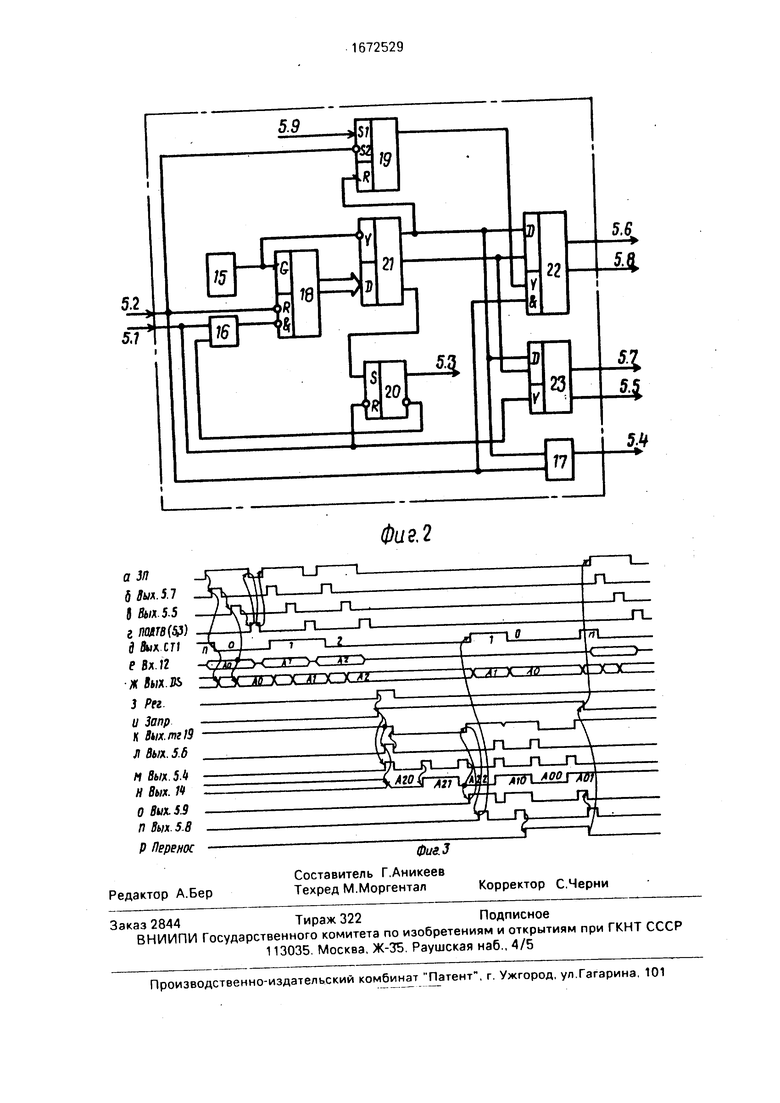

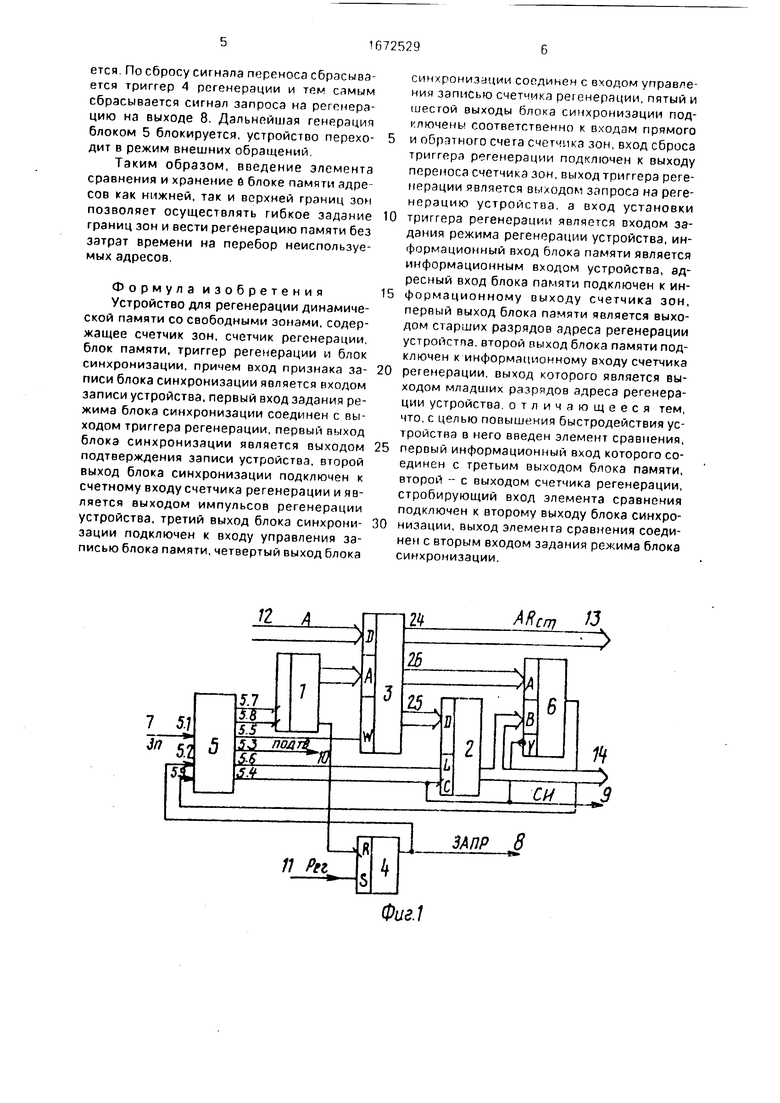

На фиг. 1 показана функциональная схема предлагаемого устройства; на фиг. 2 дана реализация блока синхронизации; на фиг. 3 представлены временные диаграммы работы устройства.

Устройство содержит счетчик зон 1, счетчик регенерации 2, блок памяти 3, триггер регенерации 4, блок синхронизации 5, элемент сравнения 6, вход 7 записи, выход 8 запроса на регенерацию, выход 9 импульсов регенерации, выход 10 подтверждения записи, вход 11 задания режима регенерации, информационный вход 12, выход 13 старших разрядов адреса регенерации, выход 14 младших разрядов адреса регенерации.

Блок синхронизации 5 содержит (см.фиг.2) синхрогенератор 15, элементы И 16 и 17, счетчик 18, триггеры 19 и 20, дешифратор 21, коммутаторы 22 и 23. Устройство содержит входы / выходы 24-26.

Устройство работает в двух режимах; внешнего обращения и регенерации.

о VI ю ел го о

В режиме внешних обращений устройству задаются адреса границ задейг. гвован- ных зон динамической памяти. Триггер 4 - в состоянии 0. В блоке 5 триггер 19 - в состоянии 1, триггер 20 - в состоянии 0. Сигналы записи поступают на вход 7 (см фиг.З.а). По ним в блоке 5 снимается сброс со счетчика 18и по сигналам cunvpo- генератора 15 счетчик 18 начинает инкре- ментирооаться. Состояние счетчика 18 дешифрируется дешифратором 21, причем во избежание ложного срабатывания в момент переключения счетчика дешифратор стробируется импульсами синхрогенерато- ра 15. Импульс с первого выхода дешифратора поступаем на коммутатор 23, который подклюияет его к входу инкремента счетчика 1 (см.фиг.3,6). Импульс с второго выхода дешифратора через коммутатор 23 поступает на вход записи f3 л о к я 3 памяти (см.фиг.3,и). При этом прохождение импульса через коммутатор 22 блокируется состо- чичем 0 триггера А. Так как счетчик 1 зон пнкрсмонтируется (см.фиг 3,д) сигналами записи, то по коду на его информационном выходе в соответствующие адреса блока 3 памяти заносятся адреса границ зон (см.фиг.3,е), По сигналу с третьего выхода дешифратора 21 устанавливается трипер 20 и на выход 10 устройства выдается сигнал подтверждения записи границ зон (см. фиг. G, г) По состоянию 0 на инверсном выходе триггера 20 элемент И 16 устанавливает счетчик 18 в состояние сброса, и дешифратор 21 прекращает выработку синхроимпульсов По сигналу подтверждения снимается сигнал записи на входе 1 и по eio нулевому состоянию сбрасывается т риггер 20.

С первого выхода 24 блока 3 памяти считываются старшие разряды адресов границ зон (см.фиг,3,ж), с второго 25 и третьего 26 - младшие разряды адресов соответственно нижней и верхней границ зон. При этом адрес верхней границы зоны может быть как большим, так и меньшим адреса нижней границы.Если значение адреса верхней границы больше значения адреса нижней границы, то задействованная зона располагается между этими адресами, Если же адрес нижней границы зоны больше адреса верхней, то соответственно в этих границах размещается незадействованная зона.

После записи адресов границ зон устройство переводится в режим регенерации сигналом на входе 1 1 устройства (см. фиг. 3, з) по которому триггер 4 устанавливается в состояние 1 (см.фиг.3,и) Вследствие эго1 о снимаются сигналы установки с

триггера 19 и сброса - со счетчика 18. дешифратор 21 начинает выдавать управляющие синхроимпульсы, коммутатор 22 и элемент 17 разрешают их прохождение на

выход блока 5, а коммутатор 23 блокирует инкремент счетчика 1 и запись в блок 3, По первому синхроимпульсу с дешифратора 21 коммутатор 22 выдает сигнал записи (см.фиг.3,л) в счетчик 2 адреса нижней гра0 ницы зоны из той ячейки блока 3 памяти, которая соответствует состоянию счетчика 1, в которое он установился в результате внешнего обращения (см.фиг.З.н). Одновременно выдается сигнал инкремента счетчи5 ка 2, однако, поскольку он по времени совпадает с сигналом записи, инкремента- ция в этом случае не производится. По заднему фронту первого синхроимпульса дешифратора 21 триггер 19 сбрасывается

0 (см.фиг.3,к) и дальнейшее поступление сигналов с выхода коммутатора 22 блокируется. Элемент И 17 выдает сигналы инкремента счетчика 2 (см фиг.З.м) которые одновременно являются поступающими на

5 выход 9 импульсами регенерации динамической памяти по строчным адресам, старшие разряды которых поступают с первого выхода 24 блока 3 памяти на выход 13 устройства, а младшие поступают на выход 14

0 со счетчика регенерации 2 (см.фиг.З.н).

Достижение счетчиком 2 значения адреса верхней границы зоны определяется элементом сравнения 6. При этом элемент сравнения стробируется инверсией инкре5 мента счетчика 2 и сигнал на выходе элемента сравнения формируется по окончании импульса инкремента (см.фиг.3,о). По этому сигналу устанавливается триггер 19 (см.фиг.3,к) и разрешается прохождение уп0 равняющих сигналов через коммутатор 22. По сигналу с второго выхода дешифратора 21 осуществляется декремент счетчика 1 (см.фиг.З.п). На выходах блока 3 устанавливаются очередные значения границ зон. За5 тем новое значение нижней границы

заносится в счетчик 2 и вновь начинается

инкремент счетчика 2 вплоть до достижения

им значения новой границы верхней зоны.

На фиг. 3 в качестве примера работы

0 устройства отображен перебор адресов А20, А21, А22 в зоне со значением А2 старших разрядов ее адресов, адреса А10 в зоне А1 и адресов AGO, A01 в зоне АО. После установки счетчика 1 в нулевое состояние,

5 что соответствует значению АО на первом выходе блока 3, счетчик 1 формирует сигнал переноса (см.фиг.З.р). После перебора адресов АО счетчик 1 по очередному сигналу декремента устанавливается в единичное состояние, а его сигнал переноса сбрасывэется. По сбросу сигнала переноса сбрасывается триггер 4 регенерации и тем самым сбрасывается сигнал запроса на регенерацию на выходе 8. Дальнейшая генерация блоком 5 блокируется, устройство перехо- дит в режим внешних обращений.

Таким образом, введение элемента сравнения и хранение в блоке памяти адресов как нижней, так и верхней границ зон позволяет осуществлять гибкое задание границ зон и вести регенерацию памяти без затрат времени на перебор неиспользуемых адресов.

Ф о р м у л а и з о б р е т е н и я

Устройство для регенерации динамической памяти со свободными зонами, содержащее счетчик зон, счетчик регенерации. блок памяти, триггер регенерации и блок синхронизации, причем вход признака за- писи блока синхронизации является входом записи устройства, первый вход задания режима блока синхронизации соединен с выходом триггера регенерации, первый выход блока синхронизации является выходом подтверждения записи устройства, второй выход блока синхронизации подключен к счетному входу счетчика регенерации и является выходом импульсов регенерации устройства, третий выход блока синхрони- зации подключен к входу управления записью блока памяти, четвертый выход блока

синхронизации соединен с входом управления записью счетчика регенерации, пятый и шестой выходы блока синхронизации подключены соответственно к входам прямого и обратного счета счетчика зон, вход сброса триггера регенерации подключен к выходу переноса счетчика зон, выход триггера регенерации является выходом запроса на регенерацию устройства, з вход установки триггера регенерации является входом задания режима регенерации устройства, информационный вход блока памяти является информационным входом устройства, адресный вход блока памяти подключен к информационному выходу счетчика зон, первый выход блока памяти является выходом старших разрядов адреса регенерации устройстпа. второй выход блока памяти подключен к информационному входу счетчика регенерации, выход которого является выходом младших разрядов адреса регенерации устройства, отличающееся тем, что, с целью повышения быстродействия устройства в него введен элемент сравнения, первый информационный вход которого соединен с третьим выходом блока памяти, второй -- с выходом счетчика регенерации, стробирующий вход элемента сравнения подключен к второму выходу блока синхронизации, выход элемента сравнения соединен с вторым входом задания режима блока синхронизации.

Фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Блок буферной памяти для терминального устройства | 1989 |

|

SU1633454A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для вывода отображаемой информации | 1986 |

|

SU1322252A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1615782A1 |

Изобретение относится к вычислительной технике и может быть использовано при положении запоминающих устройств на полупроводниковых микросхемах динамического типа. Целью изобретения является повышение быстродействия устройства за счет сокращения времени, затрачиваемого на регенерацию памяти. Устройство для регенерации содержит счетчик зон 1, счетчик регенерации 2, блок памяти 3, триггер регенерации 4, блок синхронизации 5, элемент сравнения 6, вход 7 записи, выход 8 запроса на регенерацию, выход 9 импульсов регенерации, выход 10 подтверждения записи, вход 11 задания режима регенерации, информационный вход 12, выход 13 старших разрядов адреса регенерации, выход 14 младших разрядов адреса регенерации. Введение элемента сравнения и хранение в блоке памяти адресов как нижней, так и верхней границ зон позволяет осуществлять гибкое задание границ зон и вести регенерацию памяти без затрат времени на перебор неиспользуемых адресов. 3 ил.

а ЗП 6 Дых. 5.7 0 Вып. 5.5

г mmftJ)

dflwxcn Р Вд.12 Ж 0ЫХ.Л& 3 /to.

U J0/V К Вчх.

Л Зш. 5.6

И 8ых.5Л Н Вых.

О Вил 5.9 П Вых. 5.8

Р Перенос едактор А.Бер

Фиг.З

Составитель Г.Аникеев Техред М.Моргентал

Фиг.З

Корректор С.Черни

| Устройство для управления регенерацией оперативного накопителя | 1984 |

|

SU1198474A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-08-23—Публикация

1989-09-04—Подача