.(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ДИНАМИЧЕСКИХ ЭЛЕМЕНТАХ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| Запоминающее устройство | 1989 |

|

SU1718272A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство управления полупроводниковой памятью | 1986 |

|

SU1410098A1 |

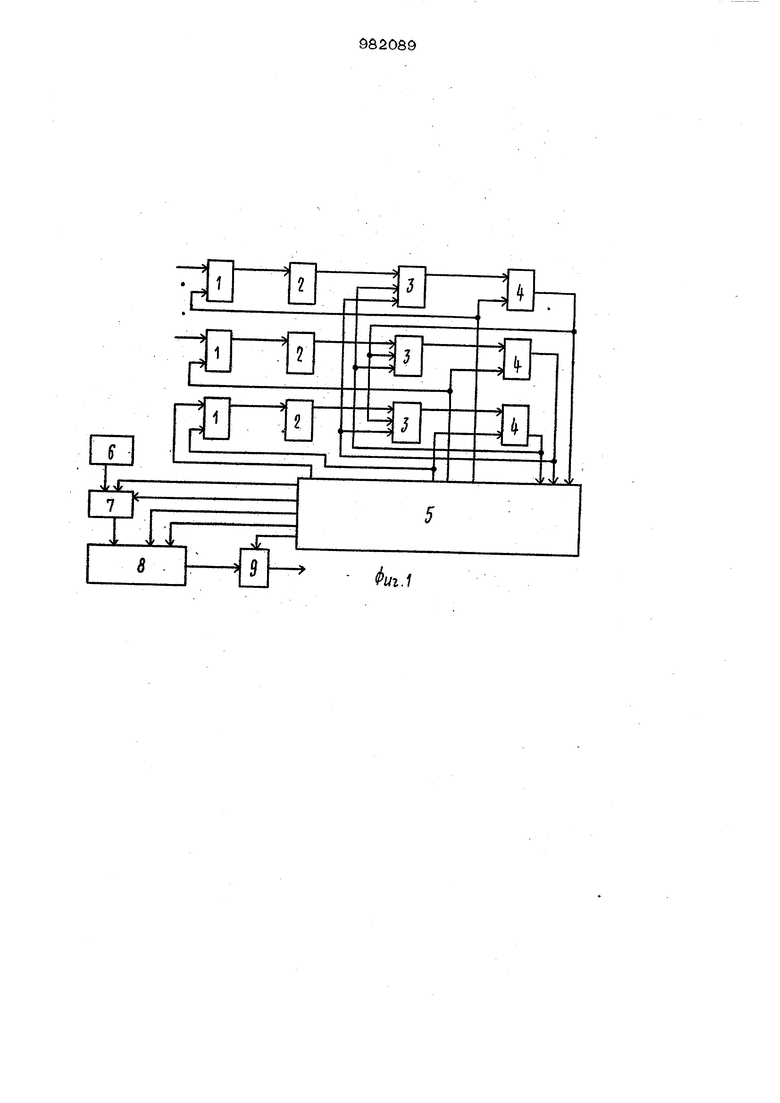

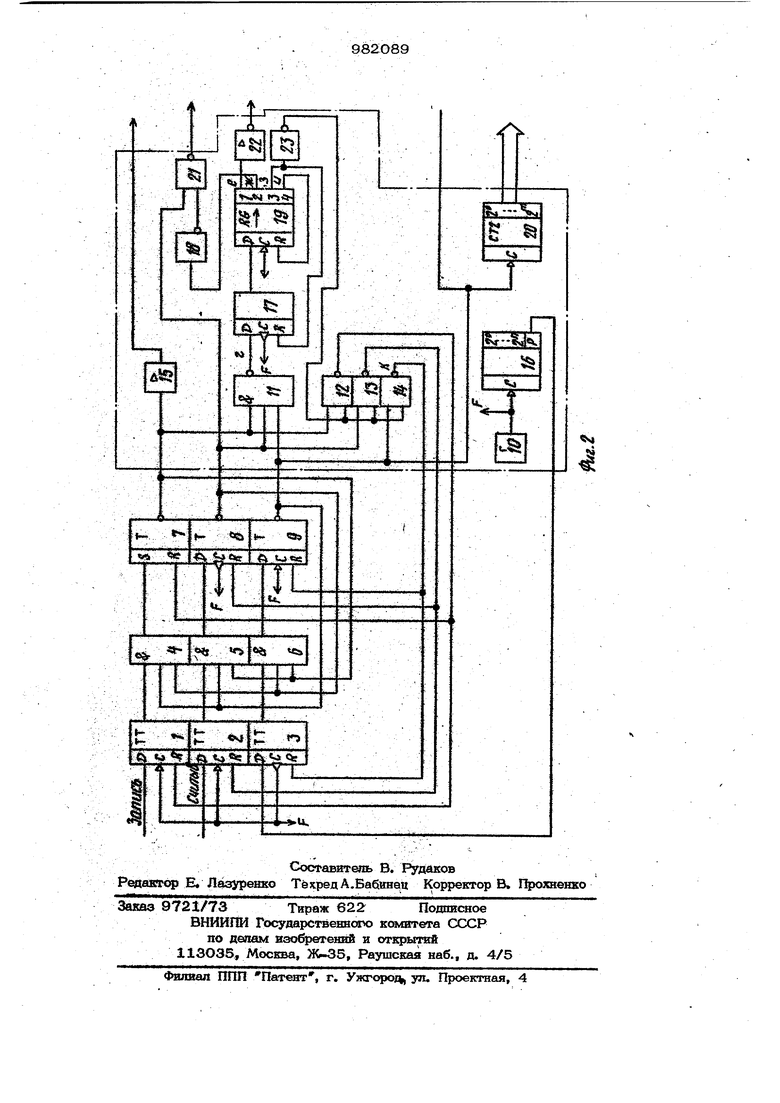

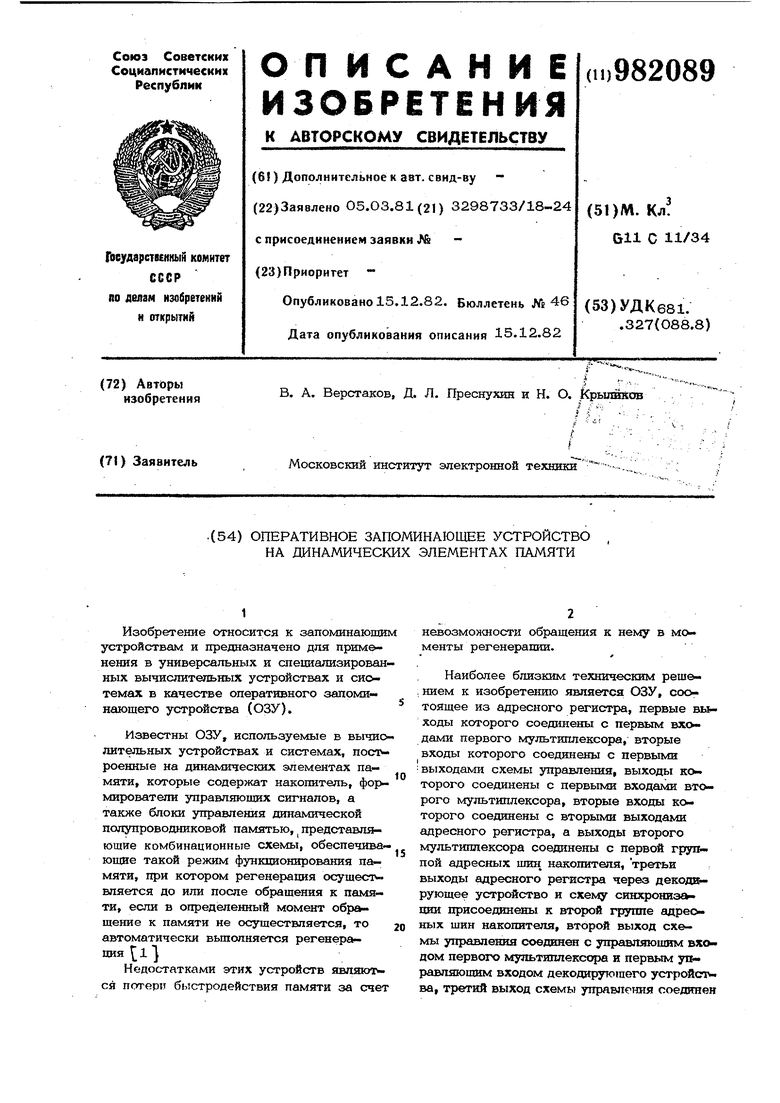

Изобретение относится к запоминающи устройствам и предназначено для применения в универсальных и специализирован ных вычислительных устройствах и сиотемах в качестве оперативного запоминающего устройства (ОЗУ). Известны ОЗУ, используемые в вычис лительных устройствах и системах, построенные на динамических элементах памяти, которые содержат накопитель, формирователи управляющих сигналов, а также блоки управления динамической полупроводниковой памятью,. представляющие комбинационные схемы, обеспечивающие такой режим функционирования памяти, при котором регенерация осушест вляется до или после обращения к памяти, если в определенный момент обращение к памяти не осуществляется, то автоматически выполняется регенерация 1 Недостатками этих устройств являют ся потери б1)стродействия памяти за счет невозмояотости обращения к нему в моменты регенерации. I- Наиболее близким техническим реще. нием к изобретению является ОЗУ, состоящее из адресного регистра, первые выходы которого соединены с первым входами первого мультиплексора, вторые входы которого соединены с первыми : выходами схемы управления, выходы которого соединены с первыми входами второго мультиплексора, вторые входы которого соединены с вторыми выходами адресного регистра, а выходы второго мультиплексора соединены с первой группой адресных щин, накопителя, третьи выходы адресного регистра через декодер рующее устройство и схему синхронизм1ШИ присоединены к второй группе адрео ных щин накопителя, второй выход схемы управления соединен с управляющим вхо дом первого мультиплексора и первым управляющим входом декодирующего устройсл ва, третий выход схемы управл ния соещтнен с вторым управляющим входом декодирующего устройства, четвертый и пятый выходы схемы управления через схему С1шхронизации соединены с управляющи , ми входами накопителя, выход которого через усилитель считывания подключен к входу регистра считывания, управляющий вход которого соединен с шестым выходом схемы управления. В случаях, когда это запоминающее устройство регенерирует собственное содержимое, при поступлении запроса на обращение в подходящий момент в течение процесса регенерации, осуществляется прерывание этого процесса, и обращение реализуется. В моменты,когда прерывание процесса регенерации невозможно выдается сигнал Занято, обращение не реализуется, и процесс регенерации продолжается . Недостатками этого ОЗУ являются потеря быстродействия за счет невозможности обращения к памяти в определенны моменты времени, когда прерывание процесса регенерации памяти невозможно, а таюке необходимость повторного обращения к памяти в этом случае. Цель изобретения - повыщение быстро действия ОЗУ на динамических элементах памяти, которое при обращении к нему запоминало бы заявки на запись, считывание, регенерацию до их выполнения по очереди в порядке поступления. Поставленная, цель достигается тем, что в оперативное запоминающее устройство lia динамических элементах памяти, содержащее регистр адреса, выход котор го соединен с первым информационцым входом мультиплексора, второй информац онный вход которого соединен с первым выходом блока управления, управляющий вход- с вторым выходом блока управления, а выход подключен к адресному ВХОДУ накопителя, первый и второй управ лающие входы соединены соотве етвенно с третьим н четвертым выходами блока управления, а информационный выход подключен к входу регистра данных, выход которого является выходом уст ройсугва, а управляющий вход соединен с пятым выходом блока управления, вве;дены три группы последовательно соеданеяных первого триггера, элемента задержки элемента И и второго триггера, при чем выход второго триггера первой группы подключен к первому входу блока управпения и первым входам элементов И второй и третьей грутт, выход второго тршгтера второй группы соединен с втоым входом блока управления, первым входом элемента И первой группы и вторьпуг входом элемента И третьей группы, выход второго триггера третьей группы подключен к третьему входу блока упра&ления и вторым входам элементов И первой и второй групп, управляпощие входы триггеров одноименных групп объединены и подключены соответственно к щестому, седьмому и восьмому выходам блока управления, девятый выход которого соединен с информационным входом одного из триггеров первой группы, информационные входы первых триггеров других групп являются входами устройства. На фиг. 1 изображена структурная схема ОЗУ на динамических элементах памяти; на. фиг. 2 - часть схемы на фиг. 1 (раскрыта структура блока управления). Устройство содержит три группы пооледовательно соединенных первого триггера 1, элемента 2 задержки, элемента И 3, И второго триггера 4, блок 5 управления, регистр 6 адреса, мультиплексор 7, накопитель 8 и регистр 9 данных. Блок 5 управления (на фиг. 2 выделен пунктирной линией) содержит генератор 10 тактовых импульсов, элемент И-НЕ 11, элементы ИЛИ-НЕ 12-14, усили.тель 15 сигналов, делитель 16 частоты, триггер 17, элемент ИЛИ-НЕ 18, сдвигающий регистр 19, счетчик 20 адреса регенерации, элемент ИЛИ-НЕ 21, усилитель 22 сигналов, элемент ИЛИ-НВ 23. Устройство работает следующим образом. Команды выбора режима, поступающие на входы ОЗУ, устанавливают триггеры 1, служащие для хранения команд выбора режима, в единичное состояние. Перезапись команд из триггеров 1 в соответствующие трИггерь 4, служащие для управления, осуществляется через элементы 2 задержки и элементы И 3. Единичное состо5шие одного из трш%геров 4 вызывает реализацию соответст вующего режима ОЗУ. Элемент И 3 обеспечивает передачу комавды из триггера 1 в соответствующий триггер 4 при условии, что два других триггера 1 находятся в нулевом состоянии, в противном случае вьшолнешге команды, запомненной в триггере 1, задерживается до обнуления триггера 4, происходящего по команде из блока 5 упра&ления по окончании вьшолнения соответ ствуюшего режима. Сброс триггеров 1 происходит по этим же командам из блока 5 управления. Если два или три триггера 1 переюио чены в единичное состояние одновременн ТО очередность передачи команд тршгг&ра 4 и, следовательно, их вьшопнение осуществляется разными длительностями задержек в элементах 2 задержки. Благодаря введению новых элементов и связей оперативное запоминающее jcr- ройство на динамических элементах памяти имеет возможность автоматически поддерживать очередь загюок на запись, считывание, регенерацию с минимизацией времени перехода от реализации одной заявки к реализации другой, что позволя повысить быстродействие устройства и, кроме того, упростить процедуру обращ& иия к памяти центрального процессора. Технико-экономический эффект от внедрения предлагаемого устройства гфоявляе ся за счет повышения быстродействия ОЗУ и выражается в экономии 4% машинного времени. Формула изобретения Оперативное запоминающее устройство на динамиче ских элементах памяти, содержащее регистр адреса, выход которого соединен с первым информациоювым входом мультиплексора, второй информада онный вход которого соединен с первым выходом блока управления, управляющий вход - с вторым выходом блока управления, а выход подключен к адресному входу накопителя, первый и второй упра& Л5пощие входы которого соединены соот ветственно с третьим и четвертым выходЁЦ ш блока управления, а информапионный выход псокшочен к входу регистра данных, выход которого является выходом устройства, а управляюпшй вход соединен с пятым выходом блока управления, отличающе вся тем, что, с целью повышения быстродействия устройства, в него три группы поо{ледовательно соедин шых первого т{шпгера, элемента задержки, И а второго триггера, причем выход iaTopoго триггера первой группы подшпочвн к первому входу блока угфавленяя и пер- . вым входам элементов И второй и третьей групп, выход второго триггера второй Г1ЩШЫ соединен о Brofita.t входом блока управления, первым входсш элемента И первой группы и вторым входом элемента И третьей грушш, выход вто рог о тригг третьей грушш подкпижен к третьему входу управления я вторым входам эл лентов И первой к второй групп, управшооншв входа трш геров одноименных Tfyan об1 единены и подключены соответственно к шестому, и восьмому выходам бпока управлшшя, девятый выход когоремгч соединен с информапиешшм вжэдом одного из триггеров перво& группы, информацв онные ъкоцы первых триггеров других групп являются вхопами устройИсточники ияформахош, принятые во внимание щж экспертизе 1. Заявка Япон № S4-5939, кл. 97(7) С 19, опубляк. 1979. 2i Заявка Японии № 54-5659, «л. 97(7) С 19, опублик. 1979 (прототип).

Авторы

Даты

1982-12-15—Публикация

1981-03-05—Подача