второго конденсатора и четвертой шине управления, другой вывод второго конденсатора соединен с истоком четвертого установочного, со стоком пятого коммутирующего и с затвором второго компенсирующего транзисторов , исток пятого коммутирующего транзистора подключен к стоку третьеI

Изобретение относится к вычислительной технике и может быть использовано в больших интегральных схемах запоминающих устройств.

Цель изобретения - повышение быстродействия дешифратора для ЗУ с резервированием.

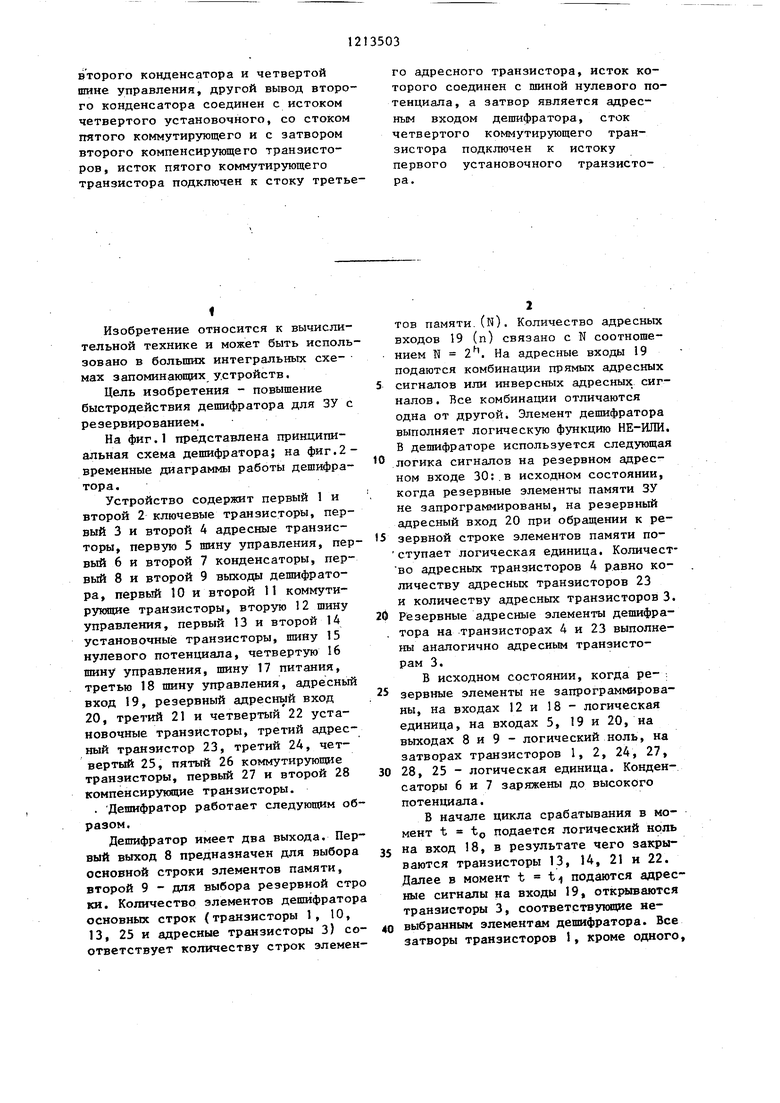

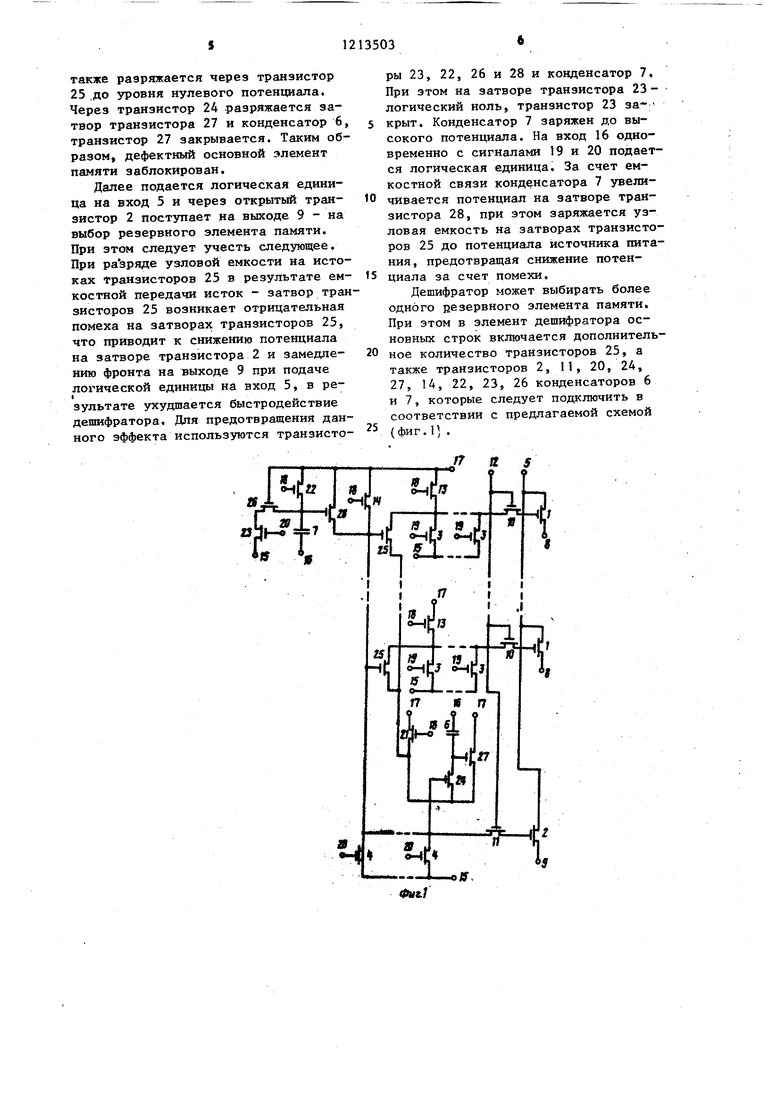

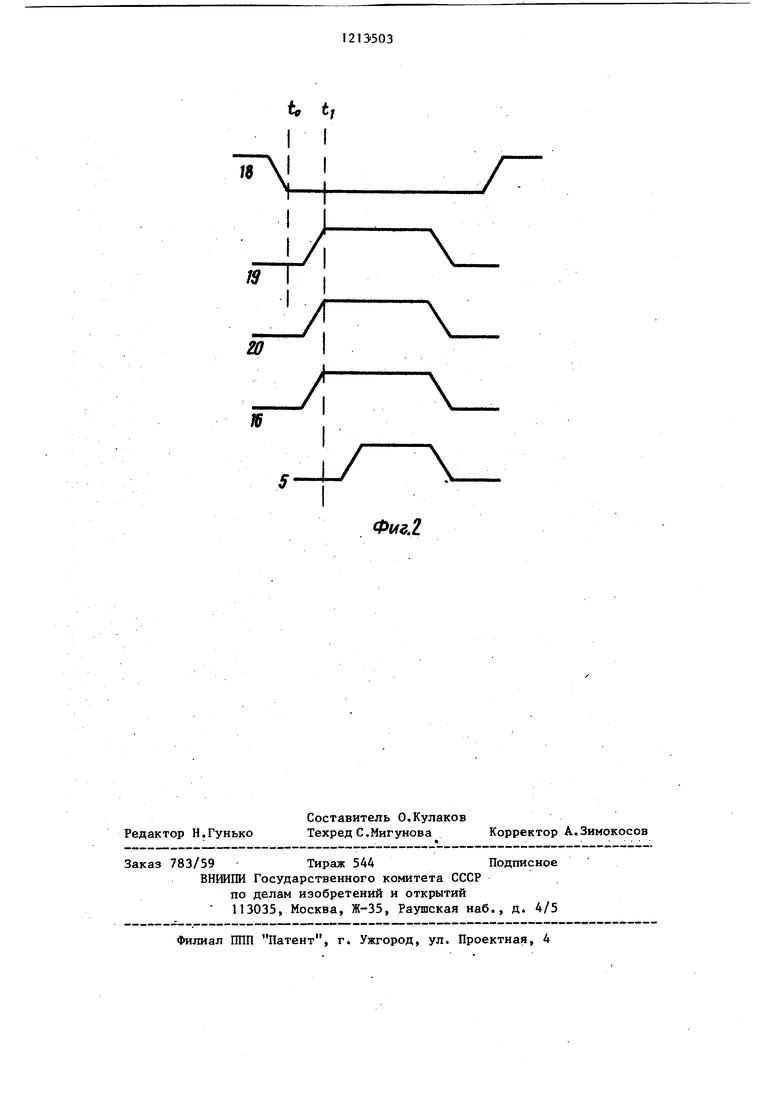

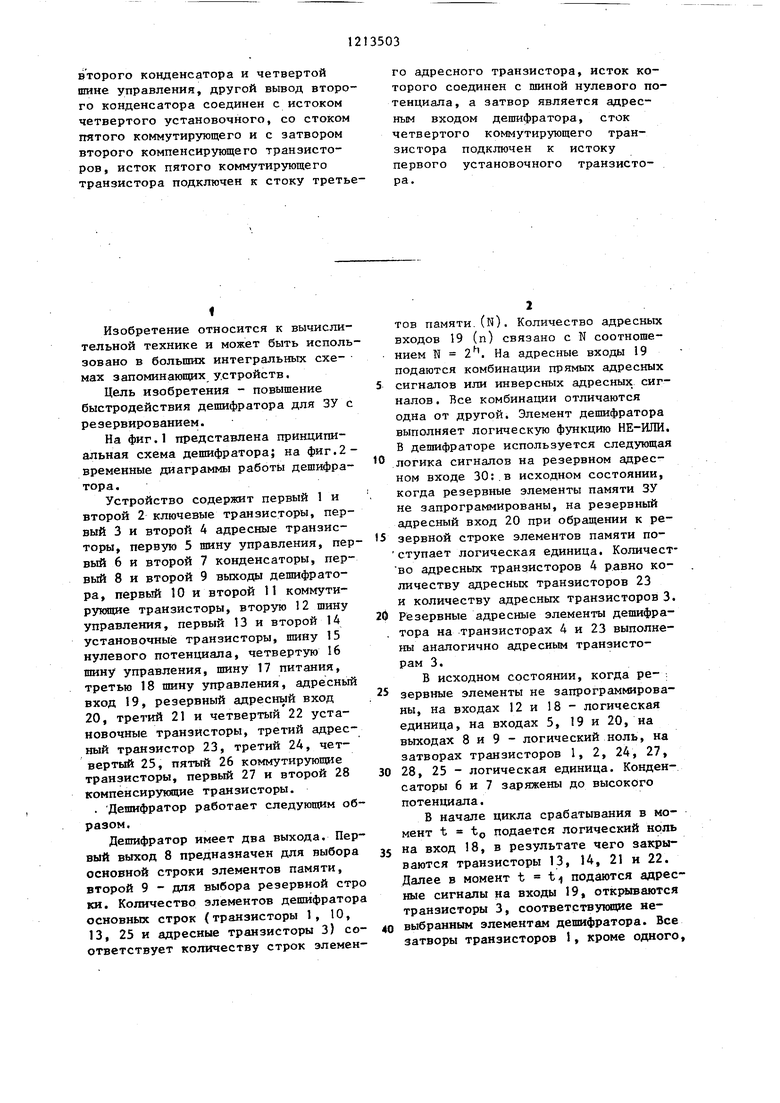

На фиг.1 представлена принципиальная схема дешифратора; на фиг.2- временные диаграммы работы дешифратора.

Устройство содержит первый 1 и второй 2 ключевые транзисторы, первый 3 и второй 4 адресные транзисторы, первую 5 шину управления, первый 6 и второй 7 конденсаторы, первый 8 и второй 9 выходы дешифратора, первый 10 и второй 11 коммутирующие транзисторы, вторую 12 шину управления, первый 13 и второй 14 установочные транзисторы, шийу 15 нулевого потенциала, четвертую 16 шину управления, шину 17 питания, третью 18 шину управления, адресный вход 19, резервный адреснь1й вход 20, третий 21 и четвертый 22 установочные транзисторы, третий адресный транзистор 23, третий 24, четвертый 25, пятый 26 коммутирующие транзисторы, первый 27 и второй 28 компенсируюпще транзисторы.

. Дешифратор работает следующим образом.

Дешифратор имеет два выхода. Первый выход 8 предназначен для выбора основной строки элементов памяти, второй 9 - для выбора резервной стро ки. Количество элементов дешифратора основных строк (транзисторы 1, 10, 13, 25 и адресные транзисторы 3) соответствует количеству строк элеменго адресного транзистора, исток которого соединен с шиной нулевого потенциала, а затвор является адресным входом дешифратора, сток четвертого коммутирующего транзистора подключен к истоку первого установочного транзистора.

тон памяти.(N). Количество адресных входов 19 (п) связано с N соотношением и 2. На адресные входы 19 подаются комбинации прямых адресных

сигналов или инверсных адресных сигналов . Все комбинации отличаются одна от другой. Элемент дешифратора выполняет логическую функцию НЕ-ИЖ. В дешифраторе используется следующая логика сигналов на резервном адресном входе 30;.в исходном состоянии, когда резервные элементы памяти ЗУ не запрограммированы, на резервный адресный вход 20 при обращении к резервной строке элементов памяти по- ступает логическая единица. Количест- во адресных транзисторов 4 равно количеству адресных транзисторов 23 и количеству адресных транзисторов 3.

Резервные адресные элементы дешифра- тора на транзисторах 4 и 23 выполнены аналогично адресным транзисторам 3.

В исходном состоянии, когда ре- .

зервные элементы не запрограммированы, на входах 12 и 18 - логическая единица, на входах 5, 19 и 20, на выходах 8 и 9 - логический ноль, на затворах транзисторов 1, 2, 24, 27,

28, 25 - логическая единица. Конденсаторы 6 и 7 заряжены до высокого потенциала.

В начале цикла срабатывания в момент t tg подается логический ноль

на вход 18, в результате чего закрываются транзисторы 13, 14, 21 и 22. Далее в момент t t подаются адресные сигналы на входы 19, открываются транзисторы 3, соответствующие невыбранным элементам дешифратора. Все затворы транзисторов I, кроме одного.

3

разряжаются через транзисторы 10 и до уровня нулевого потенциала. Однвременно с сигналом 19 подается логическая единица на резервный адреный вход 20, затвор транзистора 2 разряжается через транзисторы 11 и до нулевого потенциала, затворы трзисторов 24 и 25 - через транзисто 4, затвор транзистора 28 - через транзисторы 26 и 23 до уровня нулевого потенциала. После этого подаеся логическая единица на вход 5 и через единственный открытый транзистор 1 заряжается выбранная выходная шина 8 до высокого потенциала.

Для нормальной работы дешифратора необходимо, чтобы на истоках транзисторов 21 и 25 оставался высокий потенциал при подаче резервн адресных сигналов 20, т.е. уменьшение потенциала на затворах транзисторов 25 через транзистор 4 должно происходить быстрее, чем на истока транзисторов 13 через транзисторы 3. В противном случае, откроются транзисторы 25 и разрядят узловую емкость на истоке транзистора 21, что приведет к снижению потенциала выбранного элемента дешифратора на истоке транзистора 13 и к нарушени нормальной работы дешифратора. Выполнить данное условие достаточно тяжело, так как в ЗУ узловые емкости истоков транзисторов 13 разряжаются большим количеством транзисторов 3, а емкости большого числа затворов транзисторов 25 разряжаются в общем случае всего одним транзистором 4. Дополнительное ускорение разряда узловой емкости истока транзистора 21 вызывается влиянием суммарной емкостной связи затвор - исток транзисторов 25. Кроме того, значительный разброс в БИЧ таких параметров, как пороговое напряже

ние, крутизна транзисторов и велч- чина емкостей не дает возможности гарантировать отсутствие паразитного разряда выбранного элемента дешифратора Наличие внутренних помех по армле, питанию и подложке еще более осложняет ситуацию. Для предотвращения такого паразитного разряда используются транзисторы 24 и 27 и конденсатор 6, Одновременно с сигналами 19 р 20 подается логическая единица на вход 16, В этот

момент потенциал на затворе транзистора 24 не вьш1е, чем на его истоке и транзистор 24 закрыт, В результате емкостной связи конденсатора 6 потенциал на затворе транзистора 27 превьшает потенциал напряжения питания плюс пороговое напряжение транзистора 27, в результате чего транзистор 27 открыт и заряжает узловую емкость на истоке транзистора 21 до напряжения источника 17 питания, препятствуя паразитному снижению потенциала на истоке транзистора 21 через открытй транзистор 25. После этого подается логическая единица на вход 5 и через единственный открытый транзистор 1 заряжается выбранная выходная шина 8 до высокого потенциала. На входе 12 поддерживается постоянный высокий потенциал. При программировании резервных элементов памяти изменяется логика резервных адресных сигналов 20, При совпадании адреса на входе ЗУ с адресом дефектного элемента памяти на всех входах 20 - логический Иоль, при несовпадении (хотя бы на одном входе 20) - логическая единица. Когда на входе 20 - логическая единица, дешифратор работает аналогично случаю незапрограммированного ЗУ,

Рассмотрим случай, когда в запрограммированном ЗУ адреса на входе ЗУ совпадают с запрограммированньм

адресом, на всех входах 20 - логический ноль, В начале цикла срабатывания на входах 18, 12 - логическая единица, на входах 5, 16, 19, 20 -. логический ноль, на затворах транзисторов 1, 2, 24, 27, 28, 25 - логическая единица. Конденсаторы 6 и 7 заряжены до высокого потенциала, . На вход 18 подается логический ноль, закрываются транзисторы 13, 14, 21

и 22, подаются адресные сигналы на входы 19, открываются транзисторы 3, соответствукицие невыбраниым элементам дешифратора. See затворы транзисторов 1, кроме одного, разряжаются через транзисторы 10 и 3 до уровня нулевого потенциала. Так как на входе 20 - логический ноль, на затворах транзисторов 25 остается высокий логический уровень, узловая емкость на истоках транзисторов 25 разряжается через транзисторы 24 и 3 до уровня нулевого потенциала и единственный выбранный элемент дешифратора

также разряжается через транзистор 25 .до уровня нулевого потенциала. Через транзистор 24 разряжается затвор транзистора 27 и конденсатор 6 транзистор 27 закрывается. Таким образом, дефектный основной элемент памяти заблокирован.

Далее подается логическая единица на вход 5 и через открытый транзистор 2 постзшает тяа выходе 9 - на выбор резервного элемента памяти. При этом следует учесть следующее. При ра зряде узловой емкости на истоках транзисторов 25 в результате емкостной передачи исток - затвор транзисторов 25 возникает отрицательная помеха на затворах транзисторов 25, что приводит к снижению потенциала на затворе транзистора 2 и замедлению фронта на выходе 9 при подаче логической единицы на вход 5, в результате ухудшается быстродействие дешифратора. Для предотвращения данного эффекта используются транзисто0

5

ры 23, 22, 26 и 28 и конденсатор 7. При этом на затворе транзистора 23 - логический ноль, транзистор 23 за- крыт. Конденсатор 7 заряжен до высокого потенциала. На вход 16 одновременно с сигналами 19 и 20 подается логическая единица. За счет емкостной связи конденсатора 7 увеличивается потенциал на затворе транзистора 28, при этом заряжается узловая емкость на затворах транзисторов 25 до потенциала источника питания, предотвращая снижение потенциала эа счет помехи.

Дешифратор может выбирать более одного иезервного элемента памяти. При этом в элемент дешифратора основных строк включается дополнительо ное количество транзисторов 25, а также транзисторов 2, 11, 20, 24, 27, 14, 22, 23, 26 конденсаторов 6 и 7, которые следует подключить в соответствии с предлагаемой схемой (фиг.) .

17 в Л

ij

I 1

/a vl I

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор для запоминающего устройства с резервированием | 1986 |

|

SU1429166A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

19

Редактор Н.Гунько

Составитель О.Кулаков Техред С.Мигунова

783/59Тираж 544Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Фмг.1

Корректор А.Зимокосов

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Электроника | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Механический грохот | 1922 |

|

SU41A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-04—Подача