1

Изобретение относится к вычислительной технике, а более конкретно цифровым запоминающим устройствам, предназначенным для использования в универсальных, специализированных счетных управляющих ЭВМ, в системах сбора и обработки информации, в различных системах контроля, управлени и т.д.

Цель изобретения - упрощение устройства.

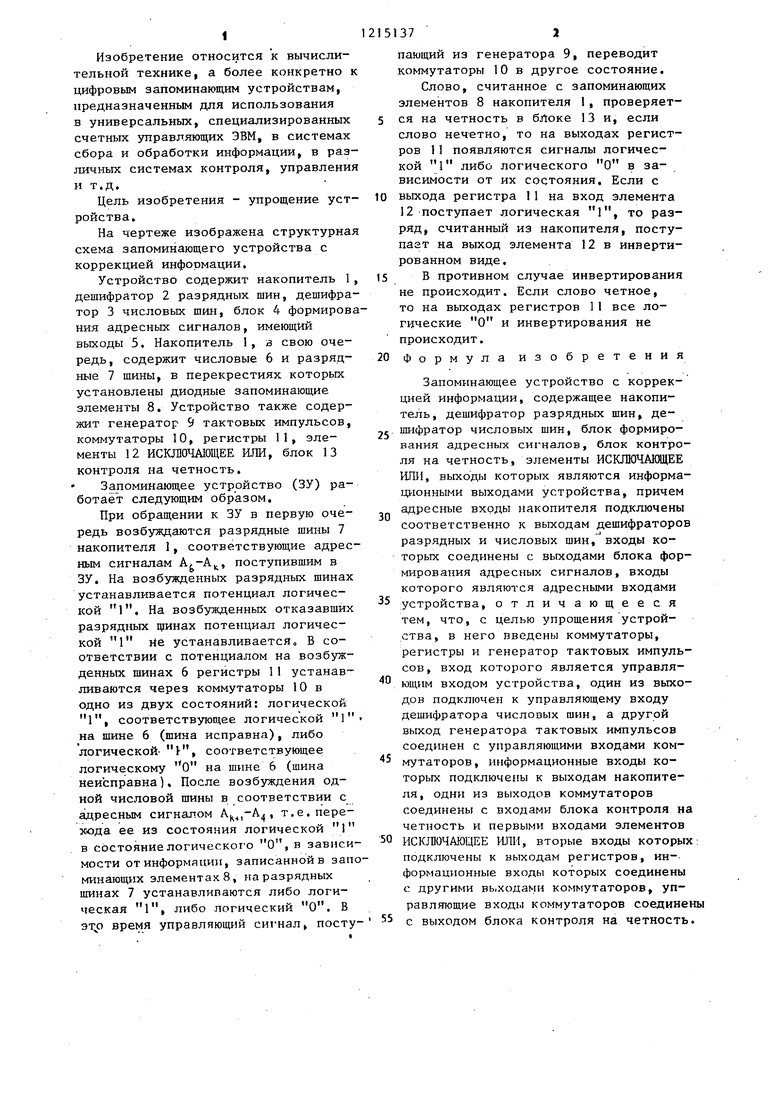

На чертеже изображена структурна схема запоминающего устройства с коррекцией информации.

Устройство содержит накопитель 1 дешифратор 2 разрядных шин, дешифратор 3 числовых шин, блок 4 формировния адресных сигналов, имеющий выходы 5. Накопитель 1, а свою очередь, содержит числовые 6 и разрядные 7 шины, в перекрестиях которых установлены диодные запоминающие элементы 8. Устройство также содержит генератор 9 тактовых импульсов, коммутаторы 10, регистры 11, элементы 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 13 контроля на четность.

Запоминающее устройство (ЗУ) работает следующим образом.

При обращении к ЗУ в первую очередь возбуждаются разрядные шины 7 накопителя 1, соответствующие адресным сигналам , поступившим в ЗУ. На возбужденных разрядных шинах устанавливается потенциал логической 1. На возбужденных отказавших разрядных щинах потенциал логической 1 Не устанавливается, В соответствии с потенциалом на возбужденных шинах 6 регистры 11 устанавливаются через коммутаторы 10 в одно из двух состояний: логической 1, cooтвeтcтвyюD ee логической 1 на шине 6 (шина исправна), либо логической- Ч, соответствующее логическому на шине 6 (шина неисправна К После возбуждения одной числовой шины в соответствии с адресным сигналом А|,-А, т.е. перехода ее из состояния логической 1

в состояние логического О,в зависи мости от информации, записанной в запоминающих элементакв, на разрядных щинах 7 устанавливаются либо логическая 1, либо логический О. В это время управляющий сигнал, посту

10

15

20

25

30

35

40

45

50

55

пающий из генератора 9, переводит коммутаторы 10 в другое состояние. Слово, считанное с запоминающих элементов 8 накопителя 1, проверяется на четность в блоке 13 и, если слово нечетно, то на выходах регистров 11 появляются сигналы логической 1 либо логического О в зависимости от их состояния. Если с выхода регистра 11 на вход элемента 12 поступает логическая 1, то разряд, считанный из накопителя, поступает на выход элемента 12 в инвертированном виде.

В противном случае инвертирования не происходит. Если слово четное, то на выходах регистров 11 все логические О и инвертирования не происходит. Формула изобретения

Запоминающее устройство с коррекцией информации, содержащее накопитель, дешифратор разрядных шин, дешифратор числовых шин, блок формирования адресных сигналов, блок контроля на четность, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых являются информационными выходами устройства, причем адресные входы накопителя подключены соответственно к выходам дешифраторов разрядных и числовых шин,входы которых соединены с выходами блока формирования адресных сигналов, входы которого являются аддресными входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены коммутаторы, регистры и генератор тактовых импульсов, вход которого является управляющим входом устройства, один из выходов подключен к управляющему входу дешифратора числовых шин, а другой выход генератора тактовых импульсов соединен с управляющими входами коммутаторов, информационные входы которых подключены к выходам накопителя, одни из выходов коммутаторов соединены с входами блока контроля на четность и первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых; подключены к ньтходам регистров, ин-. формационные входы которых соединены с другими вь.ходами коммутаторов, управляющие входы коммутаторов соединены с выходом блока контроля на четность.

i - i I - i

АО K fla

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

Изобретение относится к вычислительной технике, а более конкретно - к цифровым запоминающим устройствам, предназначенным для использования в универсальных специализированных и управляющих ЭВМ, в системах сбора и обработки информации, в различных системах контроля, управления и т.д. Цель изобретения - упрощение устройства. Устройство содержит накопитель из числовых и разрядных шин, в перекрестиях которых установлены диодные запоминающие элементы, коммутаторы, регистры, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, 0ЛОК контроля на четность. В устройстве при считывании осуществляется коррекция выходной информации, если искажение последней вызвано неисправностью разрядных шин. 1 ил. О)

| Мак-Вильяме Д., Слоэн Н | |||

| Д | |||

| А | |||

| Теория кодов, исправляющих ошибки | |||

| М.: Связь, 1979, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Электроника, 1981, т | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

Авторы

Даты

1986-02-28—Публикация

1984-06-27—Подача