цифровой преобразователь 1 с выходным сигналом 20, блок 2 памяти вход ных сигналов с сигналами 21 22 на его выходах, регистр 3 сдвига, шину 4 логической 1 с сигналом 23, . двухвходовые сумматоры 5 и 6 с сигналами 24 и 25 на их выходах, генератор 7 тактовых импульсов с сигналом 17 на его выходе, элемент 8 задержки с выходным сигналом 18, блок 9 сравнения с порогом, регист

Изобретение относится к импульсной технике, в частности к устройствам преобразования серий импульсных сигналов, и может быть использовано в различных цифровых измерительных комплексах для выделения повторяющихся импульсных сигналов из смеси с шумами и другими помехами.

Целью изобретения является повышение быстродействия.

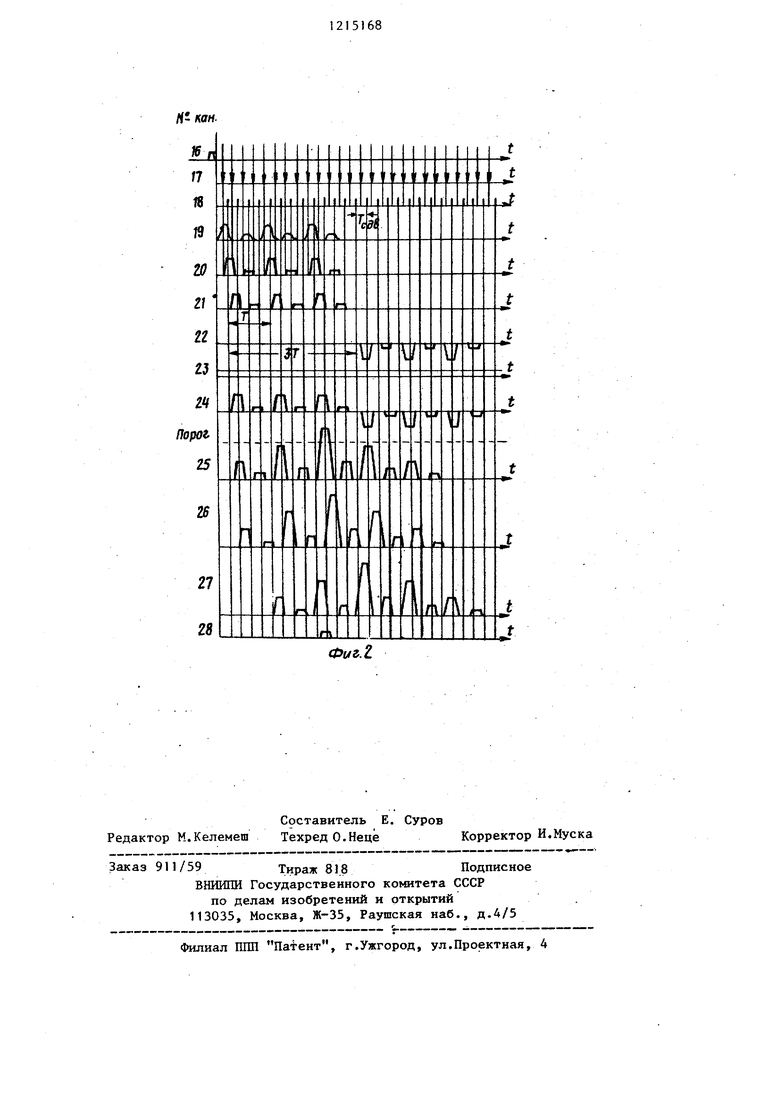

На фиг.1 приведена функциональная схема цифрового накопителя; на фиг.2 - временные диаграммы, поясняющие его работу.

Цифровой накопитель импульсных сигналов содержит аналого-цифровой преобразователь 1, блок 2 памяти входных сигналов, регистры 3 сдвига, шину 4 логической 1, двухвходовые сумматоры 5 и 6, генератор 7 тактовых импульсов, злемент 8 задержки, блок 9 сравнения с порогом, например цифровой компаратор, блок 10 памяти выходных сигналов, регистры 11 сдвига, блок 12 начальной установки, резистор 13, конденсатор 14, инвертор 15.

На фиг.2 введены следую1цие обозначения: 16 - сигнал на выходе блока начальной установки; 17 - тактовая последовательность ни выходе генератора 7 тактовых « мпульсов; 18 - тактовая последовательность на выходе., элемента 8 задержки; 19 - сигнал на накопителя; 20 - сигнал на выходе аналого-цифрового преобразователя; 21 - сигнал на первом вы- xoдe,Jблoкa 2 памяти входных сигналов 22 - сигнал на втором выходе блоры 11 блока 10 памяти выходных сигналов 26 и 27, блок 12 начальной установки с сигналом 16 на его выходе, резистор 13, конденсатор 14 и инвертор 15. На информационный вход аналого-цифрового преобразователя 1, являющегося входом накопителя, подается сигнал 19. Выходной сигнал накопителя - 28. В описании приведены временные диаграммы, пояс- няю11Ц1е работу накопителя. 2 ил.

ка 2 памяти входных сигналов ; 23 - сигнал на шине 4 логической 1, 24 - сигнал на выходе сумматора 5; 25 - сигнал на выходе сумматора 6; 26 - сигнал в первых разрядах регистров 11 сдвига блока 10; 26 - сигнал на выходе блока 10 памяти выходных сигналов; 28 - выходной сигнал накопителя.

Информационный вход аналого-цифрового преобразователя 1 является входом накопителя, его тактовый вход соединен с выходом генератора 7 тактовых импульсов и с входом элемента 8

задержки, а выход - с информационньм входом блока 2 памяти входных сигналов. Регистры 3 сдвига блока 2 памяти имеют по N Мх п+1 разрядов каждый (М - число каналов, п число накапливаемых импульсов). Общее число регистров 3 сдвига составляет m и рдвно разрядности аналого- цифрового преобразователя I. Тактовые входы регистров 3 сдвига объединены и подключены к выходу элемента 8 задержки. Входы начальной установки регистра 3 сдвига объединены и подключены к выходу блока 12 начальной установки.

Первый выход блока 2 памяти входных сигналов, образованный прямыми выходами первых разрядов регистров 3 сдвига, и второй выход блока 2, образованный инверсными выходами последннх разрядов регистров 3 сдвига, соединены соответственно с первьм и вторьм входами (входами первого и второго операндов) сумматора 5. Вход переноса в младшие разряды сумматораi

5 объедниен с (т+1)-м (.знаковым разрядом второго операнда и подключен к шине 4 логической 1, а (т+1)-й (знсчковый) разряд первого операнда подключен к нулевой шине. Такое включение сумматора 5 обеспечивает использование его в ка . честве вычитающего блока, когда первый операнд является положительным числом, а второй операнд - отрицательным числом. Выход сумматора 5 соединен поразрядно (с 1-го по (га+1)-и разряды) с первым входом f-разрядного сумматора 6. В сумматоре 6 старшие разряды первого операнда, начиная с (т+1)-го разряда, объединены, а вход переноса в младший разряд подключен к нулевой шине. Такое включение является естественным (следует непосредственно из правила двоичной арифметики) при суммировании двух операндов, первый из которых знакопеременный и имеет меньшую разрядность, чем второй (т.е. первое слагаемое меньше по абсолютной величине), а второй операнд всегда положителен. Второй вход сумматора подключен поразрядно к выходу блока 10 памяти выходных сигналов образованному прямыми выходами послед них разрядов регистров 11 сдвига, а выход - к информационному входу блока 10 и к первому входу блока 9 сравнения с порогом. Регистры 11 сдвига блока 10 памяти выходньк сигналов имеют по М разрядов каждый, а их общее число составляет f и равно разрядности сумматора 6. Тактовые входы регистров 11 сдвига объединены и подключены к выходу элемента 8 задержки. Входы начальной установки регистров 11 сдвига объединены и подключены к выходу блока 12 начальной установки. В последнем резистор 13 и конденсатор 14 включены последовательно между шиной 4 логической 1 и нулевой шиной, образуя времязадающую цепь, к которой подключен выходной инвертор 15. Разряды второго входа блока 9 сравнения подключены к шине 4 логической 1 и к нулевой шине в соответствии с требуемым значением порога. Выход блока 9 сравнения является выходом накопителя.

Данное устройство выполняет накопление импульсных сигналов в одном (г-м) канале ( элементе дальности и

5168

писледующее сравнение накопленного сигнала с порогом в соответствии с правилом накопления на скользящем интервале

5и-1

М

V ( V

CD

1 0

где n - число накапливаемых импуль- сов (ширина скользящего ин тервала); X - квантованные по амплитуде

и времени значения входного

(П

сигнала, задержанные на г тактов;

у - квантованные по амплитуде

и времени значения выходного сигнала;

с - цифровой порог.

Для пояснения принципа работы накопителя применяем правило накопления на скользящем интервале в г-м канале. Запишем выражение или k-ro и (k-l)-ro периодов работы:

V.-1

,,(«) Sr() +

УК «.-И--- K-h+t K.-h-ft- .

--°(г)

I

,- .,). у-),(. 1 -x - - х )

30 ,YK-I 2 .-1- ( к-1 . -г K-hH-i ;-hСЗ)

Вычитая у

(h

К-1

t.) из у и переноса

у в правую часть, получим посЛе приведения подобных членов рекурент- ное правило работы накопителя в г-м

канале

t) (

к-М

+ -У

г)

к(4)

Принцип работы накопителя в соответствии с выражением ) поясняется на примере его функционирования при конкретных значениях числа каналов и числа накапливаемых импульсов

. Указанному примеру соответствуют и временные диаграммы на фнг.2, причем на временных диаграммах значения сигналов на всех ннформацион- HfK цифровых многоразрядных входах и выходах (двоичные многоразрядные числа) представлены условно в виде импульсов с амплитудой, пропорциональной величине соответствующих сигналов. Для определенности временные диаграммы приведены для случая, когда на входе накопителя действует сигнал, соответствующий наличию трех импульсов в первом и третьем каналах, причем амплитуды импульсов в каждом из каналов составляют соответственно три и одну условную единицы.

После включения питания накопитель автоматически приводится в исходное положение, при котором регистры 3 и 11 сдвига блоков 2 и 10 памяти сброшены в нулевые состояния. Сиг нал сброса вырабатьгоается блоком 12 начальной установки следующим образом.

Конденсатор 14 блока 12 до включения питания разряжен. В момент вклю- чения питания напряжение на конденсаторе не изменяется скачком, поэтому на входе инвертора 15 оказьша- ется уровень логического О, а на его выходе - уровень логической 1. По мере заряда конденсатора 14 через резистор 13 напряжение на конденсаторе растет и через время, определяемое постоянной времени заряда время- задающий цепи, достигает уровня, при котором инвертор переходит из единичного в нулевое состояние. В результате на выходе блока 12 начальной установки оказьшается сформированным положительный импульс (16 на фнг,2), который поступает на входу начальной установки регистров 3 и 11 сдвига и устанавливает их в нулевое состояние.

Входной сигнал ( 1 9 на фиг.2 по- ступает на информационный в:.од аналого-цифрового преобразователя 1, на тактовьп вход которого поступают импульсы с выхода генератора 7 тактовых импульсов ( 1 7 на фиг. 2) с .пери

одом, равньм длительности накапливаемых импульсов. Проквантованный по амплитуде и времени сигнал .20 фиг.2), представленный двоичным wi-разрядным кодом, с выхода аналого- цифрового преобразователя I поступает поразрядно в регистры 3 сдвига блока 2 памяти входных сигналов, на тактовые входы которых с выхода элемента 8 задержки, поступает после- довательность импульсов сдвига (18

Т Т на фиг.2) с периодом T.e -:j Т

определяющим время обработки одного канала (.Т - период следования вход- ных импульсов в каждом из каналов). Отсчеты входного сигнала, от- носяшиеся к смежным каналам, оказы

ваются всегда в смежных разрядах регистров 3 сдвига и последовательно продвигаются в них. Так как число разрядов регистров 3 сдвига составляет N М « п+1 13, то полностью хранится информация о входном сигнале в п (трех)предыдущих периодах всех М (четырех) каналов и очередное значение обрабатываемого канала.

Как видно из изложенного, в первом и последнем разрядах регистров 3 сдвига находится информация, относящаяся к одному и тому же обрабатываемому в данном такте каналу,причем в первых разрядах это xi , а в последних раз I Ь1 / л I

Указанные

рядах - , х Д

j

5

0

5

значения входного сигнала поступают одновременно в сумматор 5, причем xj - в прямом коде, а в обратном коде (21 и 22 на фиг.2, так как х,. подается с инверсных выходов последних разрядов регист- . ров 3 сдвига. Обратный код числа X . вместе с сигналом логической 1, подаваемой в сумматор 5 с шины 4 логической 1 (23 на фиг.2), образует дополнительный код числа хУ так, что на выходе сумматора 5 оказьшается число, равное разности х1Г - - С24- ти X ц к-h к к,-з

фиг.2). Это число поступает в сумматор 6, на второй вход которого одновременно подается предыдущее значение выходного накопленного сигнала обрабатЕлваемого канала У, -У. с выходов последних разрядов регистров 11 сдвига блока 10 памяти ( 27 на фиг.2. После суммирования на выходе сумматора 6 образуется положительное число, представляющее накопленное значение выходного

сигнала обрабатьшаемого канала

(11 Уц , которое поступает на вход

блока 9 сравнения с порогом и на входы регистров 11 блока 10 памяти выходных сигналов. Значение сравнивается с порогом, величина кото-, рого в виде двоичного числа постоянно действует на втором входе блока 9 ( 25 на фиг.2). При превышении вы- ходньм сигналом у, порога на выходе накопителя появляется нормированный по амплитуде импульс, лаличие которого свидетельствует об обнаружении накопленного сигнала в данном канале (28 на фиг.2). При поступлении очередного импульса сдвига чис

(-11

ло у j записьшается в первые разряды регистров 11 сдвига блока 10 памяти (26 на фиг.2), очередное значение входного сигнала записьшается в первые разряды регистров 3 сдви га блока 2 памяти, вся информация в регистрах 3 и II сдвигается на один разряд, и накопитель пе- реходит к обработке второго канала. Ровно через четыре такта сдвига, т.е. через время Т, равное периоду следования импульсов, когда накопитель вновь будет обрабатьюать первый канал в (k+l)-M такте , число окажется в последних разрядах регистров П сдвига, так как число разрядов регистров 11 равно числу каналов .

В процессе накопления п импульсов в смежных периодах накопленный сигна может оказаться в п раз больше входного сигнала, поэтому разрядность чисел для его представления должна быть на log п ( обозначе- ние ближайшего целого числа, больше- го или равного самому числу боль- те разрядности входного числа, чтобы исключить возможность переполнения разрядной сетки. Это достигается выбором числа регистров 1I сдвига, равным Г m J log г riT и соответствующей разрядностью сумматора 6.

Формула изобретения

Цифровой накопитель импульсных сигналов, содержащий аналого-цифровой преобразователь, информационный вход которого является входом нако пителя, тактовый вход соединен с выходом генератора тактовых импульсов , а выход - с ииформационным вхо дом блока памяти входных сигналов, состоящего из « регистров сдвига с объединенньми тактовьми входами, образующими тактовый вход блока, и

блок сравнения с порогом, выход которого является выходом накопителя,

ю 15. 0

S : ; о

5

0

5

0

отличающийся тем, что, с целью повьиаения быстродействия, в него введены первый сумматор, второй сумматор, блок начальной установки, элемент задержки и блок памяти ьыходных сигналов, состоящий из Р -разрядных регистров сдвига с об- единенньми тактовыми входами и входами начальной установки, образующими соответственно тактовый вход и вход начальной установки блока, где М- число каналов , - число накапливаемых импульсов, 3 - ближайшее число, большее или равное fog i.h , при этом регистры сдвига блока памяти входных сигналов выполнены М х h 1 разрядными, а их входы начальной установки объединены и образз т вход начальной установки блока, а первый и второй его выходы, образованные соответственно прямыми и инверсными выходами первых и последних разрядов регистров сдвига, подключены соответственно к первому и второму входам первого сумматора, вход переноса младшего разряда которого подключен к шине логической 1, а выход - к первому входу второго сумг- матора, второй вход которого соединен с выходом блока памяти выходных сигналов, образованньм прямыми выходами последних разрядов регистров сдвига блока, инфо ационный его вход соединен с входом блока сравнения с порогом и с выходом второго сумматора, тактовые входы блоков памяти входных и выходных сигналов подключены к генератору тактовых импульсов через элемент задержки, а вход начальной установки блоков Памяти входных и выходных сигналов - к выходу блока начальной установки, вход которого соединен с шиной логической 1, причем разряды порогового сигналы блока сравнения с порогом подключены к ига- не логической 1 н иулевой пине.

фуг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Логическое запоминающее устройство | 1986 |

|

SU1451772A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

Изобретение относится к импульсной технике и может быть использова- и но в различных цифровых измерительных комплексах для вццелення повторяющихся импульсных сигналов из смеси с шумами и другими помехами. Цель и изобретения - повышение быстродейст- : ВИЯ. Устройство содержит аналогоW

| Лихарев В.А | |||

| Цифровые методы устройства в радиолокации | |||

| М.: Советское радио, 1973, с | |||

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лезии Ю.С | |||

| Оптимальные фильтры накопители импульсных сигналов | |||

| М, Советское радио, 1969, рис, 12.3.1 | |||

| с | |||

| РУЧКА С РЕЗЕРВУАРОМ ДЛЯ ЧЕРНИЛ | 1922 |

|

SU402A1 |

Авторы

Даты

1986-02-28—Публикация

1984-07-05—Подача