1

Изобретение относится к вычислительной технике и автоматике и ъюжет быть использовано для контрол многовыходных схем.

Целью изобретения является повышение достоверности контроля.

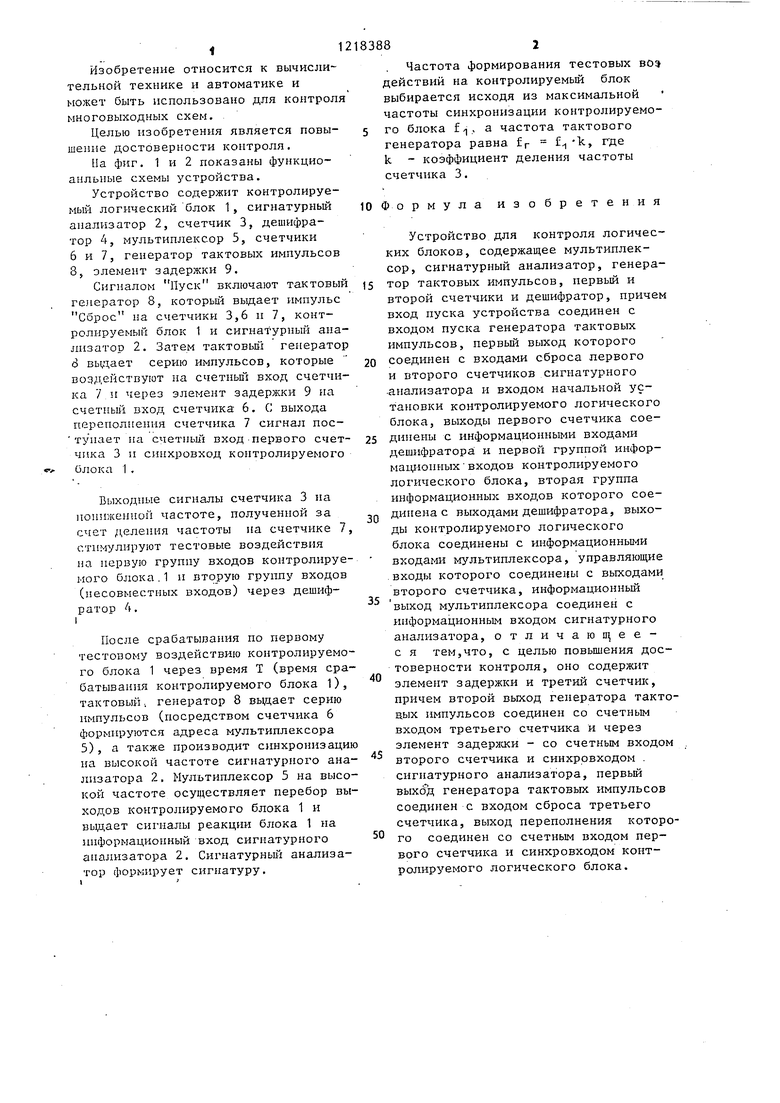

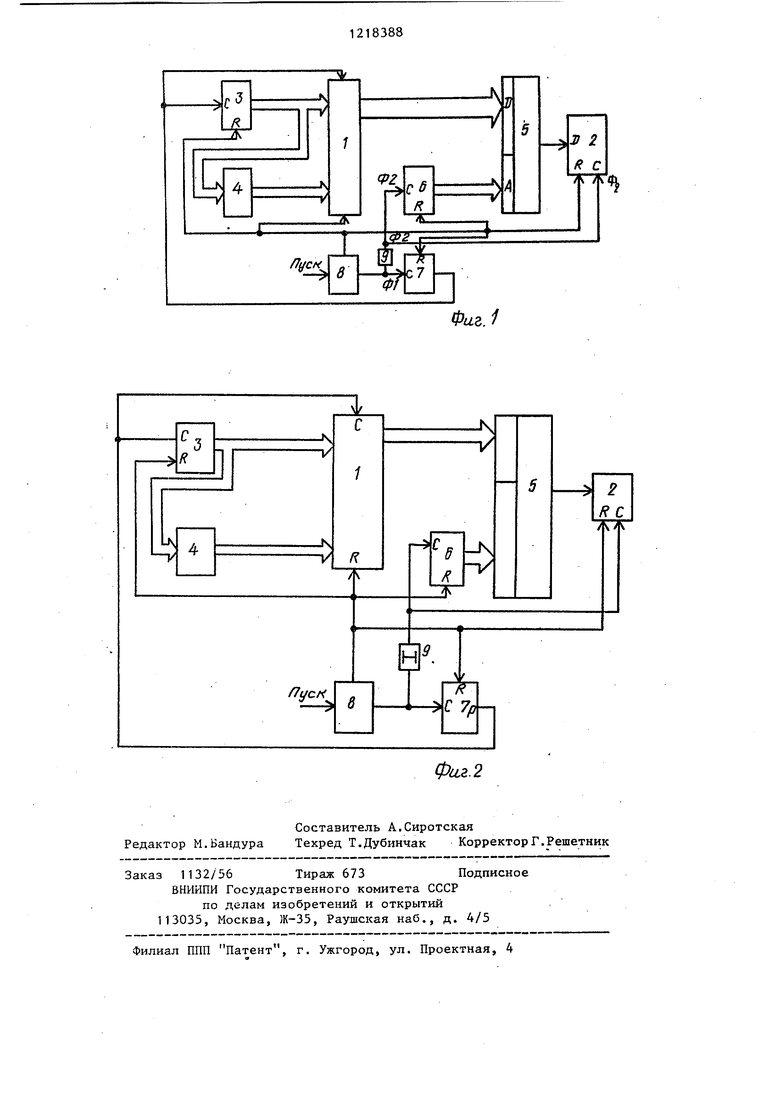

Па фиг. 1 и 2 показаны функцио- анльные схемы устройства.

Устройство содержит контролируемый логический блок 1, сигнатурный анал11затор 2, счетчик 3, дешифратор 4, мультиплексор 5, счетчики 6 и 7, генератор тактовых импульсов 8, элемент задержки 9.

Сигналом Пуск включают тактовы генератор 8, которьш выдает импульс Сброс на счетчики 3,6 и 7, контролируемый блок 1 и сигнатурньш анализатор 2. Затем тактовьш генерато 8 вьщает серию импульсов, которые воздействуют на счетньш вход счетчика 7 и через элемент задержки 9 на счетньй вход счетчика 6. С выхода переполнения счетчика 7 сигнал пос- тупает на счетный вход-первого счетчика 3 и синхровход контролируемого блока 1,

Выходные сигналы счетчика 3 на пониженной частоте, полученной за счет деления частоты на счетчике 7, стимулируют тестовые воздействия на первую группу входов контролируемого блока.1 и вторую группу входов (несовместных входов) через дешифратор 4. I

После срабатывания по первому тестовому воздействию контролируемого блока 1 через время Т (время срабатывания контролируемого блока 1), тактовый; генератор 8 выдает серию импульсов (посредством счетчика 6 формируются адреса мультиплексора 5), а также производит синхронизацию на высокой частоте сигнатурного анализатора 2. Мультиплексор 5 па высокой частоте осуществляет перебор выходов контролируемого блока 1 и вы/дает сигналы реакции блока 1 на информационный вход сигнатурного анализатора 2. Сигнатурный анализатор формирует сигнатуру.

Частота формирования тестовых воа действий на контролируемьм блок выбирается исходя из максимальной частоты синхронизации контролируемо- го блока f/j , а частота тактового генератора равна fp где k - коэффициент деления частоты счетчика 3.

Ф о рмула изобретения

Устройство для контроля логических блоков, содержащее мультиплексор, сигнатурный анализатор, генератор тактовых импульсов, первый и второй счетчики и дешифратор, причем вход пуска устройства соединен с входом пуска генератора тактовых импульсов, первый выход которого соединен с входами сброса первого и второго счетчиков сигпатурного анализатора и входом начальной установки контролируемого логического блока, выходы первого счетчика соединены с информационными входами дешифратора: и первой группой инфор- мац1-юнных входов контролируемого логического блока, вторая группа информационных входов которого соединена с выходами дешифратора, выходы контролируемого логического блока соединены с информационными входами мультиплексора, управляющие входы которого соединены с выходами второго счетчика, информационный выход мультиплексора соединен с информационным входом сигнатурного анализатора, отличаюп ее- с я тем,что, с целью повышения достоверности контроля, оно содержит элемент задержки и третий счетчик, причем второй выход генератора такто- цых импульсов соединен со счетным входом третьего счетчика и через элемент задерлоси - со счетным входом второго счетчика и синхррвходом . сигнатурного анализатора, первьм выход генератора тактовых импульсов соединен с входом сброса третьего счетчика, выход переполнения которого соединен со счетным входом первого счетчика и синхровходом контролируемого логического блока.

Составитель А,Сиротская Редактор М.Бандура Техред Т.Дубинчак Корректор Г.Решетник

Заказ 1132/56 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Фи,г.1

Фаг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1307459A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1381509A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

Изобретение относится к области вычислительной техники и автоматики и может быть использовано для контроля многовыходных схем. Цель изобретения - повышение достоверности контроля. Устройство содержит три счетчика, дешифратор, генератор тактовых импульсов, мультиплексор и сигнатурный анализатор. Счетчик и дешифратор используются в качестве генератора тестов. Другой счетчик используется для формирования адресов мультиплексора, вьпсодной сигнал которого обрабатьшается сигнатурным анализатором. В устройстве учитьшается цепь срабатывания контролируемого логического блока, и в течение одного тестового набора происходит многократный опрос одних и тех же выходов контролируемого логического блока. 1 ил. Л В ьо оо :СО 00 с

| Устройство для контроля логических блоков | 1979 |

|

SU792256A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-08-13—Подача