рехода и условного перехода, накапливающий сумматор 5 и третий элемент И 8, Вход и выход шифратора 14 соединены с выходом блока 3 памяти команд и установочным входом триггера 12. Первый и второй входы сброса и выход триггера 12 подключены к синхровходу устройства, первому выходу шифратора 15 и входу сброса триггера 9 записи и установочному входу триггера 10 чтения. Установочный вход, синхро- вход, счетный вход, вход вычитания, информационный вход, информационный выход и выход переноса сумматора 5 соединены с первым адресным входом и синхровходом устройства, выходом

1

Изобретение относится к цифровой вычислительной технике и может быть использовано в блоках предварительной выборки, команд ЭВМ, к которым предъявляются высокие требования по быстродействию, аппаратурным затратам и энергопотреблению.

Цель изобретения - повьшгение быстродействия устройства.

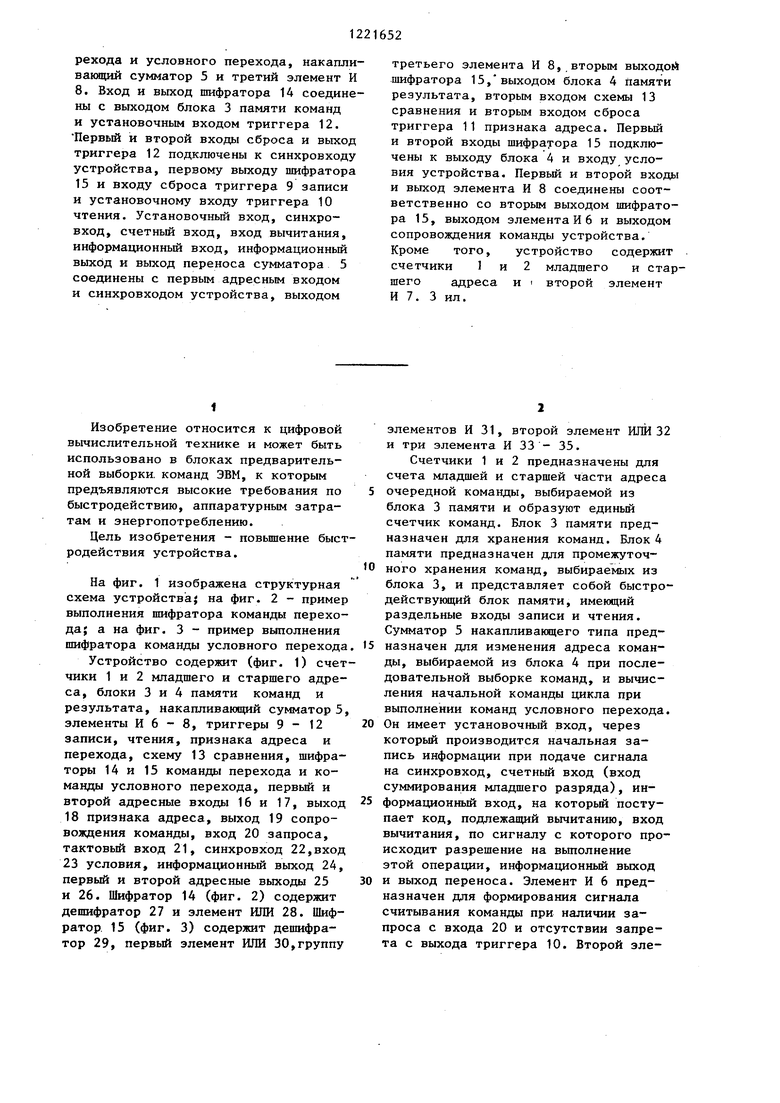

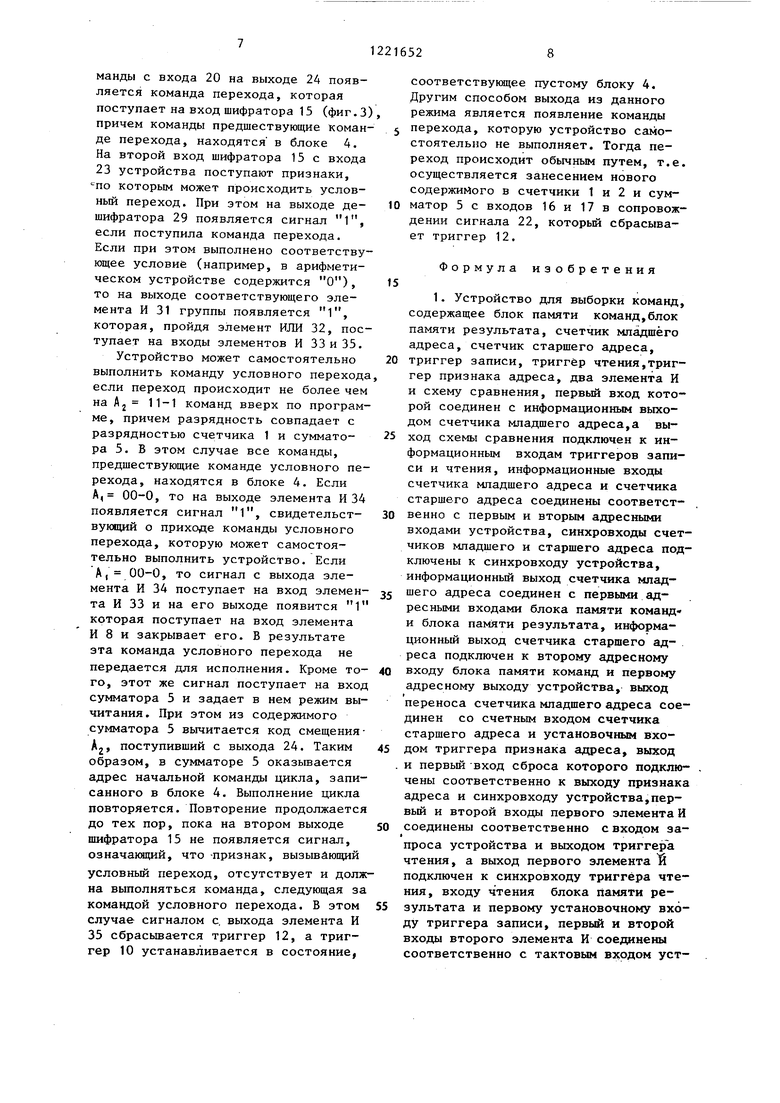

На фиг. 1 изображена структурная схема устройства} на фиг. 2 - пример выполнения пшфратора команды перехода; а на фиг. 3 - пример выполнения шифратора команды условного перехода

Устройство содержит (фиг. 1) счетчики 1 и 2 младшего и старшего адреса, блоки 3 и 4 памяти команд и результата, накапливающий сумматор 5, элементы И 6 - 8, триггеры 9-12 записи, чтения, признака адреса и перехода, схему 13 сравнения, шифраторы 14 и 15 команды перехода и команды условного перехода, первый и второй адресные входы 16 и 17, выход 18 признака адреса, выход 19 сопровождения команды, вход 20 запроса, тактовый вход 21, синхровход 22,вход 23 условия, информационный выход 24, первый и второй адресные выходы 25 и 26. Шифратор 14 (фиг. 2) содержит дешифратор 27 и элемент ИЛИ 28. Шифратор 15 (фиг. 3) содержит дешифратор 29, первый элемент ИЛИ 30,группу

третьего элемента И 8, вторым выходов шифратора 15, выходом блока 4 памяти результата, вторым входом схемы 13 сравнения и вторым входом сброса триггера 11 признака адреса. Первый и второй входы шифратора 15 подключены к выходу блока 4 и входу условия устройства. Первый и второй входы и выход элемента И 8 соединены соответственно со вторым выходом шифратора 15, выходом элемента И 6 и выходом сопровождения команды устройства. Кроме того, устройство содержит счетчики 1 и 2 младшего и старшего адреса и второй элемент И 7. 3 ил.

элементов И 31, второй элемент ИЛИ 32 и три элемента И 33- 35.

Счетчики 1 и 2 предназначены для счета младшей и старшей части адреса очередной команды, выбираемой из блока 3 памяти и образуют единый счетчик команд. Блок 3 памяти предназначен для хранения команд. Блок 4 памяти предназначен для промежуточного хранения команд, выбираемых из блока 3, и представляет собой быстро- действукмций блок памяти, имеющий раздельные входы записи и чтения. Сумматор 5 накапливакнцего типа пред- назначен для изменения адреса команды, выбираемой из блока 4 при последовательной выборке команд, и вычисления начальной команды цикла при выполнении команд условного перехода. Он имеет установочный вход, через который производится начальная запись информации при подаче сигнала на синхровход, счетный вход (вход суммирования младшего разряда), ин- формационный вход, на который поступает код, подлежащий вычитанию, вход вычитания, по сигналу с которого происходит разрешение на вьтолнение этой операции, информационный выход и выход переноса. Элемент И 6 предназначен для формирования сигнала считывания команды при наличии запроса с входа 20 и отсутствии запрета с выхода триггера 10. Второй элемент И 7 предназначен для формирования сигналов записи в блок 4 при наличии тактового сигнала со входа 21 и разрешения с выходов триггеров

9и 11. Третий элемент И 8 предназначен для запрета выдачи сигнала сопровождения команды на выход 19 при выполнении команд условного перехода исполняемых самим устройством для выборки команд.

Триггер 9 предназначен для вьщачи сигнала Запрет записи, если в блоке 4 нет свободного места. Триггер

10предназначен для вьщачи сигнала Запрет чтения, если блок 4 пуст. Триггер 11 предназначен для выдачи сигнала на выход 18, если адрес записи в блок 4 на сумматоре 5 оказался больше адреса на счетчике 1. Триггер 12 предназначен для вьщачи сигнала при наличии в блоке 4 команды перехода. Схема 13 сравнения предназначена для вьщачи сигнала при совпадении кодов на выходах счетчика 1

и сумматора 5. Шифратор 14 предназначен для вьщачи сигнала при записи в блок 4 команды перехода. Шифратор 15 при появлении на выходе 24 команды условного перехода вырабатывает сигнал на первом выходе, если услови с входа 23 выполнены и переход необходим, и на втором выходе, приводя в исходное состояние, если выполняется следующая команда. Единичные сигналы на выходах элементов И 3 группы свидетельствуют о том, что условия данной команды условного перехода выполнены, т.е. переход необходим. Сигнал на выходе элемента 34 равен ,1, когда А, 00-0, т.е. устройство в перехода.

состоянии выполнить команду

Входы 16 и 17 используются для занесения адреса команды в счетчики 1 и 2 и сумматор 5 в начале работы и при выполнении команд переходов. Занесение адреса сопровождается синхросигналом с входа 22, приводящим в исходное состояние триггеры 9-11. На вход 20 поступают запросы на очередную команду, которые прекращаются после вьщачи сигнала с выхода 19, свидетельствующего о готовности команды на выходе 24. На вход 21 поступает последовательность импульсов от генератора, период которых равен циклу обращения .к памяти. Предпола- гается, что сигналы на входах 20 и

10

20

25

221652

21 сдвинуты относительно друг друга. На выходы 25 и 26 поступает адрес выполняемой команды. Причем если на выходе 18 имеется сигнал 1, то код 5 на выходе 25 должен уменьшаться на 1 для получения действительного значения адреса. На вход 23 из арифметического устройства поступают признаки, по которым может происходить условный переход.

Устройство работает следукицим образом.

В блоке 3 памяти находятся команды, подлежащие выполнению. Уст-- )5 ройство приходит в исходное состояние при подаче на входы 16 и 17 адреса начальной команды, сопровождаемой синхросигналом с входа 22. При этом старшие разряды адресакоманды записываются в счетчик 2, а младщие - в счетчик 1 и сумматор 5. Кроме того, сигнал с выхода 22 устанавливает триггер 9 в состояние 1, а триггеры 10 и 11 - в состояние О. Сигнал с выхода триггера 11 поступает на выход 18 и свидетельствует о том, что код на выходе сумматора 5 не больше кода на выходе счетчика 1. Сигналы запроса с входа 20 не проходят через элемент И 6 и не удовлетворяются, так как блок 4 пуст. Сигнал с входа 21 (от генератора импульсов), пройдя через элемент И 7, поступает на вход чтения и обеспечивает считывание команды из блока 3 по адресу, хранящемуся в счетчиках 1 и 2, и по заднему фронту, поступив на вход записи блока 4, записывает эту команду по адресу, находящемуся в счетчике 1. Кроме того, сигнал с выхода элемента И 7 увеличивает на 1 содержимое счетчика 1, подготавливая адрес следующей команды,- а также устанавливает в 1 триггер 10, разрешая чтение из блока 4. Если после окончания очередного чтения из блока 3 оказывается, что код в счетчике 1 совпадает с кодом в сумматоре 5, то блок 4 полностью занят. Задний фронт сигнаша с выхода элемента И 7 поступает на синхробход триггера 9, и, поскольку на выходе схемы 13 присутствует сигнал 1, триггер 9 установится в состояние О и закрывает элемент И 7. Заполнение

30

35

40

45

50

55

блока 4 прекращается.

Если блок 4 не пуст, то запрос на команду, пройдя через элемент И 6,

поступает на вход чтения блока 4, в результате на выход 24 считается команда, хранящаяся по адресу на выходе сумматора 5, а на выход 19 пос- тупает сброс выдачи. Сигнал с выхода элемента И 6 прибавляет 1 к содержимому сумматора 5, и, сбросив триггер 9, разрешает считьшание из блока 3. Если при чтении из блока 4 происходит совпадение кодов на выходах счетчика 1 и сумматора 5, то блок 4 полностью выбран. При этом по заднему фронту сигнала с выхода элемента И 6 триггер 10 переводится в состояние О, элемент И 6 закрыт, а чтение команд запрещено. В результате триггер 9 сбрасьтается первой командой чтения из блока 4, а триггер 10 - первой командой записи в блок 4.

Если блок 4 не пуст, то запрос на команду, пройдя через элемент И 6, поступает на вход чтения блока 4,что обеспечивает считывание команды, хранящейся по адресу на выходе сумматора 5, на выход 24 и поступление на выход 19Утроба выдачи. Сигнал с выхода элемента И 6 прибавляет 1 к содержимому сумматора 5, и, сброси триггер 9, разрешает чтение из блока 3. Если при чтении из блока 4 происходит совпадение кодов на выходах счетчика 1 и сумматора 5, то блок 4 полностью выбран. При этом по заднему фронту сигнала с выхода элемента И 6 триггер 10 переводится в состояние О, а элемент И 6 закрыт, т.е. чтение команд запрещено. В результате триггер 9 сбрасывается пер- вой командой чтения из блока 4, а триггер 10 сбрасывается первой командой записи в блок 4.

Рассмотрим процедуру изменения адресов в счетчиках 1 и 2 и сумматоре 5. В исходном состоянии в счетчик 1 и сумматор 5 заносится один и тот же код и сумматор 5 вьшолняет функцию Счета младшей части адреса следующей команды. Поскольку чтение из ячейки блока 4 происходит только после записи информации в нее, то адрес записи в счетчике 1 больше адреса чтения в сумматоре 5. В этом случае адрес очередной команды, подлежащей выполнению, получается на выходах 25 и 26, т.е. старшие разряды адреса поступают со счетчика 2, а младшие 5

j O 5 0

с сумматора 5. Однако если счетчик. 2 обнулен (00-0) и в некоторый момент произошла запись в блок 4 по последнему адресу 11-1 (содержимое счетчика 1), а чтение должно происходить из ячейки с адресом--11-0, тогда следующий импульс с выхода элемента И 7 обнуляет счетчик 1, сигнал переноса которого прибавит 1 к содержимому счетчика 2 (0-01) и устанавливает в единичное состояние триггер 11. В этом случае код на выходе счетчика 1 оказывается меньше кода на выходе сум- / матора 5 и для получения действительного адреса следующей команды 11-0 необходимо вычесть 1 из кода в счетчике 2 (выход 25), о чем свидетельствует сигнал 1 на выходе 18. Поскольку адрес следующей команды необходим для выполнения команды перехода относительно текущего адреса команды, то формирование нового адреса происходит в арифметико-логическом блоке путем суммирования текущего адреса со смещением. В связи с этим вычитание указанной 1 не вызывает трудностей. Когда в приведенном примере происходит переполнение сумматора 5, то сигнал переноса сбрасывает триггер 11, на выходе 19 оказьшается О и, следовательно, код на выходах 25 и 26 соответствует адресу очередной команды.

Рассмотрим работу устройства при выполнении команды условного перехода. Пусть с выхода блока 3 на вход шифратора 14 поступает команда условного перехода. Формат команды представлен на фиг. 2 и содержит код операции (КОП) и смещение относительно текущего адреса Д, и А. В системе команд ЭВМ может быть несколько команд условного и безусловного перехода (по нулю сумматора, переполнению и т.п.). Если дешифратор 27, проанализировав код операции, выявляет одну из команд перехода, то на выходе элемента ИЛИ 28 появляется 1. Сигнал с выхода шифратора 14 устанавливает в единичное состояние триггер 12, который переводит триггеры 9 и 10 в состояние, соответствующее полному заполнению блока 4 и удерживает их в этом состоянии. В результате запись в блок 4 запрещена (элемент И 6 закрыт), а чтение раз- :решено. После очередного запроса команды с входа 20 на выходе 24 появляется команда перехода, которая поступает на вход шифратора 15 (фиг. 3) причем команды предшествующие коман- де перехода, находятся в блоке 4. На второй вход шифратора 15 с входа 23 устройства поступают признаки, которым может происходить условный переход. При этом на выходе де- шифратора 29 появляется сигнал 1, если поступила команда перехода. Если при этом выполнено соответствующее условие (например, в арифметическом устройстве содержится О), то на выходе соответствующего элемента И 31 группы появляется 1, которая, пройдя элемент ИЛИ 32, поступает на входы элементов И 33 и 35.

Устройство может самостоятельно выполнить команду условного перехода если переход происходит не более чем на Aj 11-1 команд вверх по программе, причем разрядность совпадает с разрядностью счетчика 1 и суммато- ра 5. В этом случае все команды, предшествующие команде условного перехода, находятся в блоке 4. Если А, 00-0, то на выходе элемента И 34 появляется сигнал 1, свидетельст- вующий о приходе команды условного перехода, которую может самостоятельно выполнить устройство. Если А, 00-0, то сигнал с выхода элемента И 34 поступает на вход элемен- та И 33 и на его выходе появится 1 которая поступает на вход элемента И 8 и закрывает его. В результате эта команда условного перехода не передается для исполнения. Кроме то- го, этот же сигнал поступает на вход сумматора 5 и задает в нем режим вычитания. При этом из содержимого сумматора 5 вычитается код смещения А, поступивший с выхода 24. Таким образом, в сумматоре 5 оказывается адрес начальной команды цикла, записанного в блоке 4. Выполнение цикла повторяется. Повторение продолжается до тех пор, пока на втором выходе шифратора 15 не появляется сигнал, означакмций, что -признак, вызьшАющий условный переход, отсутствует и должна выполняться команда, следующая за командой условного перехода. В этом случае сигналом с. выхода элемента И 35 сбрасьтается триггер 12, а триггер 10 устанавливается в состояние,

соответствукицее пустому блоку 4. Другим способом выхода из данного режима является появление команды перехода, которую устройство самостоятельно не выполняет. Тогда переход происходит обычным путем, т.е. осуществляется занесением нового содержимого в счетчики 1 и 2 и сумматор 5 с входов 16 и 17 в сопровождении сигнала 22, который сбрасывает триггер 12.

Формула изобретения

1. Устройство для выборки команд, содержащее блок памяти команд,блок памяти результата, счетчик младшего адреса, счетчик старшего адреса, триггер записи, триггер чтения,триггер признака адреса, два элемента И и схему сравнения, первый вход которой соединен с информационным выходом счетчика младшего адреса,а выход схемы сравнения подключен к информационным входам триггеров записи и чтения, информационные входы счетчика младшего адреса и счетчика старшего адреса соединены соответственно с первым и вторым адресныьш входами устройства, синхровходы счетчиков младшего и старшего адреса подключены к синхровходу устройства, информационный выход счетчика младшего адреса соединен с первыми адресными входами блока памяти команд и блока памяти результата, информационный выход счетчика старшего адреса подключен к второму адресному входу блока памяти команд и первому

адресному выходу устройства, выход I

переноса счетчика младшего адреса соединен со счетным входом счетчика старшего адреса и установочным входом триггера признака адреса, выход и первый вход сброса которого подключены соответственно к выходу признак адреса и синхровходу устройства,первый и второй входы первого элемента И соединены соответственно с входом за проса устройства и выходом триггера чтения, а выход первого элемента 1Й подключен к синхровходу триггера чтения, входу чтения блока памяти результата и первому установочному входу триггера записи, первый и второй входы второго элемента И соединены соответственно с тактовым входом устройства и выходом триггера записи, а выход второго элемента И подключен к входу записи блока памяти результата, входу чтения блока памяти команд, синхровходу триггера записи, первому входу сброса триггера чтения и счетному входу счетчика младшего адреса, второй установочный вход триггера записи и второй вход сброса триггера чтения соединены с синхровходом устройства, а информационньй вход и выход блока памяти результата подключены соответственно к выходу блока памяти команд и информационному вы- ходу устройства, отл.ичающее- с я тем, что, с целью повышения быстродействия, оно содержит шифратор команды перехода, шифратор команды условного перехода, триггер перехода третий элемент И и накапливающий сумматор, установочный вход, синхровход счетный вход, вход вычитания, информационный вход, информационный выход и выход переноса которого соединены соответственно с первым адресным входом и синхровходом устройства, выходом первого элемента И, первым выходом шифратора команды условного перехода,выходом блока памяти резуль- тата, вторым входом схемы сравнения и вторым входом сброса триггера признака адреса, кроме того, информационный выход накапливаиицего сумматора подключен к второму адресному входу.. блока памяти результата и второму адресному выходу устройства, вход и выход шифратора команды перехода соединены соответственно с выходом блока памяти команд и установочным входом триггера перехода, первый и второй входы Сброса которого подключены соответственно к синхровходу устройства и второму выходу шифратора команды условного перехода, ко- торый соединен с третьим входом сброса триггера чтения, выход триггера

перехода подключен к входу сброса . триггера записи и установочному входу триггера чтения, первый и второй входы шифратора команды условного перехода соединены соответственно с выходом блока памяти результата и входом условия устройства, а первый и второй входы и выход третьего элемента И подключены соответственно к первому выходу шифратора команды условного перехода, выходу первого элемента И и выходу сопровождения команды устройства.

2.Устройство по п. 1, отличающееся тем, что, шифратор команды перехода содержит дешифратор и элемент ИЛИ, вход и выход которого соединены соответственно с выходом дешифратора и выходом шифратора, а вход дешифратора подключен к входу шифратора.

3.Устройство по п. 1, отличающееся тем, что шифратор команды условного перехода содержит дешифратор, два элемента ИЛИ, три элемента И и группу элементов И,первые входы которых соединены с соответствующими выходами дешифратора и входами первого элемента ИЛИ, вход дешифратора подключен к первому входу шифратора, вторые входы и выходы элементов И группы соединены соответственно с вторым входом шифратора и входами второго элемента ИЛИ, выход, первый и второй входы первого элемента И подключены соответственно к первому выходу шифратора, выходу второго элемента ШШ и выходу второго элемента И, входы которого соединены с первым входом шифратора, а первый и второй входы и выход третьего элемента И подключены соответственно к выходам первого и второго элементов ИЛИ и второму выходу шифратора.

23фиг.З

Составитель Г.Виталиев Редактор Н.Воловик Техред В. Кадар

1613/54 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий t13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г, Ужгород, ул. Проектная, 4

Корректор Л. Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для контроля хода программы управляющей вычислительной машины | 1990 |

|

SU1815644A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

Изобретение относится к устройствам для предварительной выборки команд ЭВМ, к которым предъявляются высокие требования по быстродействию, аппаратурным затратам и энергопотреблению. Цель изобретения - повышение быстродействия устройства. Для этого в устройство введены триггер 12 перехода, шифраторы 14 и 15 команды пе25 X . W гз О) iptjt.l

| Королев Л.Н | |||

| Структуры ЭВМ и их математическое обеспечение | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Шкив для канатной передачи | 1920 |

|

SU109A1 |

| Устройство для выборки команд | 1984 |

|

SU1149257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-10—Подача